用户代码移植到STM32芯片时发生非对齐错误怎么办

描述

为什么基于Cortex-M3/M4的STM32芯片组织的用户代码移植到基于Cortex-M0/M0+的STM32芯片时为何可能会发生非对齐错误?

这是因为基于Cortex-M3/M4的STM32芯片对数据访问的对齐要求不那么严格,即使非对齐访问也可以支持,当然可能会牺牲访问效率。而对于Cortex-M0/M0+的芯片则明确不支持对数据的非对齐访问。显然,我们设计代码时尽量遵循对齐访问便于移植。

因为内核的差异导致我们在应用上的误解或误用,这也是常有的事情。我这里刚好就最近某STM32用户咨询的问题稍作整理,顺便做个简单分享。

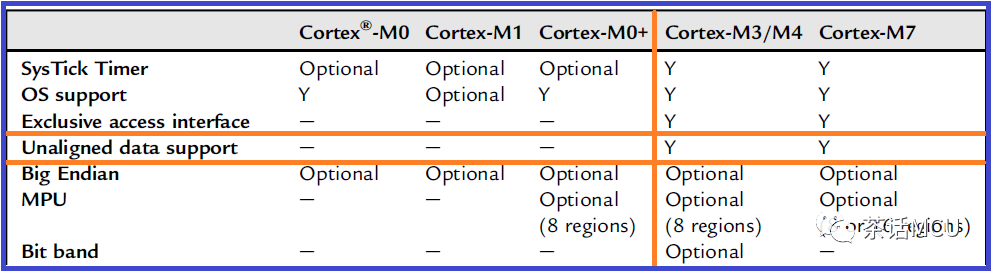

下面是部分Cortex-M内核的NVIC特性差异对照表,有兴趣的话可以看看。

该表格是我从The Definitive guide to ARM Cortex-M0 and ARM Cortex-M0+

Processors文档里提取而来,分享给大家算是借花献佛。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

工控主板发生故障该怎么办?2024-04-11 1726

-

因STM32移植而引发的两个小疑问2023-11-18 2221

-

STM32的Flash写了保护怎么办?STM32如何设置读保护和解除读保护?2023-10-29 17594

-

在STM32上移植的mx wifi源代码2022-09-26 845

-

sx1278驱动移植时报错怎么办?如何解决2022-02-21 1777

-

STM32-不同芯片的移植2021-12-29 1219

-

将代码移植到nucleoSTM32F072RBT6上出现错误2021-12-23 904

-

stm32h743外部RAM非字节对齐访问,引起的hard fault2021-12-09 991

-

STM32 进入Stop模式后电流还是很大怎么办?2021-12-08 1652

-

用户开通5G后终端耗电明显,怎么办?资料下载2021-04-13 1918

-

uboot移植遇到坏块该怎么办?2019-09-29 4562

-

电池换新无法可依怎么办2019-03-19 1911

-

将STM32F103的程序移植到STM32F107VC上,用不了该怎么办2019-01-08 4768

-

STM32F407 ADC结果无法右对齐怎么办?2018-09-10 3833

全部0条评论

快来发表一下你的评论吧 !