PCB走线串扰引起的功耗问题?

PCB设计

描述

我司有一款低功耗产品,要求关机时部分电路维持正常工作,因为电池容量有限,且电池不能充电,所以要求功耗非常低,低到5uA以下。调试过程中发现,在某种特殊场景下电池功耗异常,电流值忽高忽低,万用表电流值冲到了10uA。

虽然万用表上看到的瞬时值并不准确,但是可以肯定有瞬时电流存在,功耗异常影响了整机寿命。经过分析电路原理,发现两条信号线并排走了很长距离,并行长度可以用单位“米”来形容了,如下密密麻麻,纵横交错,当然这是特殊产品特殊走线方法,一般产品不会这么设计。

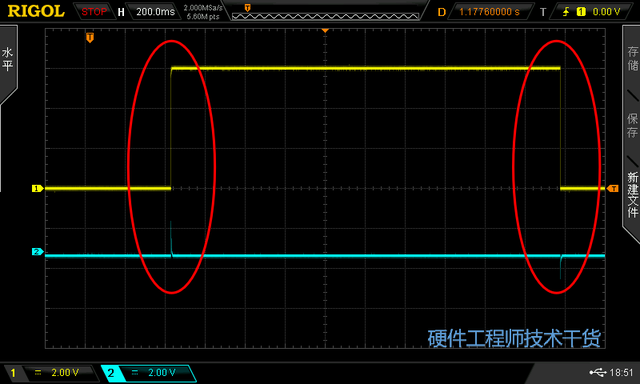

此款产品的这两个信号线并不相连,只是并行走线,一个网络是管脚输出,输出数据频率很慢,1Hz左右,另外一个管脚是输入管脚,输入管脚有一个10MR下拉电阻。使用示波器测量网络波形,如下,黄色是管脚输出信号,蓝色是另外一个管脚的输入信号。

如下图所示,黄色输出信号出现上升沿的时候,另外一个管脚出现正尖峰,峰值已经相当高了,将近1V。黄色输出信号出现下降沿的时候,另外一个管脚也出现一个负尖峰,峰值也比较高。这是由于走线之间的串扰引起的,并行距离太长,等效电容太大所致。下面会详细讲解原因。

注意:因为下拉电阻很大,使用示波器测量时,示波器的内阻会影响电路参数,测量波形和实际有差距,但是不妨碍我们进行电路原理分析。

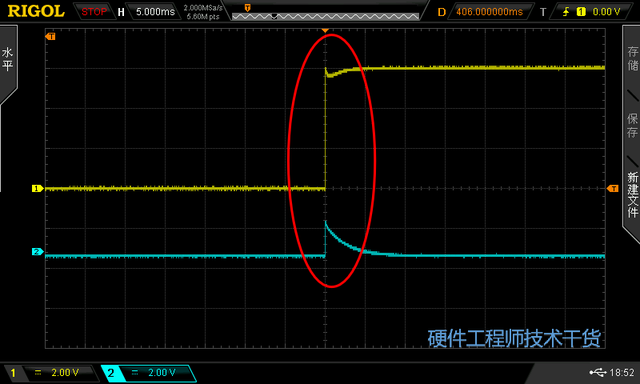

放大看一下上升沿,如下图,当输出管脚输出上升沿时,黄色输出信号有轻微跌落,蓝色输入信号迅速拉升,然后缓慢下降至正常电平。

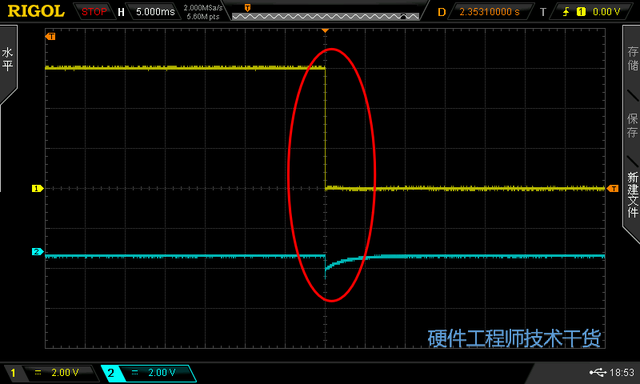

在放大看一下输出管脚下降沿,如下图,当输出下降沿时,黄色波形几乎没有什么异常,但是蓝色输入管脚有下冲,下冲很陡,然后缓慢恢复到正常电平。

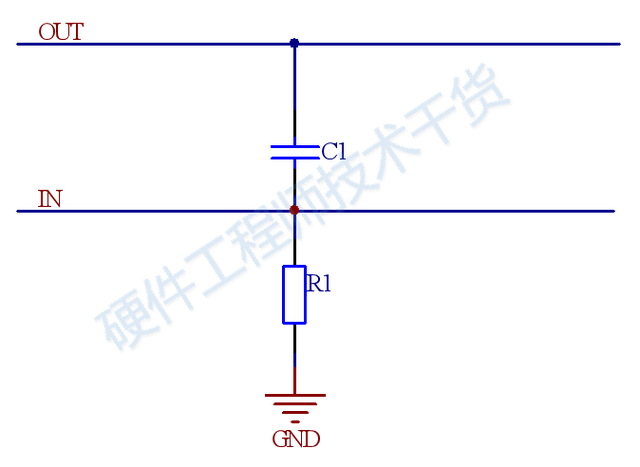

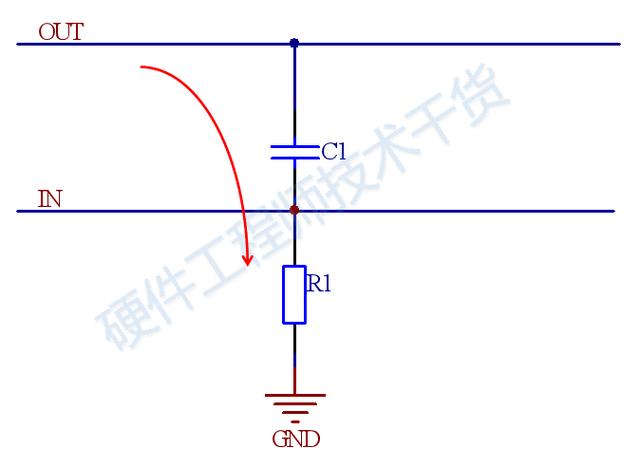

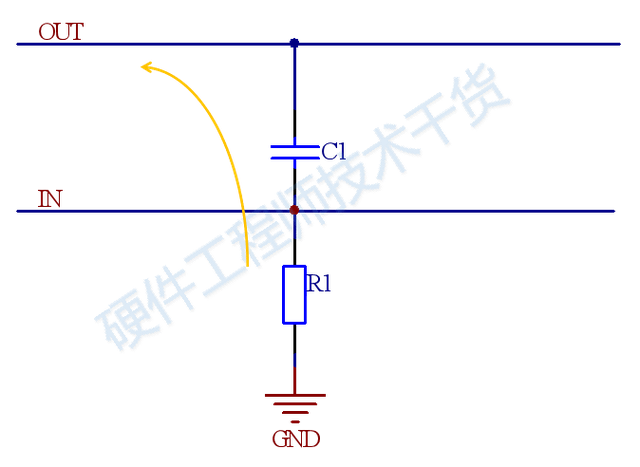

原理分析:两条走线并行距离太大,导致两条走线之间的电容很“可观”,如下图为简化了的等效电路,C1为等效电容,R1是等效电阻,这个电阻包括IN端的输入阻抗,下拉电阻等。OUT端没有数据传输的时候IN端保持低电平。

当OUT端输出高电平时,输出的高电平给C1充电,充电电流流过R1的时候会在R1上产生压降,因此在IN端能够测量出电压,此电压随着充电电流逐渐减小,也就是上面图片中缓慢降低的过程。当电容充满后IN端电压回归原始低电平。因为这里输出频率只有1Hz,而且电容较小,所以可以看到电容充满的时候,如果输出信号频率比较高,电容还没充满就开始放电了。

当OUT端输出低电平时,满电的C1开始放电,放电电流和上图相比方向相反。电流在R1上产生相反的压降,所以在IN端测量到负电压,随着电容电量逐渐放光,R1的压降逐渐减少,最终回归0点位。

电流随着输出波形变化而变化,在电阻R1上产生功耗,损失了电量。减小R1的数值可以适当减小损耗。

-

什么是串扰?PCB走线串扰详解2023-09-11 2508

-

如何减少PCB设计中的串扰问题 PCB串扰的机制和原因2023-07-20 4276

-

PCB布局之蛇形走线2022-12-27 1550

-

浅谈PCB串扰及降低方法2022-11-10 2791

-

关于高速PCB设计的串扰知识2022-08-22 4704

-

基于PCB设计的走线常用规则2022-07-13 4197

-

如何解决PCB布局中的串扰问题2021-01-13 3899

-

解决PCB设计消除串扰的办法2020-11-02 2502

-

在高速PCB设计中消除串扰的方法与讨论2020-09-16 3369

-

PCB串扰如何解决2019-05-01 4195

-

信号在PCB走线中关于串扰 , 奇偶模式的传输时延2015-01-05 6359

-

高速PCB中微带线的串扰分析2011-11-21 1350

全部0条评论

快来发表一下你的评论吧 !