浅析clock gating模块电路结构

电子说

1.4w人已加入

描述

ICG(integrated latch clock gate)就是一个gating时钟的模块,通过使能信号能够关闭时钟。常用场景:低功耗状态下,关闭部分时钟源;无毛刺时钟动态切换等。

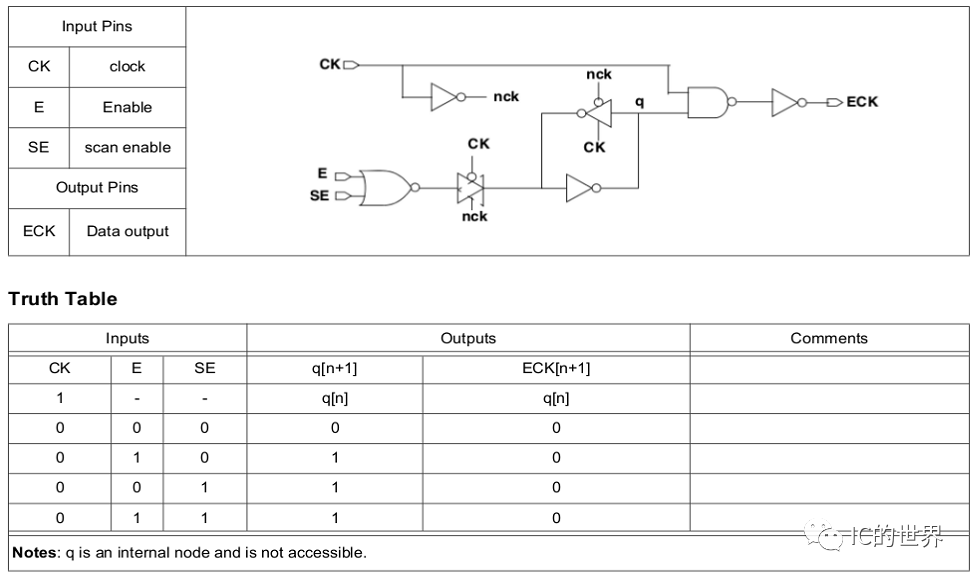

如图所示为一款ICG电路结构图,输入时钟为CK,输出时钟为ECK,E为使能信号,E为0表示关闭时钟,ECK输出为0。

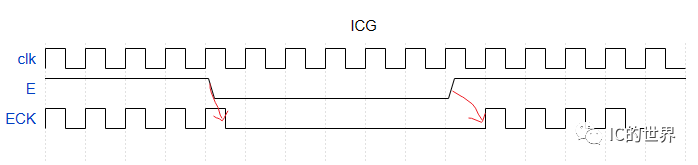

结合波形图和电路结构图,可以看到:

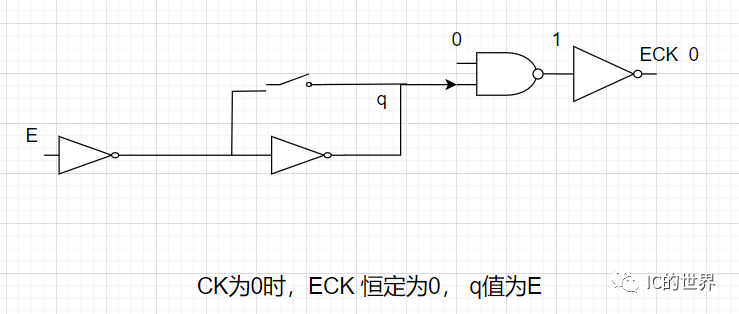

当CK为0时,ECK 恒定为0, q值为E:如果E为1,则q为1,如果E为0,则q为0。

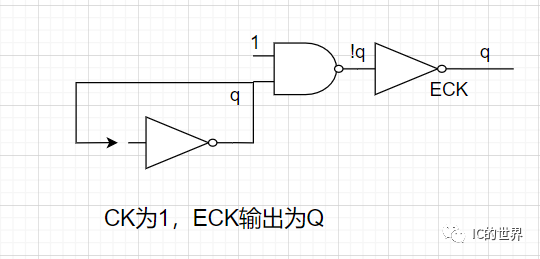

当CK为1时,ECK 恒定为q(n),即对应的上一次CK为0时,锁存的E值。 因此最终的效果就是,只要E配置成了0,那么ECK会在CK的下降沿跳变成0,随后只要E保持为0,那么ECK一直为0。 当E从0跳变成1时,ECK会在CK的下一个上升沿跳变成1.

NOTE: 建议先将E输入信号同步到CK时钟域,这样E的跳变会发生在CK上升沿附近,因此在CK处于低电平时,E已稳定,有足够的时间驱动q值,使q达到标准电压阈值,而不是介于0/1之间的电压,从而保证了ECK的驱动能力。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

降低电路漏电功耗的低功耗设计方法2020-09-16 13212

-

clock-gating的综合实现2023-09-04 3474

-

门控时钟(Clock-gating)介绍2026-01-16 101

-

浅析开关型稳压电源结构原理2012-08-06 2234

-

电源滤波电路浅析2013-02-06 11789

-

浅析TVS管的结构特性2018-11-05 3416

-

浅析交流发电机转子绕组端部结构2017-01-01 1226

-

浅析LLC谐振电路的拓扑结构与电路仿真2021-11-17 2247

-

低功耗设计基础:Clock Gating2023-06-27 2834

-

AND GATE的clock gating check简析2023-06-29 5436

-

Clock Gating的特点、原理和初步实现2023-07-17 6933

-

ASIC的clock gating在FPGA里面实现是什么结果呢?2023-08-25 1611

-

SOC设计中Clock Gating的基本原理与应用讲解2024-04-28 4374

全部0条评论

快来发表一下你的评论吧 !