Linux 下GCC的编译

描述

一、Linux 下多文件编译

在上一篇 Linux 下的 C 编程我们知道了 Linux 下的编译器为 GCC ,以及如何使用 GCC 进行编译,在文章我们讲解 GCC 的编译,使用的只使用了一个 .c 文件,直接使用

gcc [目标文件] -o [想要生产的文件名字]

那在遇到多个 .c 文件的时候如何处理呢?

实际上还是使用上面这条指令,其中的 [目标文件] 是可以为多个的。

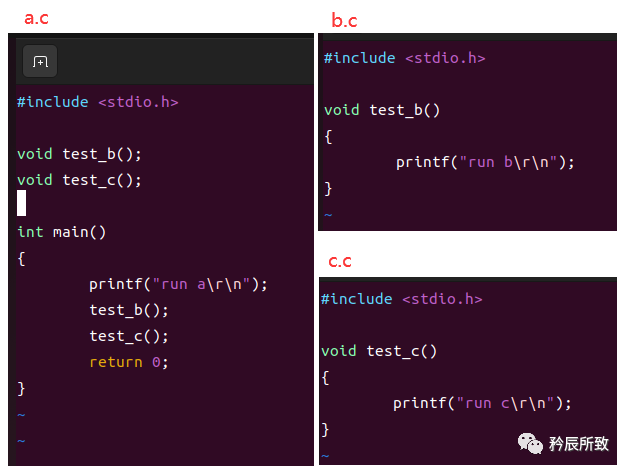

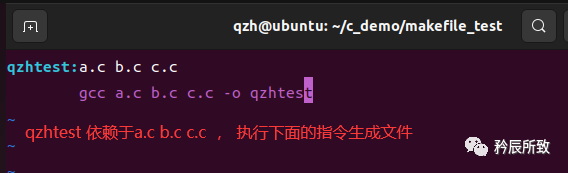

举一个简单的例子,我们写了三个.c 文件,内容如下:

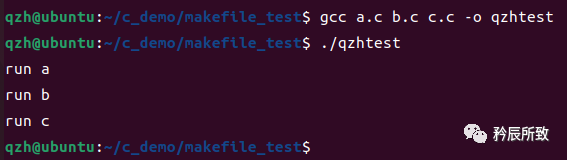

编译的方式如下图:

这么看起来是不是感觉还算简单?但是我们可以试想一下,以后做项目的时候,成千上万个文件,怎么办?

我们要考虑2个主要问题:

1、 文件数量多起来了以后如何处理?

2、只修改了单个文件,如何只重新编译修改过后的单个文件?

我们不可能和上面示例一样手动使用 gcc 命令输入文件名的,而且文件多起来了,编译时间需要很长,使用上面示例的命令,是会把所有的文件都重新编译,在后面的 linux 学习开发中,项目的编译时间可比学习 51 、STM32 哪些工程的时候多得太多,每次都编译所有文件这种行为肯定是不可取的。

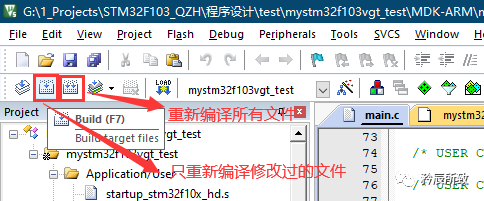

在 Windows 下面我们有各种集成的 IDE 工具,往往只需要一个按钮,就可以编译整个工程,方便快捷,比如我们熟悉的 Keil,我们只需要点击 IDE 工具栏目的一个按钮,就可以完成我们想要的操作:

那么在 Linux 下,我们该如何处理呢?

这就要用到本文主要说明的东西:Make 工具 和 Makefile 。

二、make 工具和 Makefile

首先我们要知道什么是 Make 工具,以及 什么 是 Makefile。

这部分的内容时基本概念,类似名词解释,大家记住就好,没有什么特别需要说明的,因为我们的重点在于知道以及学会他们的使用.

2.1 make 和 Makefile 是什么?

make 工具:

make 本质上它是一个程序,是一个编译工具。我们在后面进行程序的时候,都需要使用 make 命令。

使用 make 工具我们可以自动完成编译工作,而且可以有效的处理我们上面提到的问题:

- 多个文件的自动编译;

- 每次执行 make 命令,只重新编译修改后的文件;. 这里提一句,Linux 是如何判断文件是否有修改:文件的修改时间!就是通过

ls -l查看的那个时间,make 会根据依赖关系,如果发现依赖的文件修改时间比自己新,那么久会重新编译一下这个依赖文件)

利用 make 工具可以将大型的开发项目分解成为多个更易于管理的模块,可以简洁明快地理顺各个源文件之间纷繁复杂的相互关系,大大简化开发工作,避免不必要的重新编译 。

make工具通过一个称为 Makefile 的文件来完成并自动维护编译工作,Makefile文件描述了整个工程的编译、连接规则。

Makefile 文件:

Makefile 是一个文件,是一个描述一系列规则的文件。

Makefile 的 开头 M 要大写!(虽然有的地方说大小写都可以,但是保证大写,是肯定不会有莫名其妙的问题的)。

make 会根据 Makefile 文件的规则规则执行命令,最后完成编译输出 。

在 Makefile 文件中:

- 定义一系列的规则来制定源文件编译后的先后顺序

- 特定的语法规则、支持函数定义、函数调用

- 能直接集成操作系统中的命令

这是我们学习 Linux 的一个重点对象,对于新手来说,至少要做到能够看得懂,会一定程度的修改 Makefile 。

2.2 通过 STM32 提前熟悉 Makefile

实际上 STM32 的开发,我们也可以用到 Make 工具和 Makefile,如果大家目前也在用 STM32 开发,不妨使用 GCC 工具链开发,这样也能提前熟悉 Makefile 。

如果是我的粉丝朋友,一定知道现在我做 STM32 都是使用的 gcc 工具链,具体可查看文章:

抛弃IDE — 在window下使用VScode搭建ARM开发环境

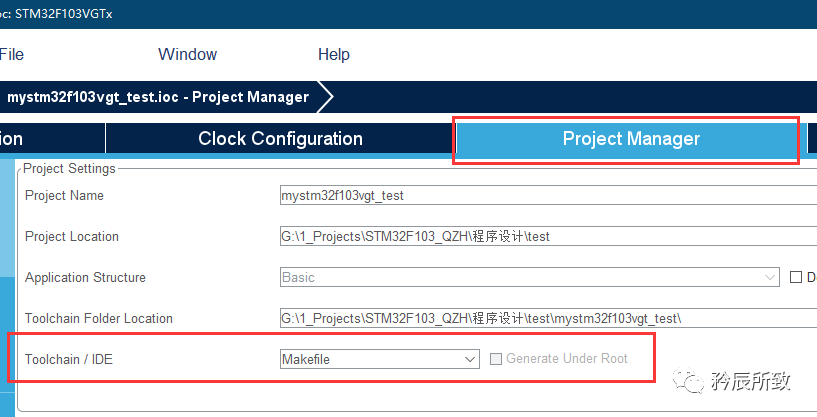

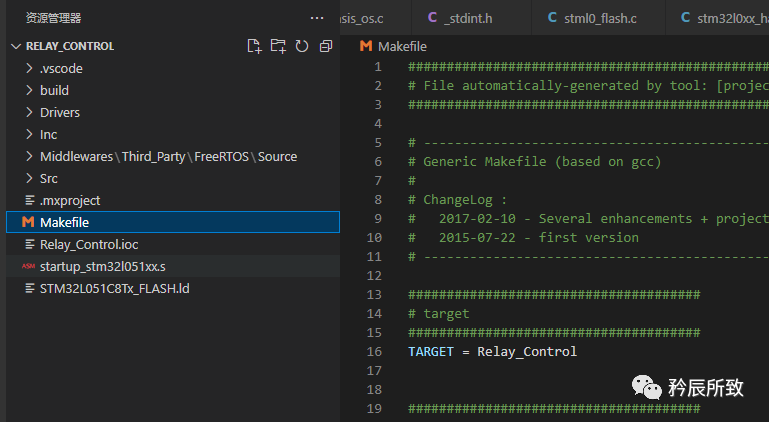

如果想看看简单的 Makefile ,大家可以写一个简单的 STM32 工程,然后在 STM32CubeMX 生成工程的时候选择 Makefile ,如下图:

然后打开工程,就可以看看 ST 工具自动生成的 Makefile 文件了,可以让自己提前熟悉熟悉 Makefile:

2.3 GCC 与 make 的关系/区别?

经常有小伙伴会被 GCC 与 make 工具搞得糊里糊涂,虽然知道怎么用,但是傻傻分不清楚或者是说不明白。

看清楚概念:GCC 是编译器,make 是一个命令工具。

感觉把概念一说就清楚了啊, GCC 是一个编译 C语言的编译器, 而 make 是一个工具,他可以使得编译工作简化,只不过我们使用的时候 make 会调用 GCC 编译器去完成编译工作。

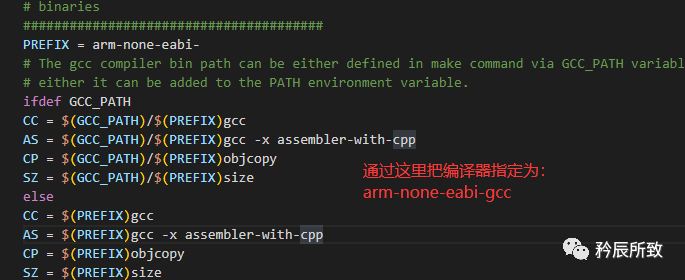

在 Makefile 中我们会指定执行编译的编译器类型,而且会根据指定的编译器类型进行对应的命令操作,如下图:

因为我们在 linux 下使用的都是 gcc 编译器,所以 Makefile 中的会看到我们熟悉的 gcc 的操作命令,我们只不过是利用 make 工具的自动编译去调用了 gcc 编译器 对工程进行编译。

三、一个简单的 Makefile

上面说过,Makefile 是学习 Linux 的一个要点之一,对于 Makefile 说明,我会单独分专栏进行说明介绍,那本文我们刚刚接触,我们写一个简单的 Makefile 来编译文章开头我们示例的3个文件。

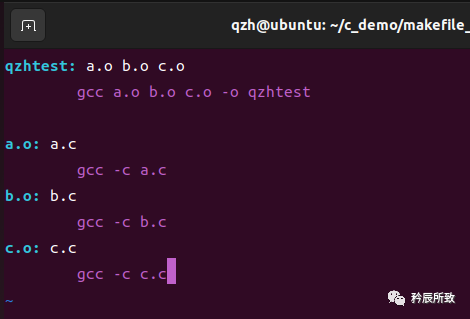

直接先写一个傻瓜式的,看看 make 工具是否有用,在示例 .c 文件同目录下,我们新建一个 Makefile 文件,如下:

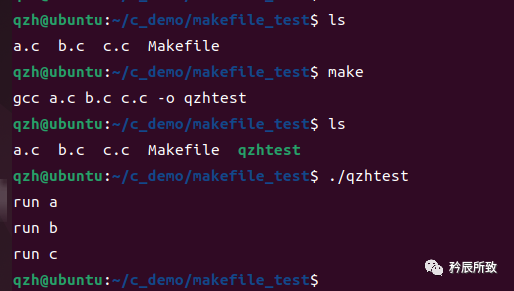

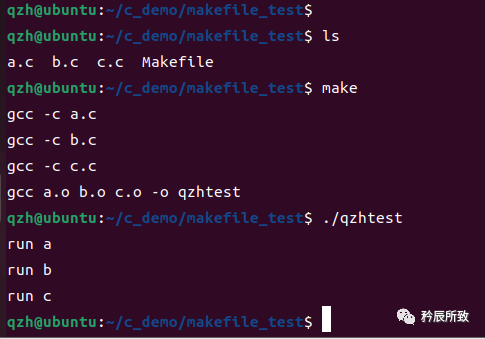

然后试着使用 make 命令看看效果:

OK,果然可以 make 直接编译,但是上面这个 Makefile 是有问题的,因为每次执行 make ,会把所有的 .c 文件都重新编译器一次,实际使用也不可能这么写。

我们回忆一下上一篇课程的内容,一个C 文件要经过预处理、编译、汇编 和 链接才能变成可执行文件,由不同的 .c 文件生成到不同的 .o 文件,最终才将所有的 .o 文件链接成可执行文件。

所以我们可分开进行,把每一个 .c 先生成 .o 文件,然后再由 所有的 .o 文件生成 最终的文件,这样如果单独修改了某个文件 ,只需要把修改过的 .c 文件重新编译就行了,所以我们的 Makefile 应该这么写:

make 的结果如下:

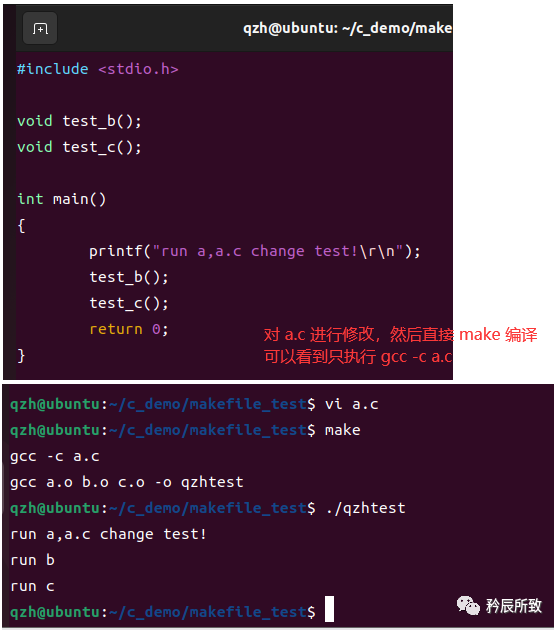

这样写得好处就是,如果我们只对某一个.c 文件进行修改,他只会对修改过的文件进行重新编译,我们可以测试一下,比如我们修改一下 a.c 文件:

上面这个简单的 Makefile ,大家是不是已经可以感觉到 make 工具的方便快捷了!

结语

本文向大家介绍了一下 Linux 编程时候使用的 make 工具,如何在没有 IDE 工具的 Linux 环境下高效快捷的编译工程,就靠 make 工具了。

当然,我们的重点在于 Makefile,对于 Makefile 的写法规则,更多的内容我会单独写文章说明的。

对于入门的小伙伴来说,也没有必要一蹴而就,写好 Makefile 固然重要,但是对于现在一般的应用开发来说,Makefile 要完全自己从头写得时候不多,很多时候可以找到一个可用的模板进行修改,我们至少要做到可以看懂,可以去修改 Makefile!

-

Linux的gcc编译过程介绍2023-07-14 978

-

Linux使用gcc编译程序的语法2023-06-22 1703

-

【Linux编程】如何使用gcc生成预编译文件?2022-08-31 3042

-

【Linux编程】如何使用gcc编译源代码时输出map文件?2022-08-15 10096

-

Linux开发环境下的Arm gcc交叉编译介绍2022-06-02 3832

-

"Linux下使用VSCode,GCC,OpenOCD实现STM32一键编译烧录调试(STM32CubeMX篇)"2021-12-06 1603

-

迅为龙芯2K1000开发板Linux下gcc编译2021-11-26 2354

-

gcc的使用方法以及Linux gcc 的常用选项2020-10-22 4089

-

Linux系统下Gcc的基本用法和选项2020-08-20 1590

-

Linux下开发STM32 使用gcc-arm-none-eabi工具链编译生成bin、hex文件2020-02-28 13329

-

Linux教程之如何对Linux系统下的gcc进行编程的基本使用教程2018-11-02 1184

-

常见gcc编译警告整理以及解决方法2017-11-14 22325

-

Linux下C/C++编译器gcc使用指南2017-11-02 1008

-

Linux环境下程序编译2011-04-05 615

全部0条评论

快来发表一下你的评论吧 !