高速电路电源完整性测试之电源输出阻抗和环路测试

电子说

描述

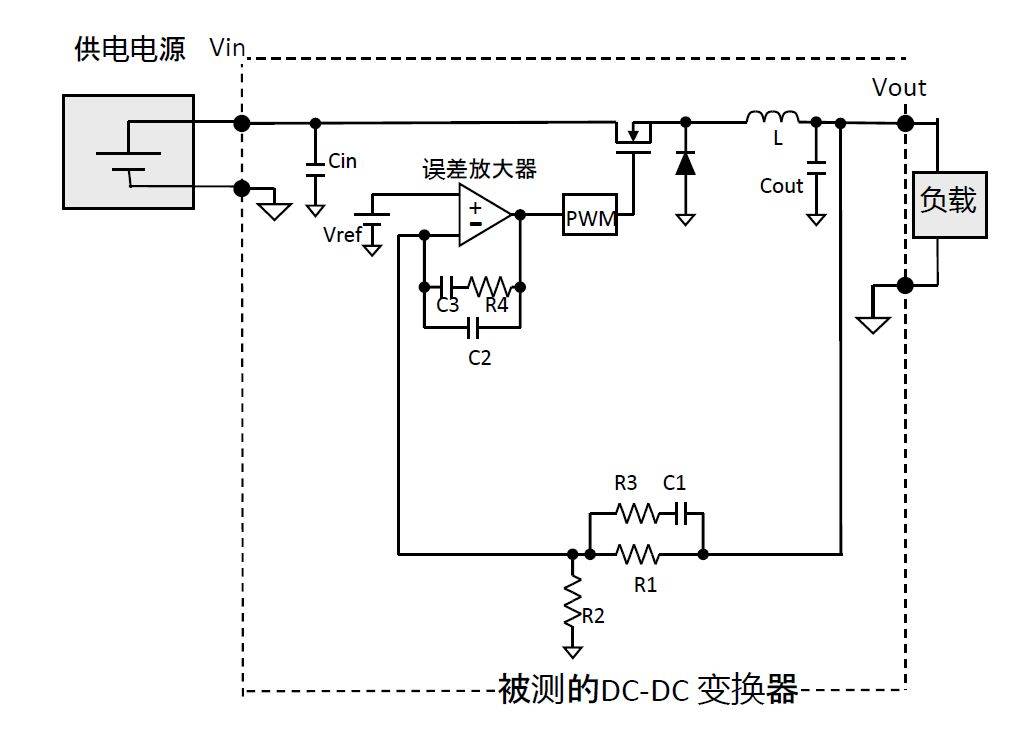

DC-DC 变换器原理示意图:

DC-DC可以降压也可以升压。

供电电源过来的DC经过开关管变成脉冲。

脉冲经过滤波电路变换回DC输出。

通过在输出端电压采样,进行负反馈调整脉冲占空比,可以控制整个能量输出,达到稳压目的。

造成输出DC不稳的原因主要是负载电流变化,当然还有其他因素比如输入不稳,环境变化等。

改善电源完整性方法

1、优化反馈环路设计

瞬变响应速度

环路稳定性

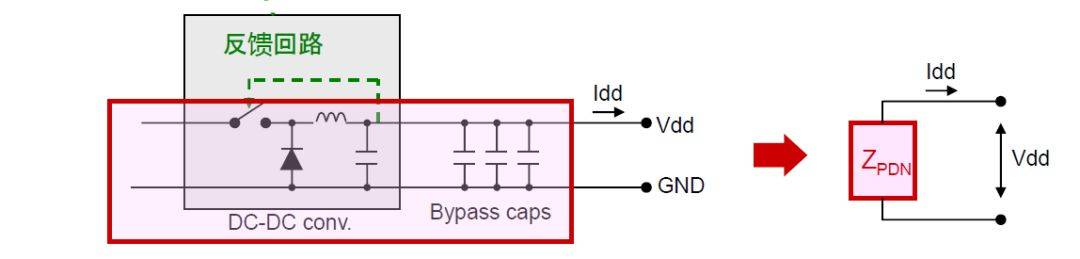

2、将|ZPDN| 压到一个小数值

可以使得Vdd波动最小化,因为Delta-Vdd= ZPDNx Delta-Idd(较小的ZPDN 较小的Delta-Vdd)

DC-DC电源模块反馈环路的特征测试

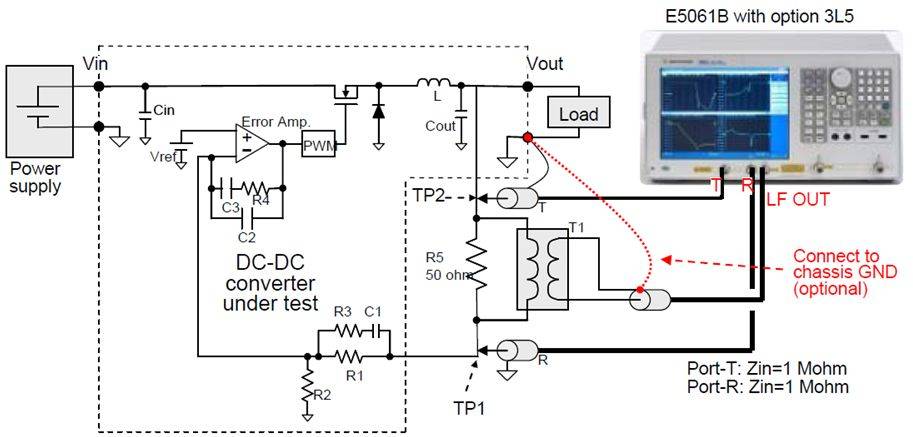

Keysight E5061B 低频-射频网络分析仪的选件3L5,可以提供±40Vdc 的直流偏置电压叠加到从端口 1 或 LF OUT端口上输出的交流信号上。此外,如果在仪表的 S 参数测试端口上对被测器件进行测量时,它还可以从 LF OUT端口输出直流电压。可以在5Hz~3GHz 的率范围内提供常用的网络测量和分析功能。功能全面的低频网络测量能力(包括内置的 1MΩ 输入) 都被完美地集成到这个高性能的射频网络分析仪之中。

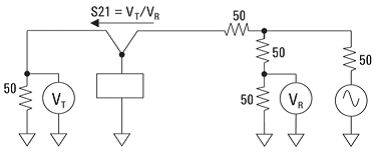

使用 E5061B-3L5可以测试DC-DC电源的环路增益、相位裕量、增益裕量等反馈环路特性。比如环路增益测试测试配置如下图:在E5061B-3L5的高输入阻抗测量接收机的R和T端口上测量激励施加电路两侧的交流电压,随后把这两个测量结果进行比值计算得到环路增益最终的测量结果。

把激励信号加在满足Zin >> Zout 的点上,并让电阻R满足Zin >> R >> Zout的条件,可以通过T/R 比值的测量结果得到循环传递函数-GH 的特性,这里选择R=R5=50欧姆;

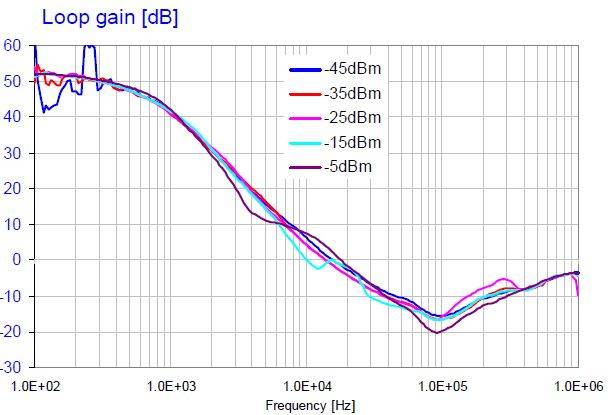

如下图所示,当测试得到环路增益|GH|后,通过游标找到|GH|=1的交叉频率。同样的,在相位测量曲线即可得到相位裕量,进而可以测量增益裕量。

DC-DC电源模块输出阻抗测试

电源的输出阻抗会影响到在电流变化时输出电压的变化,其输出阻抗越小,瞬态电流变化对输出电压的影响越小。DC-DC电源输出阻抗的测试有电流-电压检测法和并联-直通法测试。电流-电压方法使仪表激励信号源和被测件直流输出电压之间很好的隔离,接收机使用高阻输入端口,适用于测试输出电压较大的DC-DC变换器的输出阻抗。但是,这种方法不适用测试毫欧级的输出阻抗。

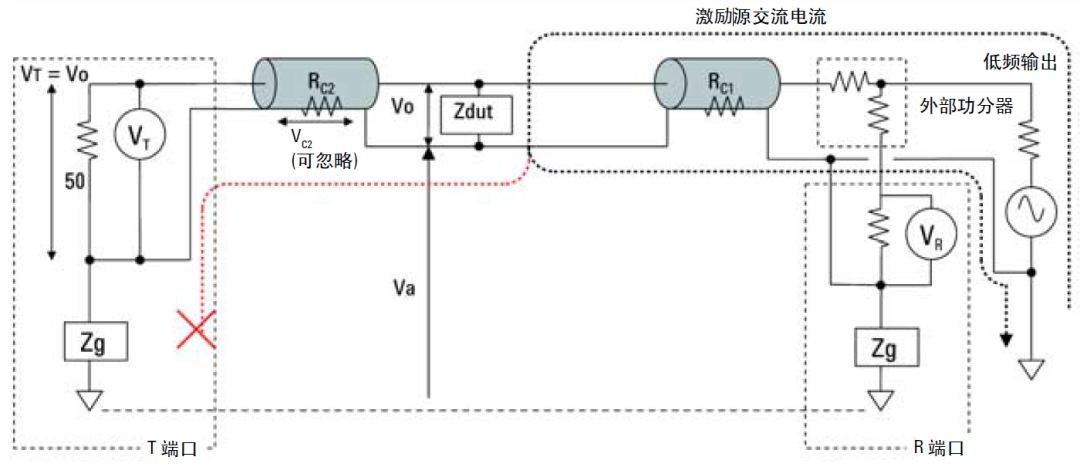

并联-直通方法能够对毫欧级的微小阻抗进行精确测量,通过测量T,R端口传输系数S21推导出输出阻抗。Zdut 和S21 之间的关系为: Zdut = 25 x S21/ (1-S21),其原理如下。

由于激励信号源和接收机之间测试电缆的接地环路的电压下降会引入误差,传统的低频网络分析仪对于非常小的毫欧级阻抗的测试非常困难。虽然可以在激励源、接收机一侧加入磁环抑制电流,或者使用变压器隔离接地环路,然而合适的磁环非常难以选择,变压器剩余响应的影响也无法完全消除。

Keysight网络分析仪E5061B-3L5 的增益-相位测试端口使用在低频大约30Ω半浮置的接地方法,可以阻止屏蔽电流,不需要外部磁环或变压器就可以轻松测试毫欧级的输出阻抗。下图是使用E5061B-3L5 增益-相位端口精确测试DC-DC变换器输出阻抗的原理。

电源分配网络PDN阻抗测试

数字电路系统中,电路供电通常使用DC-DC Buck-Boost单元或LDO模块。由DC-DC单元、电路板的电源布线层、无源器件(整形LC、旁路电容、去耦电容)组成了电源分布网络(Power Distribution Network)。

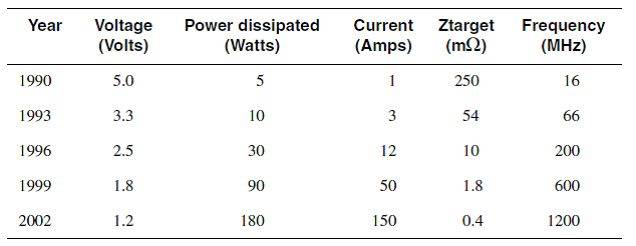

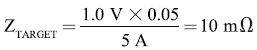

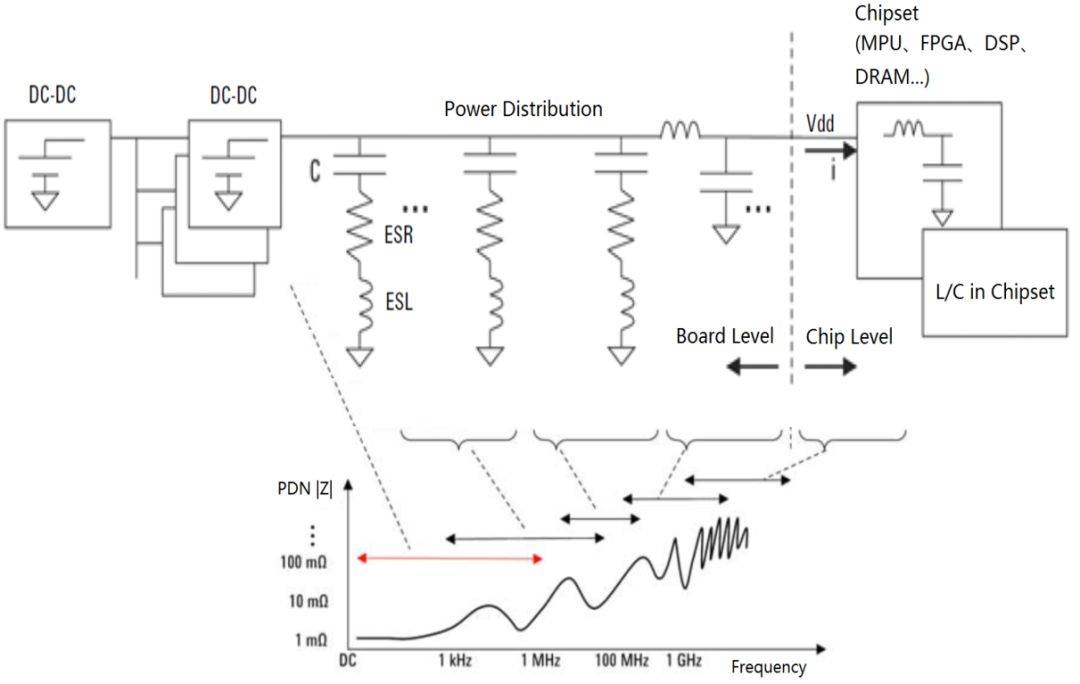

为了评估电源系统对纹波噪声的要求,以及方便在频域和时域评估电源系统,引入了目标阻抗Ztarget。目标阻抗同样遵循欧姆定律,假设电源电压为5V,纹波范围要求为5%,负载电流微1A,电路工作时电流变化在50%以内,那么对目标阻抗的要求为 Ztarget ≤ (5*0.05)/(1*50%)。随着数字系统频率的增加以及集成规模增大,为了减小功耗电源电压越来低,电源纹波要求越小,对PDN阻抗的精确测试变的异常重要。下图显示了数字电路电源功耗、工作频率、PDN目标阻抗的变化趋势。

如前面提到的,假设Zpdn 是从负载器件一端看到的Vdd 和接地层之间的阻抗,Delta-I 就是由负载器件的工作所引起的电流变化,在电源层面上会产生电压降Delta-V = Delta-i x Zpdn。更严格地讲,电压降应该是: Delta-V =IFFT (FFT(delta-I) x Zpdn)。对于MPU 之类的高性能LSI的应用情况,Delta-I可能是几安培或几十安培,对于包含大量大规模集成芯片的高速数字电路中,低电压大电流工作时,电源分布网络(PDN)极小的输出阻抗会引起电压的较大波动,超出电压幅度的要求范围,导致信号完整性和电磁干扰问题。比如供电电压为1V,允许的纹波噪声或者电压偏移为5%,电流变化范围为5A,则PDN的阻抗要求为:

因此,在从DC到GHz的广阔频率范围内,必须将电源层的阻抗Zpdn 抑制在一个极小的值上。下图显示了PDN网络阻抗的影响因素及的频率和阻抗范围。

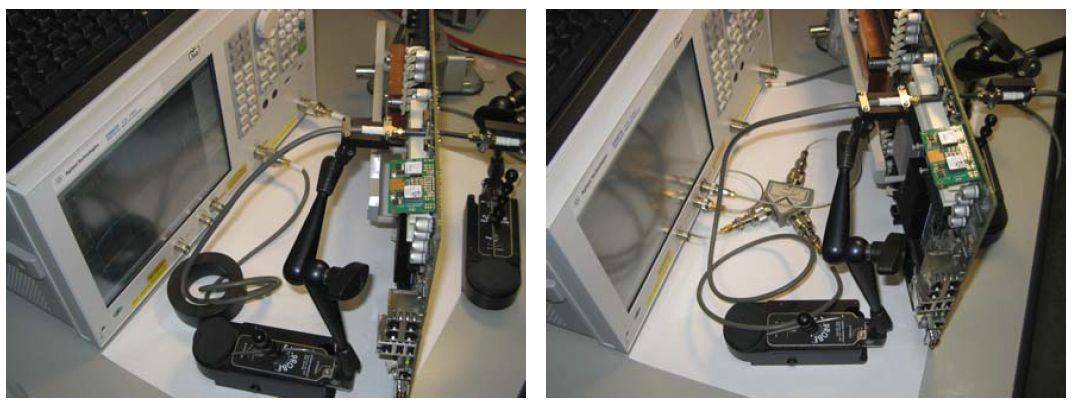

在装配好的电路板上,安装有DC-DC变换器,滤波LC电路,旁路电容、磁珠等无源器件,以及电源层的网络布线共同构成PDN阻抗。同样,可以使用增益相位端口或者S端口测试系统级的PDN阻抗。使用S端口测试时,频率范围可以在5Hz-3GHz,需要使用磁环抑制线缆接地环路引入的AC电流。也可以在系统上电或者断电条件小测试系统电路板的PDN阻抗。下图是用E5061B进行PDN网络阻抗测试的例子。

无源器件如电感,电容也是PDN的重要部分,电容器作为旁路电容,选择不同容值,可以在相应频率范围抑制PDN的阻抗,减小电源噪声。

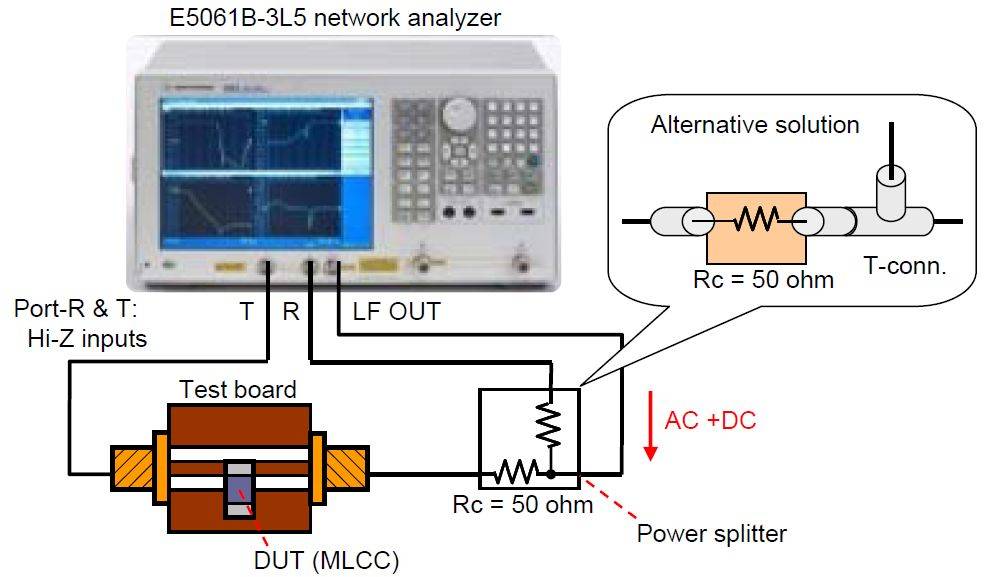

并联-直通测量在小阻抗范围内具有良好的灵敏度,通常用于测量旁路电容。对于铁氧体磁珠等去耦器件,阻抗较高,使用反射测量方法进行测试。由于测试电缆接地环路的影响,会在低频段导致阻抗测量结果的较大误差。如前所述,E5061B-3L5 的增益相位测试端口的半浮置接地结构可以消除这一影响,频率范围5Hz-30MHz。还可以使用S参数端口测量更高频率范围的阻抗特性,5Hz-3GHz,需要使用磁环抑制流过接地屏蔽层的交流电流。下图显示了E5061B-3L5 用增益相位端口进行电容阻抗测试方法。

审核编辑:汤梓红

-

普源DHO3000系列示波器电源完整性测试2025-04-15 932

-

高速电路中的信号完整性和电源完整性研究2024-09-25 491

-

高速电路电源分配网络设计与电源完整性分析2024-09-19 745

-

电源完整性仿真和测试解决方案2023-09-12 8519

-

电源完整性设计与测试2022-08-30 4388

-

基于示波器测试电源和信号完整性的挑战2022-08-01 1170

-

高速电路信号完整性分析与设计 —阻抗控制2022-02-10 1073

-

什么是电源和信号完整性?2021-12-30 2116

-

电源和信号完整性的分析与测试2021-09-03 2665

-

高速PCB电源完整性设计与分析2021-04-21 2177

-

电源完整性(PI)设计和测试2020-10-20 1491

-

电源环路响应测试方案的学习2020-02-11 2663

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 7044

-

高速信号的电源完整性分析2012-08-02 3623

全部0条评论

快来发表一下你的评论吧 !