Virtuoso软件中常见的约束方法

描述

早期,电路设计工程师经常需要手工标注相关的信息在原理图上用于提醒版图工程师相关器件的版图设计要求,比如匹配,对称等。其实VSE早就引入了设计约束功能,并且通过layout 同步schematic的约束,还可以快速的检查约束规则是否匹配。

有了这项功能后,就不需要和牛逼哄哄的版图工程师费口水了。

主要的方法如下

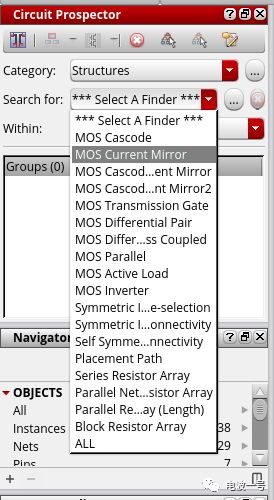

1, windows-assistant-> Circuit Prospect可以调用出电路模块的匹配功能,快速查找出常用的需要约束的地方比如Power Nets,current mirror以及differential pair这些模块。主要分为Structure, Devices, Nets, Pins, inst Terms, 比较常用的还是Structure和Device,虽然经常匹配不到。

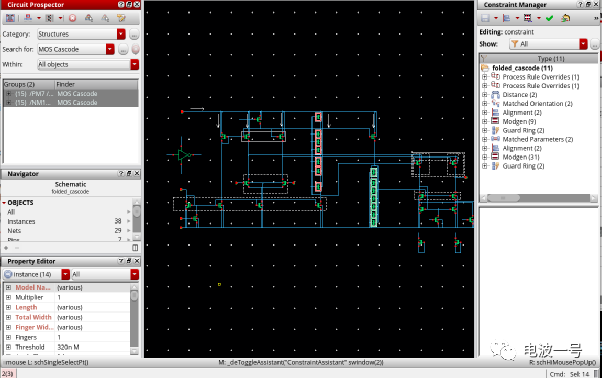

2, Windows--> assistant -->Constraint Manager

可以调出相应的约束菜单,支持的约束类型可以分为三大类,Electrical, Placement 和Routing。比如常用器件参数匹配就在Electrical中的Parameter Match

点击设置好的约束,可以高亮原理图对应的管子。

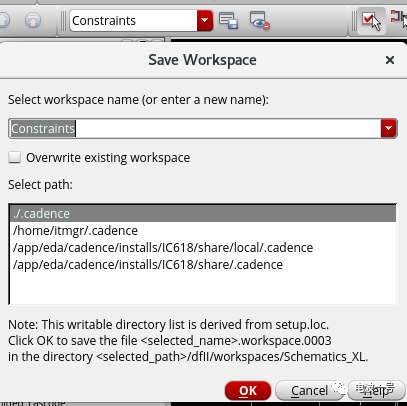

正常开启之后设计的界面如下,可以通过windows-workspace-->save workspace,方便下次快速调用。

比较常见的约束方法有,

1, VDD/VSS power net用Process Rule overide 使用更粗的线宽, 比如4X,6X minimum width

2,current-mirror 用modGen 自动生成。

3, 等等等

Lanuch layout -XL后,原理图的constraint 可以自动同步过来,也可以手动将更新部分同步。Check Constraint开了之后,版图中是否违法constraint可以直接发现。

总体来说,Constraint Manager是一个相当能减少沟通成本的好工具,也是模拟设计向数字设计方法学习的一个体现,不知道贵司是否已经在生产中应用。

-

人工智能中常见的数据标注方法2023-09-21 3831

-

linux系统中常见注册函数的使用方法2023-10-19 1473

-

FPGACPLD中常见模块设计精华集锦2012-08-17 4228

-

电源中常见的故障现象如何维修2021-03-11 1889

-

在无线移动数据接收中常见的问题2021-04-14 1641

-

HDMI I/O设计和测试中常见的问题?怎么解决?2021-06-02 1698

-

网络设备中常见术语含义及故障分析2011-12-27 15248

-

FPGA时序约束方法2015-12-14 1005

-

版图布局软件Virtuoso快捷键总结资料下载2017-12-21 1588

-

分频器的相位问题_音响中常见的相位问题及解决方法2018-05-28 46377

-

WillSemi采用的Cadence Virtuoso定制IC设计平台有哪些优点?2018-08-08 1810

-

keil中常见的各种错误警告以及相应的解决方法资料说明2019-03-08 2992

-

直线导轨使用中常见的问题有哪些2023-08-03 2129

-

PCB阻焊工序中常见品质问题及解决方法2023-08-30 3188

-

理解STM32控制中常见的PID算法2023-10-17 3586

全部0条评论

快来发表一下你的评论吧 !