模拟top仿真中数字控制的快速方法

描述

模拟中使用数字调整电路是非常非常频繁的,用途比较多的是改变电流,电阻。在模块级别仿真生成控制的寄存器控制信号也是件麻烦的事。

传统工程师有这样的几个办法:

1, 用多个vbit(好像经常有bug,数半天0110,1个小时跑完后发现弄错了)。

2, 也有写个脚本生成vpwl/vpwlf。(仿真慢,vbit还能当成事件驱动来优化仿真速度,vpwl/vpwlf真是没救了)

3, 也可以使用ahdl library里面的adc的,应该更慢吧。

4, 当然也可以写vams激励,但是需要切换仿真器,一些频域的仿真就受限制,再说要是会ams,一般工程师就不做模拟了。

当然最好的方法是直接有一个pcell,其实如果熟悉virtuoso的那个括号括号的编程环境,就可以很容易的做一个这样的模拟寄存器位产生模块。

通过使用位操作可以快速的实现模拟环境中二进制寄存器控制位产生,如果有数字设计背景,对位操作应该非常熟悉。

括号语言中关于几个位操作符的定义如下

在CIW里面实践一下:

看完CIW里一顿猛如虎的操作,大家应该知道怎么实现了,具体的方式是将控制量移位后和1做位与 操作,就可以得到相应的二进制代码。

比如3,对应0011, (3>>3)&1=0 , (3>>2)&1=0 , (3>>1)&1=1 ,(3>>0)&1=1。

只要把这个写到Analog/Vdc模块里,做成一个通用的设计库单元就行了。考虑到浮点数的原因, round一下就解决了。同时为了方便参数传递,把数字电压和控制数使用了pPar()传递进来。

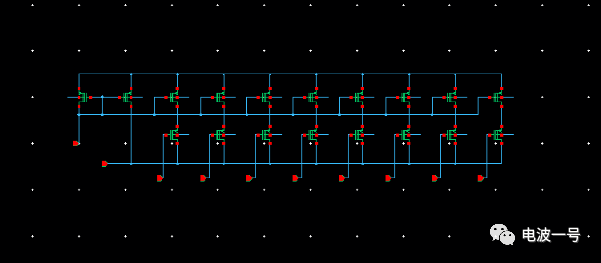

考虑到不同工艺的数字电压可能有些变化,多加了一个dvdd的参数。最后的效果是这样的,隐隐约约的可以看到电阻上对应的数字电压了吧。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PFC模拟和数字控制的比较 PFC对电网稳定性的贡献2024-12-16 1539

-

反射内存卡在半实物模拟仿真中的使用以及如何使用2024-11-01 820

-

模拟控制式和数字控制式VGA应用指南2023-11-28 354

-

使用仿真设计的电力电子数字控制器2023-02-03 1213

-

如何定制数字控制回路的模拟组件2023-01-03 1749

-

如何使用电力电子仿真数字控制器2022-04-25 2631

-

智能电源:模拟和数字控制回路实现对比2021-09-29 3822

-

如何正确模拟仿真中的VLSI电路?2021-06-17 2020

-

新型数字控制方法在有源滤波器中的应用2021-04-21 1211

-

数字控制真的会取代模拟控制,而成为PFC中的主流控制方式吗?2021-04-07 2417

-

三菱PLC模拟仿真中文软件2016-01-14 1919

-

模拟控制式和数字控制式VGA(二):数字控制式VGA2012-06-08 4234

-

基于Linux的实时数字控制系统设计2009-09-08 657

-

功率因数校正(PFC)的数字控制方法2009-07-11 5319

全部0条评论

快来发表一下你的评论吧 !