同步FIFO设计分析

描述

模块虽小但是要有新意,首先写一个同步FIFO,这是一个烂大街的入门级项目,但是我肯定不会写的那么简单,需求如下:

- size=3232(高宽)

- 同时读写

- 给出空满、将空将满信号

- 单口sram接到读使能下一拍出数据(或者n拍之后)

和大多数文章所写描述的同步FIFO的需求不一样的地方在于最后一个需求,内部例化的sram的读取动作不是读及读出的操作。因此基于这种sram,又要兼顾FIFO的标准协议,以及需要FIFO逻辑速度到达最优,需要对设计进行一些小的处理

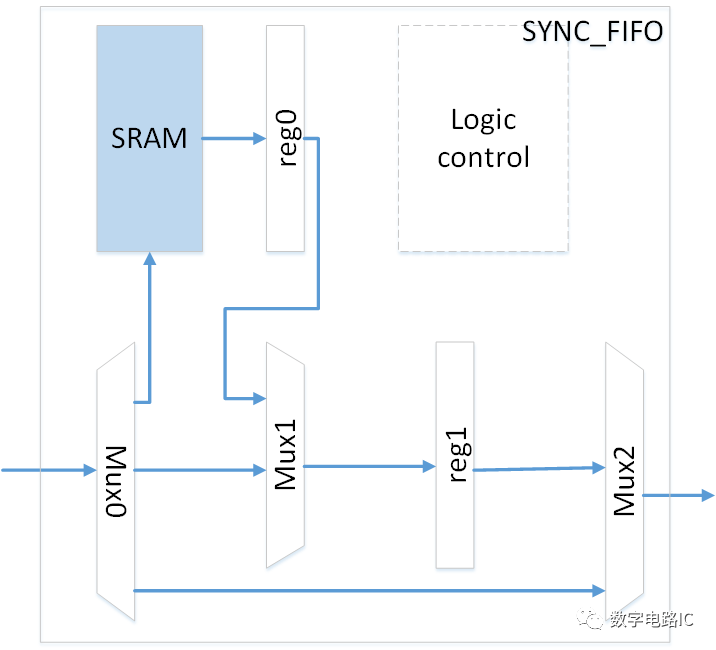

下图为本次同步FIFO设计的框图:

设计分析:

- 使用reg0的原因

由于sram延时一拍读出,因此就需要有reg0处理延时,既只要reg0为空,寄存器就向sram读数,达到提前取数,消除延时的效果。(一般sram有几拍延时就有几个reg0) - 使用reg1的原因

reg1用于处理边界条件,在sram和reg0为空时,没有读使能的情况下写入第一个数,此时第一个数如果存入sram,则读取流程将变成sram-reg0-output,中间延迟过长,但是假如使用reg1用于存储第一个数据,则可以把这一拍数据延时解决掉。(且同上述,一般有几个reg0就有几个reg1) - 使用mux2的原因

mux2也是用于处理边界条件,在sram和所有寄存器都为空时,写使能和读使能同时来到,则数据bypass通过SYNC_FIFO模块。 - mux0和mux1则用于处理上述逻辑关于数据通道切换的处理。

- 关于sram存取、各种空满信号的判断,就不再一一叙述,想了解这方面设计可以参见网上各种同步FIFO设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

同步FIFO和异步FIFO区别介绍2024-06-04 3848

-

握手型接口的同步FIFO实现2023-12-04 1680

-

为什么异步fifo中读地址同步在写时钟域时序分析不通过?2023-10-18 1684

-

基于Verilog的同步FIFO的设计方法2023-08-31 1654

-

同步FIFO设计详解及代码分享2023-06-27 3283

-

一个简单的RTL同步FIFO设计2023-06-14 872

-

FIFO设计—同步FIFO2023-05-26 2410

-

同步FIFO之Verilog实现2022-11-01 3125

-

华秋PCB专业设计分析软件-BOM智能分析2021-07-21 1108

-

可靠性设计分析系统2017-12-08 5361

-

异步FIFO的设计分析及详细代码2017-11-15 9329

-

VHDL实用电路模块设计分析2011-03-02 924

全部0条评论

快来发表一下你的评论吧 !