SAR ADC的基本原理是什么?

模拟技术

描述

今天我们来学习SAR ADC喽。逐次逼近寄存器型模数转换器(Successive-Approximation Analog to Digital Converter),是一种常用的A/D转换结构,其较低的功耗表现,还不错的转换速率,在有低功耗要求(可穿戴设备、物联网)的数据采集场景下广泛应用。

逐次逼近,顾名思义,多次转换和Bit计算中,A/D数字码输出逐渐逼近输入值。其算法核心就是“二分搜索(Binary Search)”,该算法能够高效快速的接近目标值。

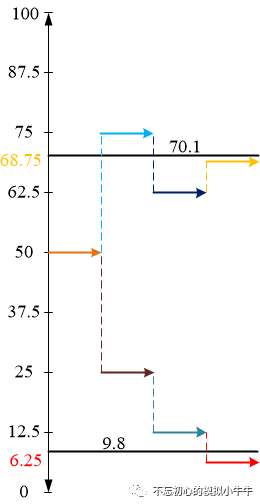

举例说明,假如要请您猜测一个0~100范围内的被猜实数,您的每一次猜测,您只能得到猜测值和被猜实数的比较结果,“高了”或者“低了”的答复。请在有限的猜测次数后,得到最接近被猜测实数的猜测值。该过程可以用如图2所示的猜测过程来表示。

图2

在图2中,两个被猜实数分别为9.8和70.1。可以看到使用二分搜索的方式,第一步确定被猜实数是否大于50,根据第一次的猜测结果,决定下一次二分搜索的区域。通过4次判断,最终得到了6.25和68.75的猜测结果。这也是有限次数误差较小的一种猜测。

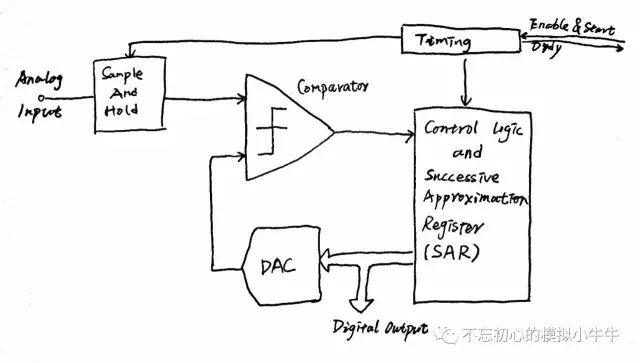

对于SAR A/D来说,其输出是二进制的数字码,结合图2的猜测过程,我们可以看到,二分搜索的过程需要首先确定MSB(Most Significant Bit)位的值,依次向低位搜索,直到LSB(Least Significant Bit)得到确定,其中需要有数字码到其代表的离散模拟量的转化过程(DAC实现),被猜测实值(模拟输入)和数字码对应的离散模拟量的判断(比较器实现)。其功能框图如图3所示。其中还包含了对输入的采样保持部分,控制逻辑及逐次逼近所需的数字电路部分。

图3

注意图2中用于和猜测结果比较的基准,等效为图3中DAC的输出。其输出结果的准确程度和均匀程度会直接影响到SAR ADC整体的性能, 因此需要选择合适的DAC架构实现。

目前常见的开关电容DAC,又称电荷再分配DAC。电容匹配精度仅受工艺过程中的光刻精度影响,容易实现SAR ADC精度和线性度的要求。该结构还有如下优点,将DAC和采样保持部分融合为一体,简化了电路的复杂度。

图4

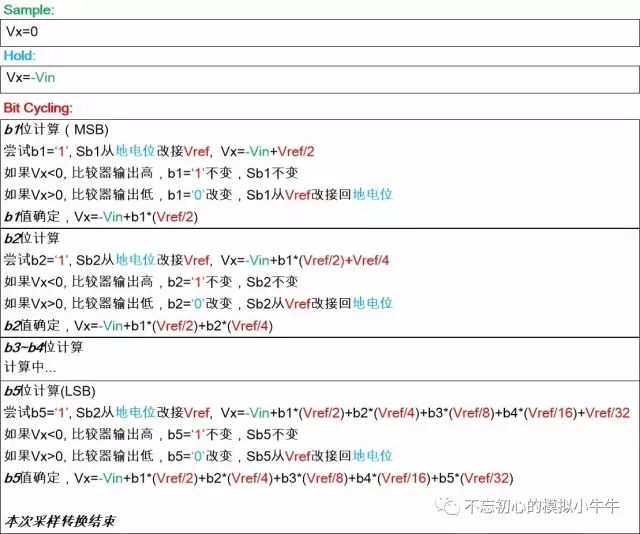

一个简易的4bit电荷再分配结构及工作过程如动图4所示。其中电容容值以2^N比例形式排列,b1~b5依次为最高位到最低位。其中Sample Phase用于采样输入信号,Hold Phase是采样完毕,等待转换的阶段,此过程结束后,输入电压Vin以电荷的形式存储在二进制排列的电容上。Bit Cycling是过程为逐比特确认的过程。各阶段Vx节点电压及逐比特计算的过程如图5所示。

图5

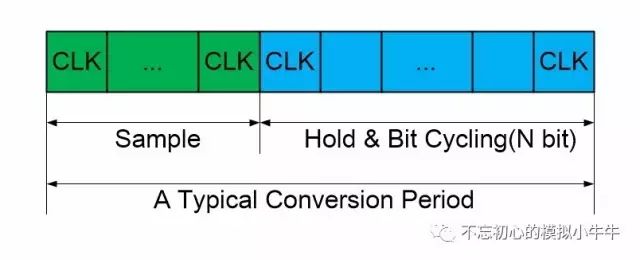

Sar ADC典型的时序如图6所示,通常对输入信号的采样Sample需要多个时钟周期,具体所需时间为受分辨率影响,采样后输入信号建立误差应小于1/2 LSB。保持Hold和转换过程,需要N个时钟周期,如果存在校准的过程,则需要更多的时钟周期。

图6

好了,这期的内容就先到这里了。

审核编辑:刘清

-

sar adc基本原理基础学习2023-09-14 1191

-

Σ-ADC拓扑背后的基本原理的基本知识2023-01-23 2734

-

SAR切换电容ADC的基本原理2022-11-01 2420

-

AD转换基本原理是什么2022-02-18 1125

-

步进马达基本原理2021-11-30 1853

-

PIC16F15323单片机的基本原理2021-11-24 769

-

ADC基本原理是什么?通道类别有哪些?2021-11-18 2732

-

模数转换器(ADC)的基本原理是什么?2021-09-28 2968

-

无线充电的基本原理是什么2021-09-15 2675

-

ADC的基本原理是什么2021-08-02 1691

-

线性电源的基本原理是什么2021-07-30 2203

-

模数转换器(ADC)的基本原理是什么2021-07-26 1775

-

Sigma-Delta ADC的基本原理及性能指标是什么?2021-06-22 3428

-

并行编码模数转换器(ADC),ADC的基本原理2010-03-24 3356

全部0条评论

快来发表一下你的评论吧 !