瑞萨电子RZ/V2系列MPU简介

描述

RZ/V2系列MPU简介

RZ/V2系列是一种内置瑞萨电子独家硬件加速器 “DRP(Dynamically Reconfigurable Processor,动态可配置处理器)-AI”的AI专用微处理器(MPU)。DRP-AI专为嵌入式机器视觉类AI/ML(Machine Learning)应用优化设计,可提供实时AI推理和图像处理功能,同时兼具了高AI推理性能和低功耗特性,家族化产品支持0.4~80TOPS不等的可扩展AI算力,为资源(如电池容量、空间等)有限的嵌入式端侧AI应用提供差异化有竞争力的解决方案。

家族产品概览

RZ/V2 AI-MPU家族产品概览

按照性能划分

RZ/V系列有三大子系列产品:

1入门级RZ/V2L,配备软ISP和3D图形引擎,可应用于基础的分类、目标检测、人脸识别等应用,主要规格如下:

2 x Cortex-A55,最高主频1.2GHz,支持NEON/FPU

专用DRP-AI硬件加速单元,软ISP(DRP库)

500-MHz Arm Mali-G31 3D图形引擎,GPU支持库:OpenGL ES1.1/2.0/3.0/3.1/3.2,OpenCL 2.0

支持MIPI-DSI或RGB888显示输出,最高支持1920 × 1080显示分辨率

硬件VCP,支持H.264/ AVC编码和解码,支持高达FHD (1920 x 1080) x 30fps处理

支持MIPI-CSI或DVP camera输入

千兆以太网、USB2.0、双CAN-FD接口,ADC,最多7路UART

2中端RZ/V2M子系列包括RZ/V2M和RZ/V2MA两款产品,可用性能需求更高的目标检测、姿态估计、OpenCV加速应用,主要规格如下:

2 x Cortex-A53,最高主频1.0GHz,支持NEON/FPU

专用DRP-AI硬件加速单元,加速卷积神经网络处理,或OpenCV加速

MIPI-CSI输入,4K/30fps高性能ISP(仅RZ/V2M)

MIPI-DSI,HDMI显示输出,最高支持1920 × 1080显示分辨率(仅RZ/V2M)

硬件VCP,支持H.265/HEVC编码和解码,H.264/ AVC编码和解码,最高3840 × 2160p × 30fps编码, 3840 × 2160p x 30 fps解码(仅RZ/V2M)

千兆以太网、USB3.1、PCIe高速接口

3高性能RZ/V2H子系列(将于2023年MP),提供8~80TOPS强劲算力,可应用于支持更复杂的语义分割(避障或定位)、空间物体捕捉、行为预测等应用,主要规格如下:

4 x Cortex-A55,最高主频1.8GHz,支持NEON/FPU

专用DRP-AI硬件加速单元,4K/30fps高性能ISP

500-MHz Arm Mali-G31 3D图形引擎,GPU支持库:OpenGL ES1.1/2.0/3.2,OpenCL 2.0

MIPI-CSI Camera输入,最多8路

MIPI-DSI显示输出,最高支持FHD(1920 × 1080p)x 60fps显示分辨率

硬件VCP,支持H.265,H.264编码和解码,最高4K x 30fps 编解码

千兆以太网、USB3.2、PCIe、CAN-FD等接口

DRP-AI作用和优势

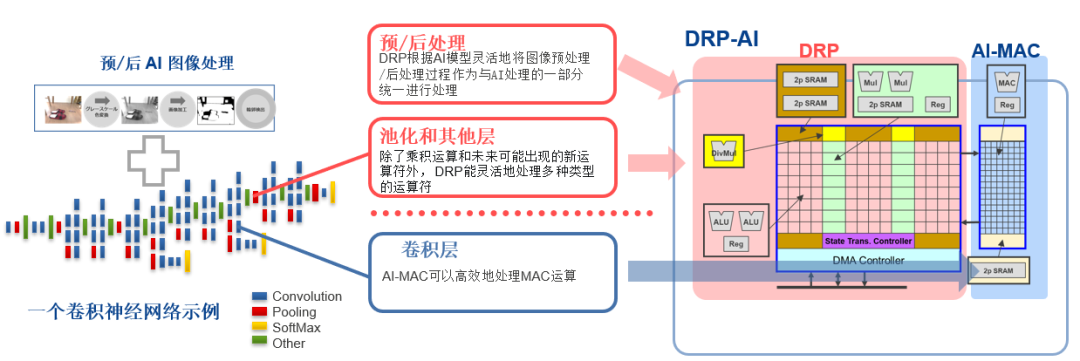

DRP-AI对DL(Deep Learning)卷积神经网络具有非凡的加速效果,同时兼具了高AI推理性能和低功耗特性,主要原因在于:

1DRP独特架构:集成专用AI-MAC单元和DRP两部分专用IP。端到端AI推断由DRP-AI单元单独处理,无需任何CPU介入处理

2大部分前/后处理由DRP的流水线处理完成

3最高的MAC操作利用率

4通过集成Buffer内存尽可能地减少了与外部DRAM数据交换

DRP-AI的开发流程

同市场上其他主流机器学习硬件加速器,DRP-AI的开发流程包括AI包括学习(训练)和推理两个环节。差异点在于,瑞萨将提供免费的DRP-AI模型转换工具,将目标代码转换成可识别的代码,部署到RZ/V嵌入式平台。

审核编辑:汤梓红

-

瑞萨RZ/A系列微处理器(MPU)简介2023-09-15 2713

-

瑞萨电子推出支持入门级AI应用设计的全新RZ/V2L MPU2021-05-24 3268

-

瑞萨电子高端微处理器(MPU)RZ系列介绍2023-09-01 1988

-

瑞萨RZ/G系列MPU简介2023-09-11 2835

-

瑞萨RZ/V系列产品介绍2024-01-16 2573

-

瑞萨电子推出功能强大的单芯片RZ/V2H MPU2024-03-08 2221

-

产品详解 | 瑞萨电子RZ/T2M MPU2024-03-13 2497

-

产品详解 | 瑞萨电子RZ/T2L MPU2024-03-21 2456

-

产品详解 | 瑞萨电子RZ/N2L MPU2024-04-20 3600

-

产品简介 | RZ/G2系列MPU2024-04-29 1623

-

产品简介 | RZ/V2系列MPU2024-05-08 1768

-

瑞萨电子RZ/N2L MPU产品介绍2024-12-19 2416

-

瑞萨电子RZ MPU家族精品RZ/N2L产品介绍2024-12-23 1925

-

瑞萨新款RZ/V2N视觉AI MPU产品介绍2025-03-27 1868

-

盟通科技基于瑞萨RZ MPU的EtherCAT主站应用方案2025-11-21 1577

全部0条评论

快来发表一下你的评论吧 !