基于Xilinx FPGA的边界扫描应用

描述

上一篇文章,介绍了基于STM32F103的JTAG边界扫描应用,演示了TopJTAG Probe软件的应用,以及边界扫描的基本功能。本文介绍基于Xilinx FPGA的边界扫描应用,两者几乎是一样。

1. 获取芯片的BSDL文件

FPGA的BSDL文件获取方式,可以参考之前的文章:BSDL文件获取。 以Xilinx Kintex-7系列FPGA XC7K325T为例,可以在BSDL Library网站获取,或者在ISE、Vivado的安装目录获取,

D:ProgramXilinx14.7ISE_DSISEkintex7data D:ProgramXilinxVivadoVivado2018.3ids_liteISEkintex7data

2. 硬件连接

首先需要准备好以下硬件:

JTAG调试器,如JLink V9标准版

一块FPGA板子,如Xilinx XC7K325T

Xilinx的JTAG接口和Jlink的JTAG接口线序不一致,需要使用单独的杜邦线分别连接TCK、TMS、TDI、TDO和VREF、GND信号。

3. 边界扫描测试

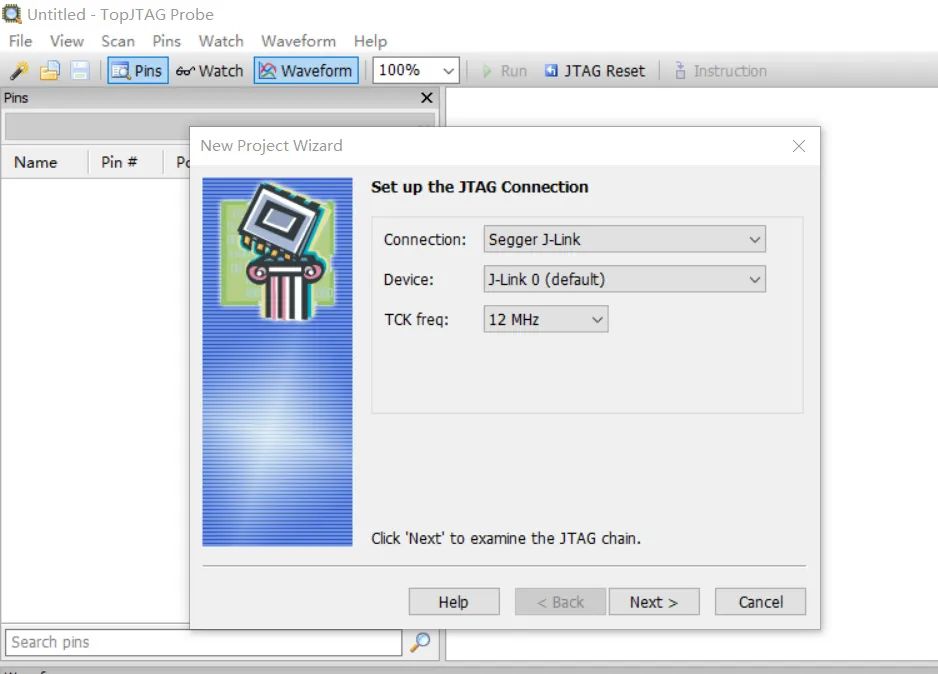

打开TopJTAG新建工程,选择JTAG设备为JLink

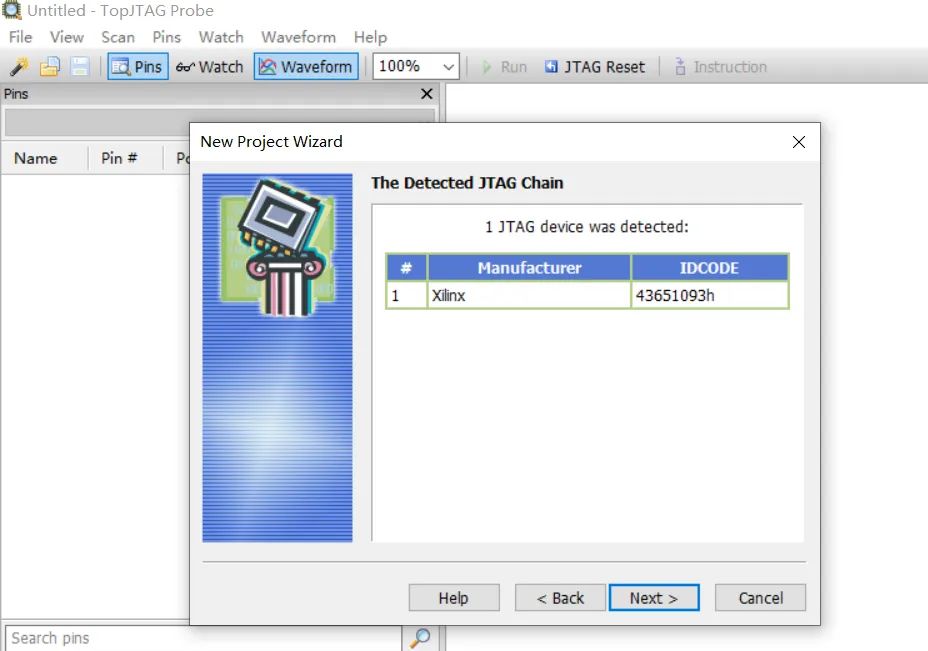

如果连接正常,会显示当前连接芯片的IDCODE

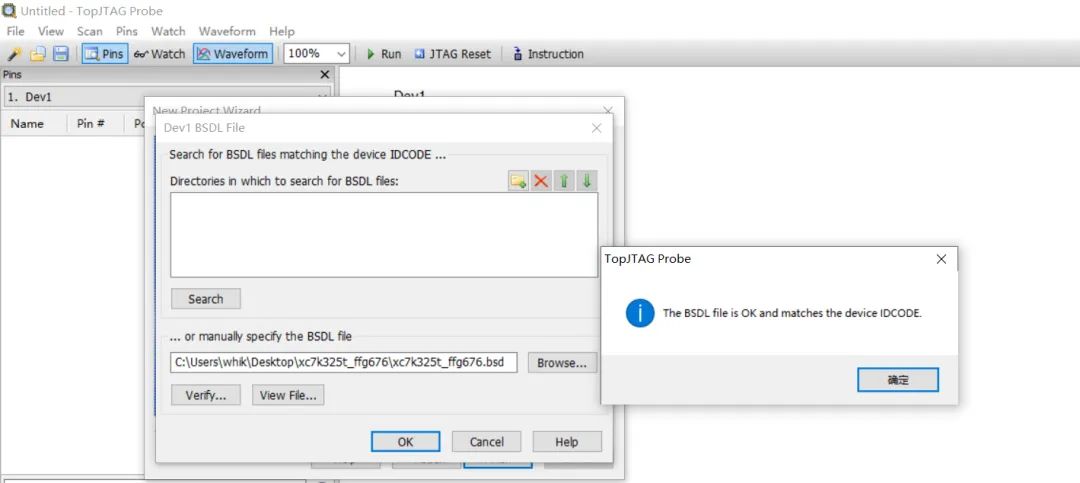

指定BSDL文件路径,并进行IDCODE校验。

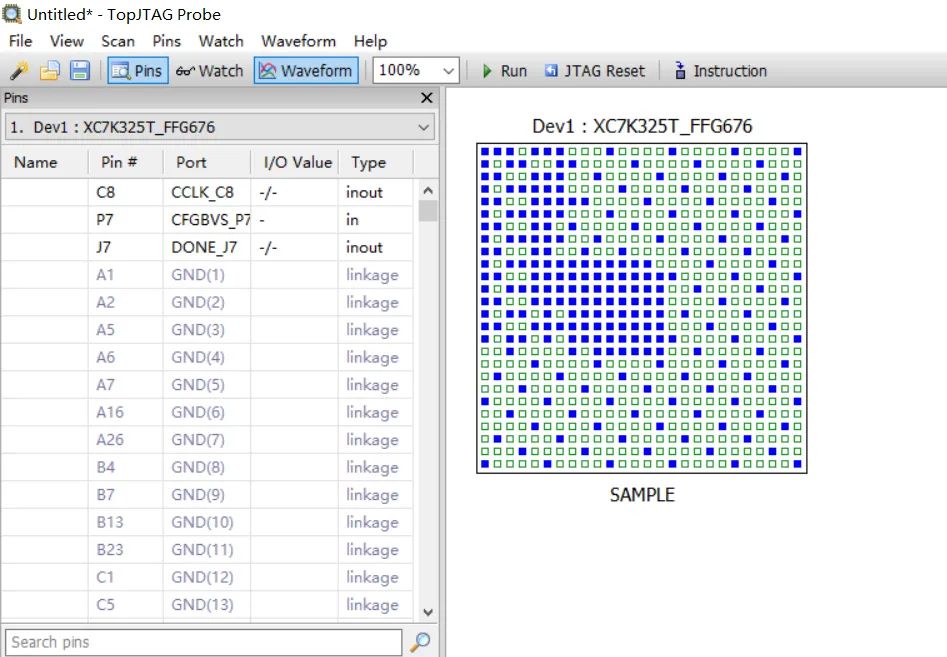

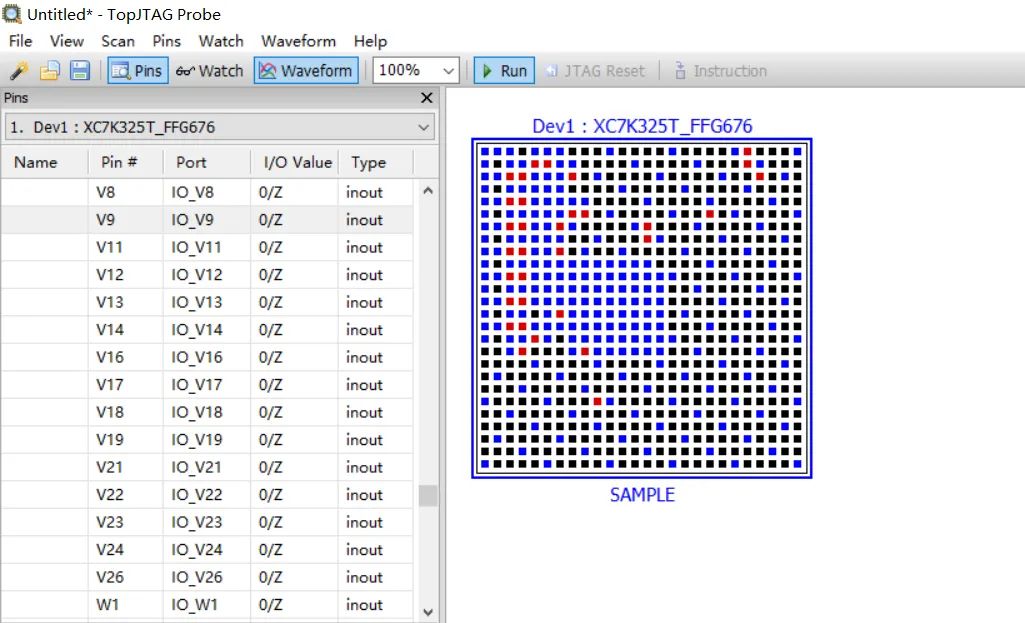

初始状态为stop状态,

初始默认为Sample状态,点击RUN按钮,就可以看到所有管脚的实时状态,黑色的是电源管脚,黑色的是高电平,蓝色的是低电平。闪烁的说明当前为高低电平翻转状态。

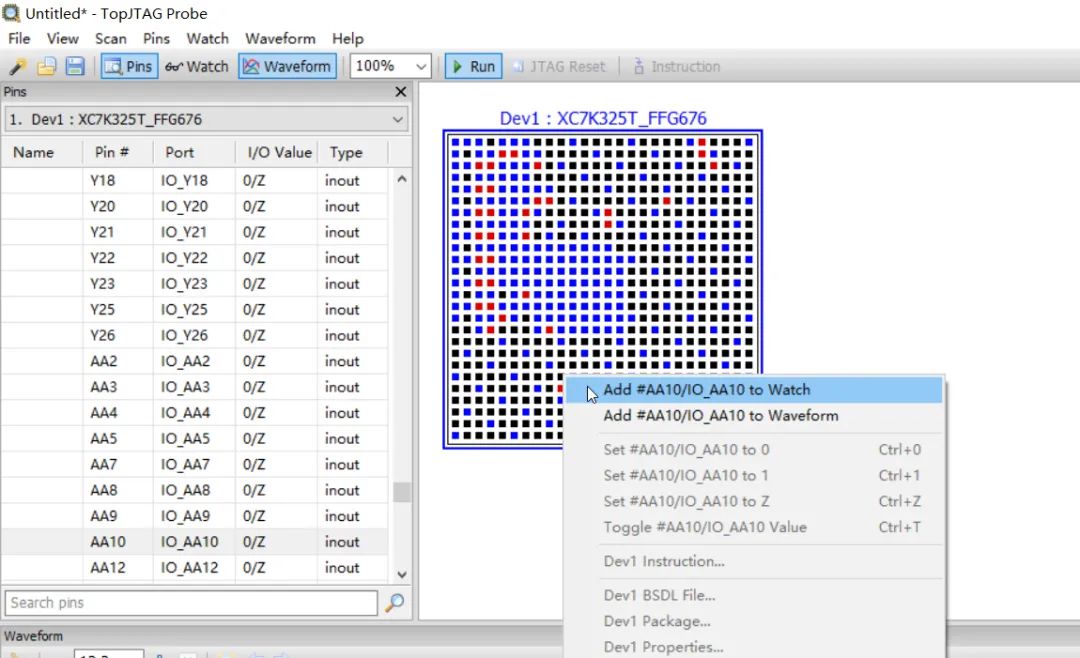

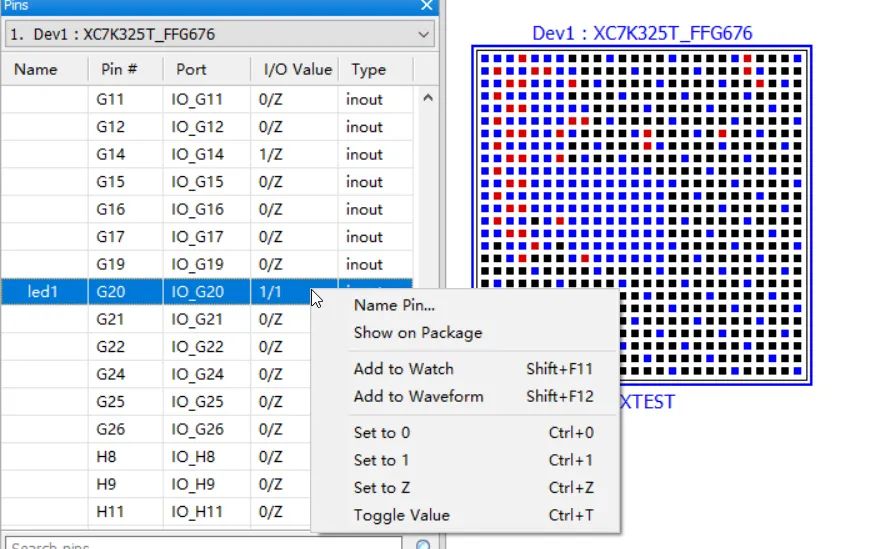

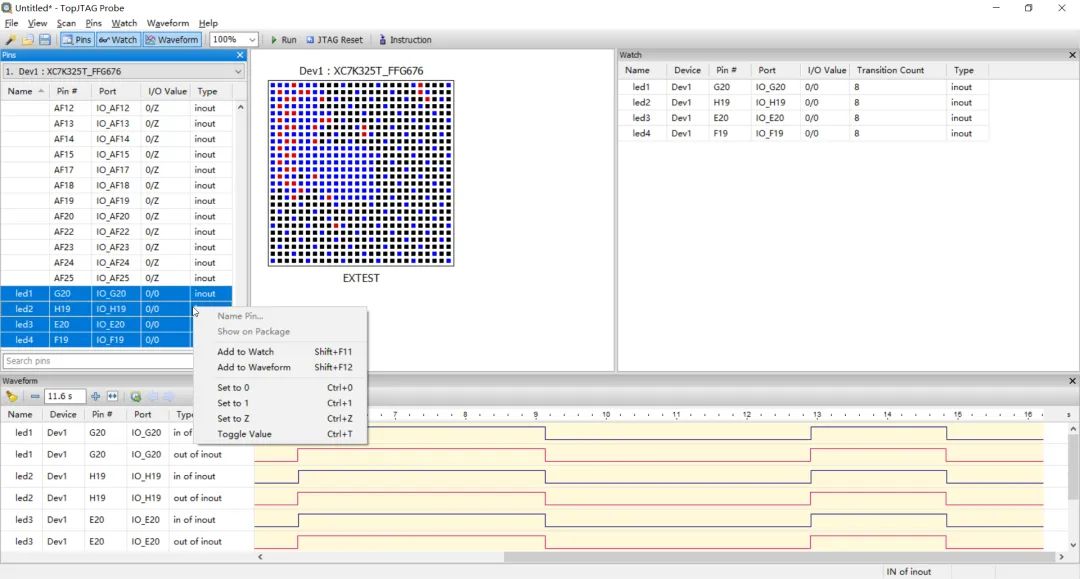

在左侧Pins窗口或右侧芯片视图,选择一个芯片管脚,右键,可以选择添加到Watch窗口或Waveform窗口

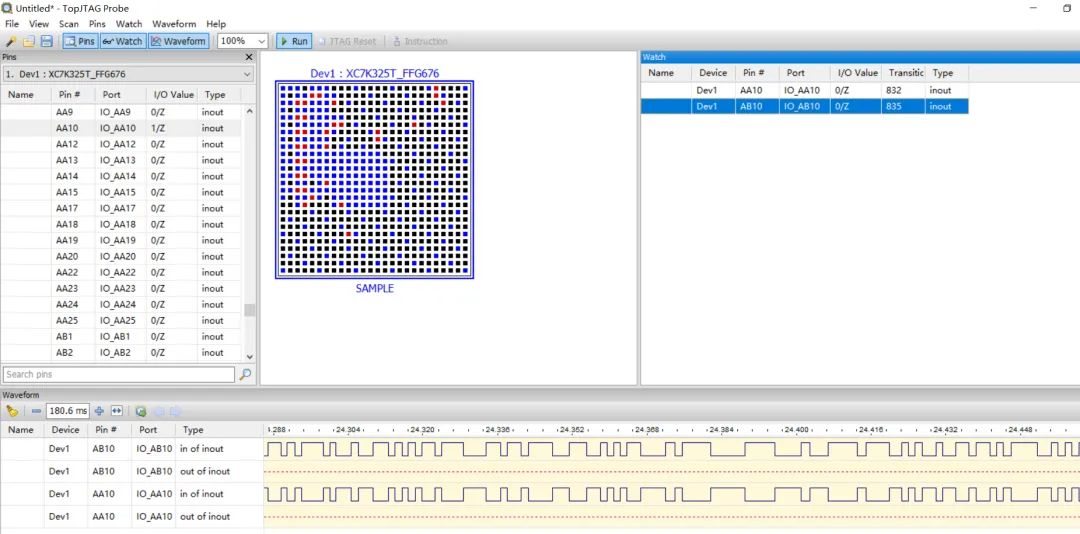

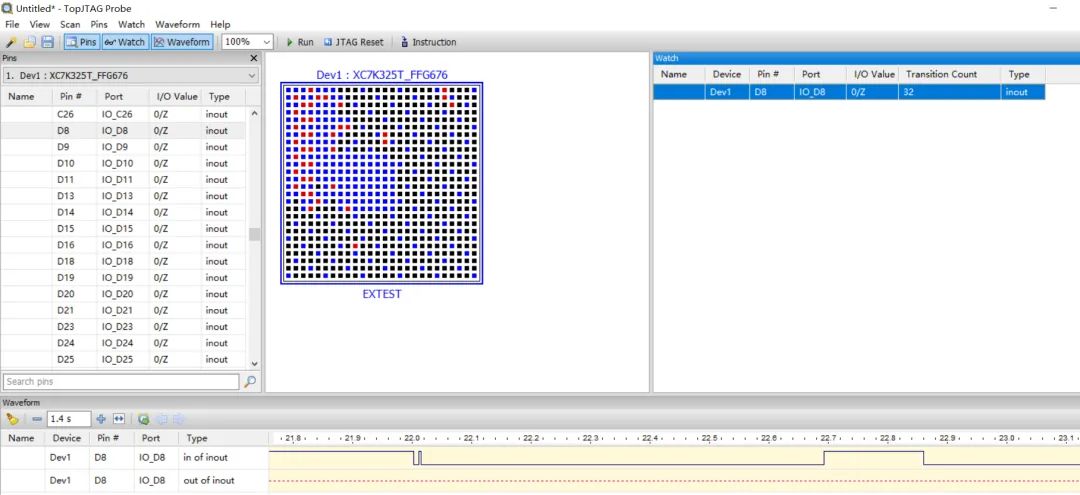

Watch窗口可以看到管脚实时状态,并且可以统计电平翻转的次数,Waveform窗口可以显示实时的波形。

Waveform支持放大、缩小、暂停等基本操作。

Pins窗口,选择一个管脚右键之后,可以进行命名,输出高、低电平或高阻状态。

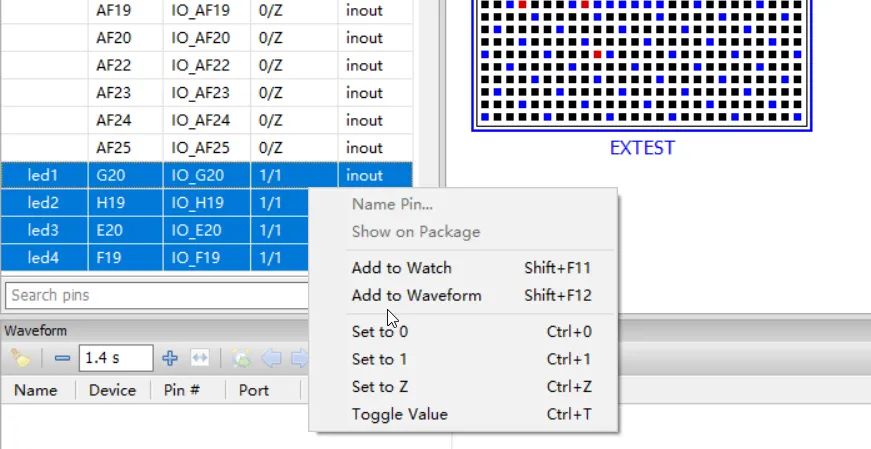

支持多选之后,批量控制电平状态

支持多选之后,批量添加到Waveform窗口

4. 总结

和单片机不同,大多数FPGA芯片都是BGA封装的,管脚个数从200至1000不等,这也就意味着需要多层PCB来进行硬件设计,密集的引脚和PCB的内层走线,会导致故障的排查越来越困难,通过边界扫描,可以方便、快捷的判断出故障点,在产品研发、生产、测试阶段可以大大提高效率。

审核编辑:汤梓红

-

什么是边界扫描?JTAG边界扫描测试方案介绍2023-09-22 6368

-

FPGA边界扫描模式可以串接两个FPGA吗2014-03-24 2637

-

请问什么是边界扫描?2019-07-01 4559

-

如何利用SOPC设计一款便携式边界扫描故障诊断仪?2021-04-12 1402

-

边界扫描测试技术介绍2022-02-17 1240

-

边界扫描测试技术在硬件实验中的应用2009-08-18 802

-

应用于FPGA的边界扫描设计2009-12-14 525

-

边界扫描与电路板测试技术2006-03-11 2180

-

基于USB总线的边界扫描测试系统2011-07-04 846

-

边界扫描测试的原理及应用设计2016-02-16 659

-

简述BSDL边界扫描语言,BSDL边界扫描语言的应用2017-04-19 9508

-

边界扫描测试的基本原理及其测试系统的设计2017-12-01 1357

-

边界扫描技术的详细资料描述2018-12-04 1295

-

JTAG(四) 边界扫描测试技术2021-12-20 1112

-

边界扫描测试软件XJTAG和TopJTAG介绍2023-09-11 5692

全部0条评论

快来发表一下你的评论吧 !