核间通信(IPC)的目标和实现机制

描述

目前很多芯片都会有几个core核,有的是CortexM0+、M4、M7、A53、A73等等,有的有着2核、3核、4核甚至6核8核,不同的核的主频支持度不一样,适用的具体应用场景也不同,因此需要IPC(Inter-processor communication)来核间通信,进行数据的交互。

核间通信(IPC)的主要目标是:充分利用硬件提供的机制,实现高效的CORE间通信;给需要CORE间通信的应用程序提供简洁高效的编程接口。

根据所使用的硬件特性,核间通信的实现机制有:

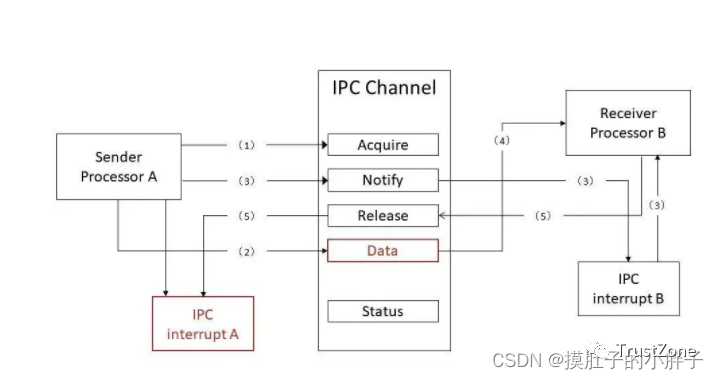

• ·Mailbox中断

• ·基于共享内存的消息队列

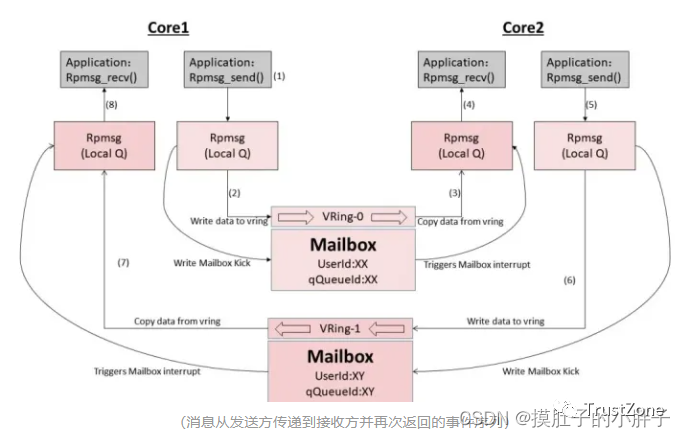

封装-VRING-解析的过程:1、应用程序向给定目的地(CPU、端点)发送消息

2、消息首先从应用程序复制到两个CPU之间使用的VRING。此后,IPC驱动程序在硬件邮箱中发布 VRING ID。

3、这会触发目标 CPU 上的中断。在目标 CPU 的 ISR 中,它提取 VRING ID,然后根据 VRINGID 检查该 VRING

中的所有消息。

4、如果收到消息,它从VRING中提取消息并将其放入目标RPMSG端点队列中。然后触发在此 RPMSG端点上阻止的应用程序。

5、应用程序处理接收到的消息,并使用相同的RPMSG 和VRING 机制在相反方向回复发送方CPU。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SoC的核间通信机制—mailbox介绍2023-08-11 9224

-

关于AM5728核间通信方式(共享内存)问题2018-05-15 9720

-

关于C6678核间IPC通信的问题2018-08-03 3092

-

IPC核间通信测试配套IPC例子的PDF文档里的核间通信时间比我测试的少了4个数量级,请问是什么原因?2018-08-07 1659

-

【创龙TMS320C6678开发板】关于多核间通信2018-12-05 5416

-

核间通信(IPC)解决方案2022-11-03 1946

-

一种基于Mailbox核间机制的多核处理系统2017-11-22 13449

-

在OMAPL138的ARM核与DSP核上实现TL IPC双核通信开发2020-08-06 1936

-

Jacinto7 TDA4VM处理器的核间通信解决方案2022-07-01 9897

-

Jacinto™︎ 7核间通信解决方案2022-10-28 672

-

Jacinto 7核间通信解决方案2023-03-16 2080

-

进程间通信的机制有哪些2023-07-21 1848

-

SoC核间通信的实现机制之mailbox中断2023-09-05 3445

-

核间通信可能的实现机制2023-09-13 2169

-

如何实现一套linux进程间通信的机制2023-11-10 1338

全部0条评论

快来发表一下你的评论吧 !