异常、陷阱和中断有什么区别呢?

电子说

描述

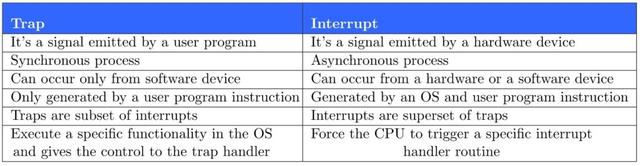

异常和中断会暂停程序以响应硬件或软件中的意外事件。中断是异步事件,异常是同步事件,但是中断和异常之间的区别也取决于具体情况。例如,x86 机器和 ARM 处理器之间以及 CISC 和 RISC 处理器之间的定义不同。

本常见问题解答首先概述了中断的一般定义和各种类型的异常,然后比较了几种计算环境中定义的差异以及如何优先处理中断。

异常有时被称为“陷阱”,可以由执行函数时进程中的异常或错误触发。除零、断点或无效内存访问等情况与程序的执行同步发生。它们可能会导致异常,从而改变处理器的操作。一旦异常原因得到处理,处理器就会返回到之前的活动。另一方面,中断是异步发出的并且可以随时到达。例如,用户击键的产生会启动中断。

异常是软件驱动中断的子集,而中断可以源自软件或硬件源。当异常发生时,异常处理程序执行异常类型定义的特定功能。同样,中断会触发处理器的特定例程,例如在击键到达时及时处理它们。

在基本层面上,异常(陷阱)被定义为源自软件的同步事件,而中断是由外部硬件引起的异步事件。

在 MCU 中,中断可以指示硬件设备中需要及时关注的电子或物理变化。中断用于实时计算以支持多任务处理。大多数 MCU 都是中断驱动设备。MCU 中的特定总线控制线通过 INT 引脚处理中断的接收。

INT引脚连接多个外部设备,例如键盘;网络互连卡、USB 接口等。中断控制器通知处理器哪个设备发出中断,使处理器能够执行必要的中断处理程序。在某些情况下,中断会导致 CPU 开始执行中断向量表中具有特定指令的代码。中断可能源自硬件、软件或其他处理器 (图 1) 。另一种对中断进行分类的方法是按来源分类:

- CPU内部触发异常

- 由外部硬件设备触发的中断

- 由软件源触发的中断。

- 处理器间中断由多任务或实时计算环境中的不同CPU 触发。

中断可能源自外部硬件、处理器或另一个处理器(在多核环境中)或软件。

有时根据情况的严重程度将异常分为两类:

中止会停止代码执行,直到条件得到处理为止,并且中止是由硬件故障、被零除错误等重大问题引起的。

陷阱需要被处理,但不会阻止代码执行,并且用于虚拟内存管理、程序调试和类似功能。

处理中断

异常或中断处理通常分为三个阶段:

- 当处理器识别出异常的来源时,就会发生“识别”。

- 当处理程序控制指令执行、保存上下文并且处理程序例程开始在管理员模式(有时称为特权状态)下运行时,将“发生”异常或中断。

- 异常或中断“处理”发生在管理程序模式下,并持续到处理器恢复执行程序代码为止。

定义不同

中断可以分为异常、陷阱、故障和中止,但事情并没有那么简单。这取决于上下文和所考虑的特定平台。在各种环境中,“陷阱”可以指任何中断、软件中断或同步软件中断。此外,该术语仅适用于由名称中带有“trap”的指令产生的中断或启动监视程序或调试器的断点。中断在 x86 和 ARM 环境中具有不同的分类。

在x86环境中,存在硬件中断和软件异常,分为三种不同类型:故障、陷阱和中止。x86 环境中的中断由任何 I/O 设备异步触发。当程序被“中断”时,它可以重新启动而不会丢失功能。“故障”也会导致可重新启动的情况,但它是与软件执行相关的同步事件。“陷阱”就像一个错误,但具有不同的返回地址。在陷阱中,返回地址指向陷阱指令之后要执行的指令,而在故障中,返回地址指向出错的指令。陷阱通常用于系统调用。“中止”是由严重错误引起的,并且通常不允许程序重新启动。

在 ARM 架构中,术语“异常”可用于指代所有类型的中断。在这种情况下,异常被分类为硬件中断、复位、异常生成指令和中止。ARM MCU 中的中止包括数据中止(数据访问失败)或指令中止(指令读取失败),也称为预取中止。虽然 x86 环境中的“异常”是同步事件,但它们在 ARM 环境中可以是同步或异步的。此外,ARM“异常”可以是精确的,也可以是不精确的(如下一节中定义)。

RISC差异

与 CISC 架构相比,RISC MCU 采用不同的方法来处理中断或异常。对于设计人员来说,这些差异最初可能比 x86 和 ARM 架构之间的差异更具挑战性。RISC 机器识别四种类型的异常:

- 异步精确和不精确

- 同步精确、非精确

与其他情况一样,异步异常可以随时发生,而同步异常则与指令流同步。精确例外和不精确例外概念的引入是一个重要的区别:

- 精确异常具有精确定义的原因,并且通常是可恢复的。

- 不精确的异常是不可恢复的,意味着处理器无法继续执行程序,通常会导致灾难性的故障。

同步精确是指令异常的结果。根据具体原因,保留出错指令或下一条指令的地址,以供异常处理后使用。异常处理程序确定错误指令是否部分或全部完成,并确定应如何处理它。

同步不精确异常用于 RISC-V 处理器,但在 PowerPC 设备中并不完全支持。同步不精确异常处理是针对 PowerPC 架构中的特定浮点异常定义的。同步不精确异常的一般概念将来可能会得到更全面的实现。

异步精确有时称为“可屏蔽”,可能由外部中断、递减器故障、系统管理中断、热管理中断等引起。在异步精确异常期间,异常之前正在处理的指令在异常处理之前完成。当异常被清除时,下一条指令被存储并执行。由于这些异常是由外部设备引起的,因此在处理任何给定异常之前,可能会同时或快速连续发生多个异常。如果异常处理程序中的存储空间不足,则可能会错过某些异常。解决这个潜在问题的一种方法是在异常处理程序和外部设备之间包含某种形式的握手,以确保所有异常都已被接收和确认。

异步不精确,有时称为“不可屏蔽”,例外情况仅包括系统重置和机器检查。当系统复位发生时,CPU停止,所有内部存储器和寄存器复位,然后处理器重新启动。机器检查异常是当CPU检测到处理器本身、内存、I/O设备或系统总线中的硬件错误时发生的计算机硬件错误。对于 PowerPC 设备,软件错误(例如某些无效的内存访问)也可能导致机器检查异常。大多数机器检查异常都会停止操作系统并需要重新启动才能恢复操作。

识别 RISC 异常

当指令不按程序顺序执行时,异常识别尤其具有挑战性。例如,PowerPC 按照严格的程序顺序处理同步异常,即使程序流中后续的指令可能已生成了附加异常。第一个异常的处理就像前面的指令已全部执行而后面的指令尚未执行一样。

当然,多个异常可以同时发生。在这种情况下,将根据特定优先级处理异常。异步不精确异常具有最高优先级,在此类别中,系统重置异常的优先级高于机器检查异常。接下来是按程序顺序处理的同步精确异常,然后是同步不精确异常。异步精确异常的优先级最低,外部中断的优先级高于内部中断(例如递减器和系统管理中断)。

当多个异常同时发生时,RISC 器件具有严格的异常处理优先级。

概括

在基本层面上,异常被分类为中断的子集。更具体地说,异常是源自软件的同步事件,而中断被定义为由外部硬件引起的异步事件。中断和异常的定义因 x86、ARM 和 RISC 等计算架构而异。异常和中断的各种原因在中断系统操作方面具有不同的严重程度。因此,要根据具体情况制定严格的优先顺序。

-

数字地与模拟地有什么区别呢?2011-09-26 9719

-

请问事件请求与中断请求有什么区别?2019-06-28 3810

-

STM32中断的分类不同组之间有什么区别呢2021-08-13 1341

-

一文读懂中断方式和轮询操作有什么区别吗2021-12-10 2730

-

什么是中断?系统异常和外部中断有什么区别2022-01-07 940

-

vitis和vivado有什么区别和联系呢?2023-10-16 1166

-

51的内部中断源与外部中断源有什么区别?2023-11-08 551

-

中断、异常和系统调用2011-11-03 422

-

FPGA和单片机有什么区别呢?2017-02-11 43434

-

hdcp和hdmi有什么区别2017-12-17 21101

-

hdmi与vga有什么区别2019-01-24 40291

-

RTOS和 TSOS有什么区别?2020-03-12 5849

-

单片机中断与CPU的轮询有什么区别2020-06-29 4233

-

type-c和普通接口有什么区别呢?2023-07-28 8436

-

AIGC和AI有什么区别2025-02-20 2332

全部0条评论

快来发表一下你的评论吧 !