NFC电路匹配实例 NFC电路原理图和PCB设计

描述

NFC电路匹配实例

很多朋友后台私信我,要有一个手把手的实例演示就好了,刚好一个智能锁的项目,刷卡距离只有3mm左右,需优化刷卡距离.这次调试记录了调试过程的所思所想,欢迎批评指证.

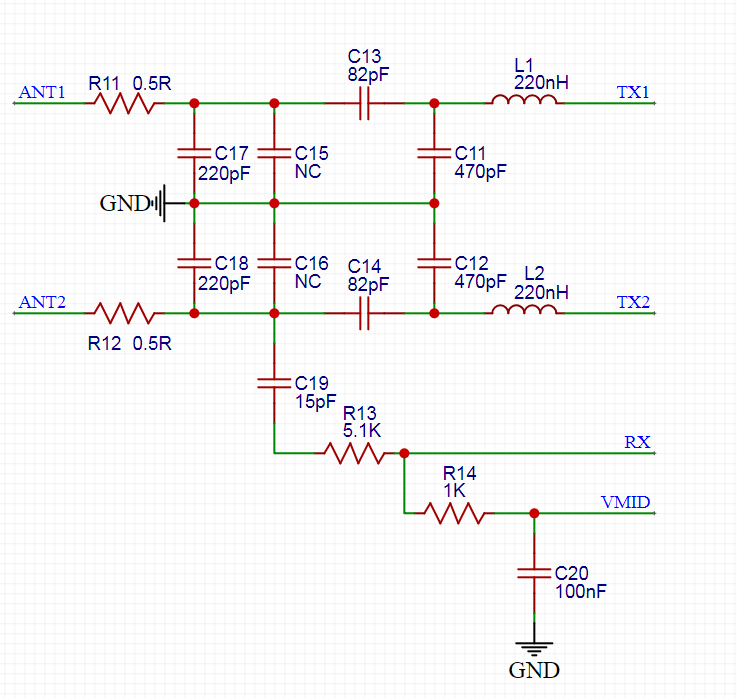

一.NFC电路的原理图和PCB

二.开始调试

调试步骤如下:

1)确定NFC芯片最佳工作阻抗

2)设计天线线圈,测量天线线圈的等效电路参数

3)根据Q值或带宽要求确定串/并联电阻的阻值,后多时候,用串联电路就可以了, 并联电路 是串联电路的转换,文章只对串联电路进行说明.

4)根据需要滤除的高次谐波分量,确定LC结构EMC滤波器 的截止频率,计算EMC滤波器的L、C值

5)计算阻抗变化电路中的电容容值实现共轭匹配

6)实际测试与参数调整

1.确定NFC芯片最佳工作阻抗

本次调试的项目NFC用的是FM5114B,从规格书中,未能找到TX1,TX2的阻抗,通过电话联系FAE,才告知,TX1,TX2两端的阻抗为25R左右,并发了一份参考文档,也是要求在simth圆图的25R附近.

2.设计天线线圈,测量天线线圈的等效电路参数

在测试量之前网分要先较准,并且补偿射频馈线的时延,去掉C17,C18,断开C13,C14,在C13,C14的左侧焊接馈线.测试数据如下:

本测试测试,用的是lite VNA,

天线数据:1.92+j80.44R

由此Q=80.44/1.92=41.89

这个天线的电阻有点大啊!这个NFC的天线和控制芯片是通过接口座相连接的,可能和这里有关系,多次测量还是这个结果.

Q值在42左右,还是可以的,需不需调整带宽,到实际测试距离的时候调整,FAE说他家的Q值一般在36左右,***,就是这样,规格书好多参数找不到,靠沟通才能获得.

3.MC滤波器的L、C值

网上LC计算截止频率:

这个值有点小,波电路的截止频率太了,13.56+0.007+0.8475=14.4145MHZ,电容由560PF改为470pf.

4.计算阻抗变化电路中的电容容值实现共轭匹配

1)先测试芯片和滤波电路的阻抗,

取下芯片,在TX1,TX2间焊47/2=23.5R,(我这里没有25R的电阻,)断开C13,C14,在C13,C14的右侧焊网分线,测得如下图:

Z=55.64-j40.33R

2)下面从天线数据:1.92+j80.44R,经过匹配后要得到的数据:Z=55.6+-j40.33R(注意器件的串并联转换)

3)用SIMTH圆图仿真:

先并120PF,再串30pf

4)simth圆图只能作一个调整趋势判断,实际值会与这个有区别:

实际元件值C17,C18焊220pf,才能移到VAN上合适的位置,串82PF,才能接近共轭.

5)验证测试:

a.发现距离已经调到了1.5cm,将串联电阻R11用1R代替,距离有所增加,接近1.8cm

b.所有的值调好后,我们去掉并联的两个47R,测试在没有芯片的情况下,整个链路的阻抗.M2的阻抗为:Z=26.33+j14.38R S11也很不错.

-

3637320230

2025-11-27

0 回复 举报13.56+0.007+0.8475=14.4145MHZ中的0.007和0.8475是哪来的? 收起回复

3637320230

2025-11-27

0 回复 举报13.56+0.007+0.8475=14.4145MHZ中的0.007和0.8475是哪来的? 收起回复

-

PCB原理图与PCB设计文件的区别2023-08-01 7027

-

Cadence高速电路板设计与仿真(原理图与PCB设计) .zip2022-12-30 1913

-

介绍下NFC天线的设计2021-11-11 3148

-

NFC技术 (二) -硬件设计2021-11-06 1635

-

带I2C的NFC标签PCB和原理图资料下载2021-04-14 1059

-

PCB原理图和PCB设计之间的关键差异2020-11-03 14629

-

pcb设计实例讲解2019-04-25 21570

-

Altium Designer 实用宝典—原理图与PCB设计2017-11-29 3319

-

PCB设计与制作——调频收音机电路原理图设计2016-08-16 2821

-

EAGLE电路原理图与PCB设计方法及应用9-10章2016-04-26 1727

-

NFC读卡器原理图与PCB图2015-10-28 13976

-

NFC天线/NFC-SWP天线2013-05-16 6181

全部0条评论

快来发表一下你的评论吧 !