介绍一种IP控制信号的处理方式

电子说

1.4w人已加入

描述

在ASIC/FPGA项目中,我们会用到很多IP,其中有很多IP存在内部控制信号以及内部状态信号。这些控制信号和内部状态信号影响数据流的接收和发送。

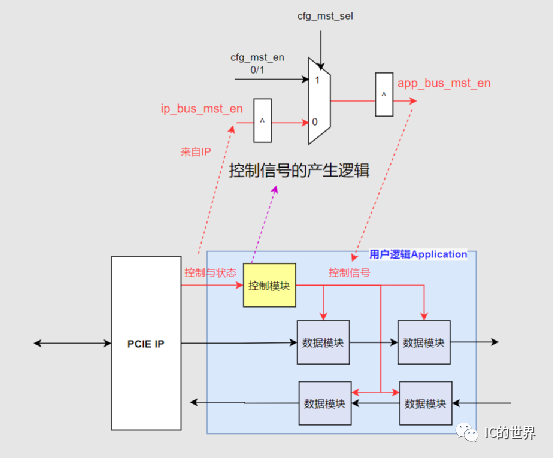

以PCIe为例,蓝色框图部分为PCIe用户侧逻辑,是需要用户实现的逻辑。

左侧白色为PCIe IP,PCIe内部配置空间有一个控制信号,名为bus_master_en(简写),当bus_master_en为0时,不期望用户逻辑发送dma请求(memory读写请求)。

所以在用户逻辑中,我们就需要感知到这些信号的数值,用于控制数据逻辑模块。

通常我们期望这些信号是可控的,能够灵活配置,既给芯片加了一层保障,又方便debug。

即使对IP或者协议的理解有误,也能通过配置规避大部分问题。

那一种很常见的方式就是,添加一个mux,默认情况下,使用ip驱动的控制信号。

如图所示:

ip_bus_mst_en是ip输出的控制信号。

app_bus_mst_en用于控制内部数据模块。

cfg_mst_en和cfg_mst_sel都来自配置csr模块,可灵活配置成0或者1.

cfg_mst_sel默认值为0,表示选择ip_bus_mst_en,在默认情况下,app_bus_mst_en的数据与ip_bus_mst_en相同

这种设计小技巧在IC项目中比较普遍,但是又时常被忘记。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

求助:请问这两种对电源处理方式的区别和它们的用法。2017-07-24 3540

-

按键消抖都有哪些处理方式?2023-11-01 554

-

一种基于SoPC系统的液晶控制IP核设计2009-08-31 432

-

光盘销毁机的处理方式2009-12-31 4377

-

一种处理信号相位误差电路的设计2012-10-10 747

-

另一种方式控制一个舵机2016-03-21 461

-

一种WCDMA基带信号处理方法的研究2017-01-12 1114

-

一种实用的铜电阻测温的信号处理方法2017-01-22 865

-

基于android采用异步处理方式开发移动护理程序的设计2017-10-26 679

-

介绍学习一种模拟信号的处理方式:对数处理2018-01-11 12193

-

【经验分享】系统常用 (电磁兼容)EMC处理方式2018-04-17 1226

-

PCB电镀中异常处理方式2022-08-11 700

-

浅析测力传感器的两种处理方式2021-12-20 1503

-

使用相序识别仪时,常见故障原因以及处理方式概述2023-12-19 2383

-

模数转换器结束信号的四种处理方式2024-02-03 1557

全部0条评论

快来发表一下你的评论吧 !