PCIe相关问题解答

描述

PCIe 设备的数据流有哪些,分别是什么场景?

PCIe 设备的数据流主要为4大类:

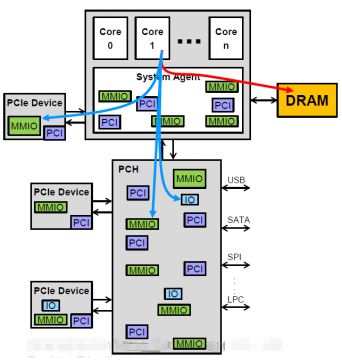

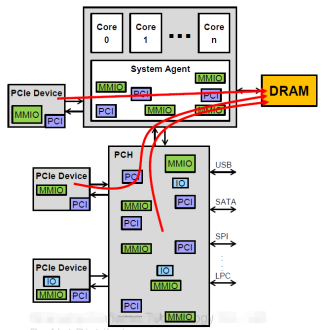

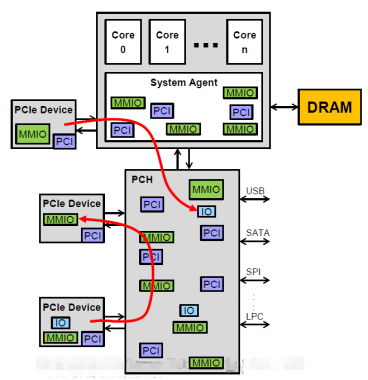

1.CPU 发起的,访问PCIe设备配置空间的数据流。这种数据流主要是BIOS/Linux PCIe driver 对设备进行初始化、资源分配时,读写配置空间的。包括PCIe 枚举,BAR 空间分配, MSI 分配等。 设备驱动通过 pci_wirte_config() / pci_read_config() 发起配置空间访问。 lspci / setpci 也是对应到配置空间访问。

2.CPU 发起的,访问PCIe设备MMIO/IO的数据流。将Bar空间mmap 到系统地址空间后,设备驱动可通过地址访问PCIe 设备的 Bar / MMIO 空间。 一般的,设备会将特定的寄存器和存储实现在MMIO空间内。CPU可使用 iowrite32() / ioread32() 等方式访问 MMIO 空间。这是一种效率较低的PCIe使用方式.

3.PCIe 设备发起的,访问 Host Memory 的 DMA 数据流。这种数据流由PCIe 设备的DMA Engine 发起,是一种常见的、高性能的PCIe 数据流。CPU通过配置 PCIe 设备内的DMA Engine (通过MMIO寄存器),启动设备PCIe DMA。网卡,GPU 等PCIe 设备,数据通路均有PCIe DMA完成。

4.PCIe 设备发起的,访问PCIe设备MMIO/IO的数据流, 亦称P2P (Peer to Peer)。同(3)类似,也是利用PCIe 设备的DMA engine, 但是数据访问的是其他PCIe 设备的MMIO地址空间而非Host Memory. CPU须配置桥片端口路由地址。 GDR (GPU direct RDMA) 就是利用这种数据流,避免主机内存的数据拷贝。

CPU访问设备内存(Bar空间)和访问主机内存,有什么不同?

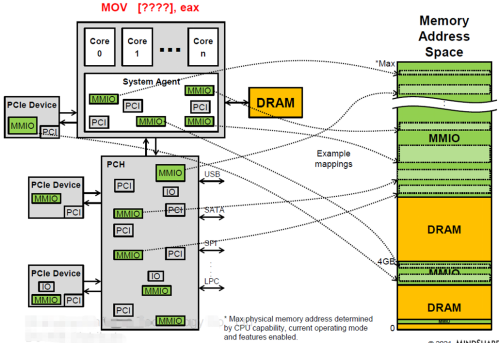

Prefetchable MMIO 映射到系统地址空间后,软件可以通过地址对PCIe MMIO空间进行直接访问(CPU使用MOV指令),这一点与系统内存访问在操作上是一致的。

Root Complex 会根据CPU 访问的地址决定数据访问路由,对于系统内存地址空间,数据会被路由到iMC (integrated Memory Controller) 访问DDR;对于MMIO地址空间,数据会被路由到Host Bridge 转换为 TLP 发起对设备的PCIe 通信。

一般的,Host Memory 分配都是Cacheable (writeback) 的,而 MMIO 通常是Uncacheable的,加之两者带宽和通信机理的不同,导致了CPU 使用地址直接访问PCIe MMIO空间无法达到访问系统内存的性能,也无法用满PCIe带宽。使用memcpy() 在Host Memory 和MMIO 地址拷贝数据也是一种低效方式。

对于连续的MMIO 空间访问,可以通过支持write combine的方式( mmap_wc() )来提升性能。

为什么需要使用PCIe DMA,在设备与主机间搬运数据?

PCIe DMA 能够实现高性能的数据搬运。

1.CPU 仅需要配置DMA Engine, 大块的数据搬运过程无需CPU参与,CPU占用率低;

2.DMA Engine 是全硬件化的通信方式,TLP payload 大overhead 小,PCIe链路使用率高;

3.支持descriptor 的DMA 能够实现用户态数据的零拷贝,减小内存带宽消耗;

4.支持多队列的DMA,能够提高系统并行度,支持多核,多进程应用,硬件解决IO抢占和调度问题,软件编程简单;

如何使用PCIe设备的中断?

PCIe 协议定义了三种中断:INTx (legacy), MSI, MSIX

1.INTx 中断是相对古老的PCIe设备中断方式,整个系统仅支持8个INTx 中断,所有设备共用。PCIe 中的INTx 中断是通过PCIe message发送到 switch 和 IO APIC的。CPU收到 IO APIC 转发到 local APIC 的 INTx 中断后,需要查询ISR确定中断源设备,并进一步查询中断含义,才能执行中断处理函数。中断数量少,中断查询复杂,响应延迟大,与数据流不保序等问题的存在,是INTx的主要缺陷。

2.MSI 是实现在配置空间的消息中断,每个PCIe function可支持最多32个MSI 中断。MSI 中断是一笔PCIe 写报文,向APIC 地址域写入特定的数据,触发CPU中断。因为其通过PCIe write TLP 实现,中断与业务数据的保序性容易实现,硬件处理Racing Condition的代价更小。MSI中断可以具备特定的含义,设备之间不耦合,中断响应快。

3.MSIx 是实现在Bar空间的消息中断,优点与MSI类似,但其数量支持更多,每个function 最多可以支持2K条中断向量。

MSI 和MSIx 是目前主流的中断实现方式,在虚拟化的场景下,中断可以通过IOMMU 实现remap 和 posting, 进一步提升系统性能。

网卡接收方向性能低,进行调优有哪些思路?

网卡收包性能性能调优,需先识别出性能瓶颈,可通过performance监控工具(如Intel PCM), 查看 CPU 利用率,内存带宽使用,PCIe流量等。

一般的,优化方向包括:

1.确定NUMA的亲和性,保证CPU/Memory/PCIe 三者的亲和性

2.确定PCIe全链路的带宽匹配,确保内存带宽(读+写双向)有余量

3.设备合理的PCIe通路MPS/MRRS

4.查看并打开IDO/RO (需注意应用场景无保序风险)

5.DMA Engine 参数的调优,Batch 操作的阈值配置(队列doorbell, completion notify等)

6.中断频率的调优和控制(一般在20K/100k 每秒,需结合应用和CPU)

7.DDIO 和 cacheable / uncacheable 内存空间的分配

具体原理和操作可参考课程中的有关介绍。

审核编辑:汤梓红

-

Keystone NDK常见问题解答2024-10-11 571

-

TFPxxx常见问题解答2024-09-29 495

-

CLOCK常见问题解答2023-11-23 727

-

CAN总线常见问题解答2021-12-27 2891

-

PDIUSBD12常见问题解答资料下载2021-05-14 1321

-

AN-1291:数字电位计:常见问题解答2021-03-19 1245

-

晶闸管实用技术问题解答2017-09-12 1124

-

广州大彩串口屏技术文档—硬件问题解答2016-07-01 854

-

PC 音质常见问题解答2010-08-02 662

-

新手-iPhone/touch常见问题解答2010-02-02 613

-

CCS问题解答2009-08-03 1041

-

TOPSwitch-HX常见问题解答2009-04-27 855

-

VxWorks常见问题解答2009-03-28 619

-

常见以太网馈问题解答2008-10-24 472

全部0条评论

快来发表一下你的评论吧 !