什么是DFT?我们为什么需要它?DFT可以永久的消除故障吗?

电子说

描述

1.什么是Design for Tesability,我们为什么需要它?

a. 芯片在制造过程中的问题

如今,半导体是整个电子行业不断发展的核心。新技术的发展,尤其是先进技术节点,如7nm及以下工艺,使集成电路行业能够跟上消费者不断增长的性能需求,也即摩尔定律得到延续,毫不夸张的说,集成电路技术是人类科技的支点。

但是,新的技术同时带来了新的挑战,芯片尺寸的变小会增加某些错误的可能性。芯片制造过程中的错误是我们不愿看到的,下面列出芯片制造中可能出现的一些问题。

- 密度问题 :随着纳米技术的出现,芯片制造过程越来越复杂。设计的晶体管越来越小,沟道长度越来越小,后端连线也越来越密集。现在的芯片,普遍有数十亿个晶体管,所以,两根导线之间短路或断路的概率很大,这些是错误或者故障的来源。关键是,在设计和制造过程中可能会出现大量此类错误。综上所述,晶体管密度的增加,芯片失效的可能性大大增加。

- 软件问题 :此外,除了制造过程的defect,用于设计芯片的EDA软件的bug或者工程师的失误,也会造成芯片失效。

- 应用问题 :在一些关键应用中,我们无法承受芯片的故障。例如,在医疗行业,设备控制器中的单个故障甚至会造成个人生命危险。对于使用低温燃料运行的火箭或航天飞机,其控制芯片需要在较宽的温度范围内工作。因此,这些芯片的测试条件应针对特定的环境且在极端条件上进行,以防止使用过程中发生任何故障。

- 维护问题 :万一未来发生故障,为了进行维修或者保养,我们需要精准定位问题。由于PCB尺寸不断缩小,因此用万用表测试已经无法定位问题,而且模块化设计正朝着SoC设计的方向发展,从而失去了相关性,最后使维护过程变得更加昂贵。

- 商业问题 :如果发现设计的芯片存在故障,最终会转化为公司的重大损失。稍后我们将讨论如何及时发现故障来降低成本。

即使在封装过程中,也有可能出现故障。考虑到所有这些问题,最关键的是在芯片出厂前进行测试,并且在每个关键过程都需要测试。

b. 解决问题的办法:DFT

测试从来就不是免费的午餐。现在的CPU都包含超过1000多个pins,内部包含许多功能,如果芯片内任一晶体管出现故障,整个芯片就会失效。作为消费者,我们不希望用到有故障的芯片。但是,要从数十亿个晶体管中找到单个缺陷晶体管,犹如大海捞针。我们需要穷尽各种组合来测试芯片所有功能,如果以这种方式进行测试,那么芯片上市时间非常久远,甚至以至于芯片可能永远无法到达消费者手中。那么如何解决这种问题?我们使用一种方法为芯片添加测试功能,叫可测性设计design for testability,DFT并不影响芯片的正常工作。

简而言之,可测性设计是一种通过向芯片添加更多电路来使芯片测试变得可行且具有成本效益的设计。此外,可测性设计技术可以改善内部节点的可控性和可观察性,从而可以测试芯片内部功能。

c. DFT的作用

i.测试时序电路

DFT提供了测试时序电路的解决方案,时序电路由于和时钟相关,正常的测试非常困难。与组合逻辑电路不同,我们无法仅通过查看输入来确定时序电路的输出。时序电路的输出取决于输入和时钟状态,很难从外部控制和观测内部触发器。

因此,除非将时序逻辑电路初始化为已知值,否则无法对其进行测试。为了初始化它们,我们还需要一组特定的功能。DFT使我们能够将此功能添加到时序电路中,从而使我们能够对其进行测试。

ii. 优化芯片制造过程

DFT在芯片制造过程中实现了两个重要目标:

- 拒绝有故障的芯片(品控)

测试会检查制造过程中的错误,这些错误会在设计的芯片中产生故障。较早的检查到故障,则可以将有故障的芯片丢弃,可以节省时间和金钱

- 监控和提高制造能力

芯片在制造过程中会经过很多次测试,如果测试失败,EDA软件可以定位到某个具体位置,然后进行切片分析其微观结构,最终定位到制造过程中。

d. DFT可以永久的消除故障吗?

测试是否可以保证芯片再也不会出现故障?

不会,芯片到客户手中,也有可能出现故障。如果芯片暴漏在高温或潮湿的环境或由于老化而随时可能出现故障。

举个例子,如果你有未锁定的CPU,你可以尝试超频,但是请不要这么做!

超频是一种将系统频率和电压提高到额定值以上的方法,配置不正确的超频可能会干扰时序指标并导致不稳定性。长时间超频会导致系统过热并承受压力,从而缩短计算机的使用寿命。这可能会导致芯片间歇性故障,并在将来造成随机崩溃。除此之外,它也可能使保修无效。以上例子只是对现实生活中可能发生故障的一种解释。

关键是,您甚至可以自行产生故障,芯片永远无法抵抗故障。它们总会发生,那么我们需要做些什么?测试设备可以增强我们的信心,通过测试芯片,供应商试图最大程度地减少将来发生错误和故障的可能性。

为了确保高质量的芯片,芯片在设计过程中还涉及一个辅助过程,即为验证。

2. 验证和测试的关系

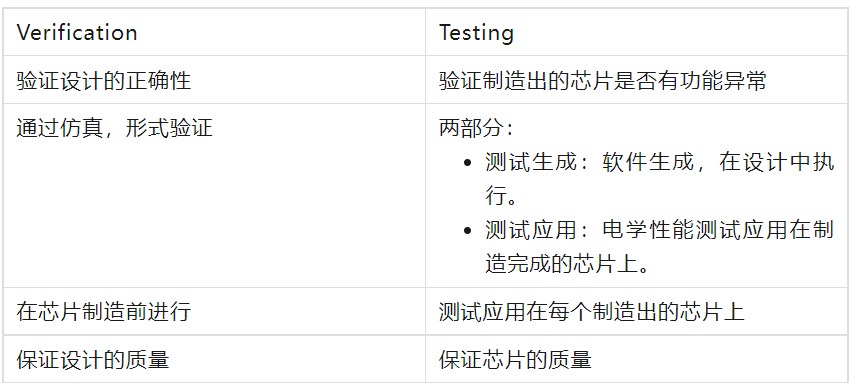

a. 验证和测试的不同点

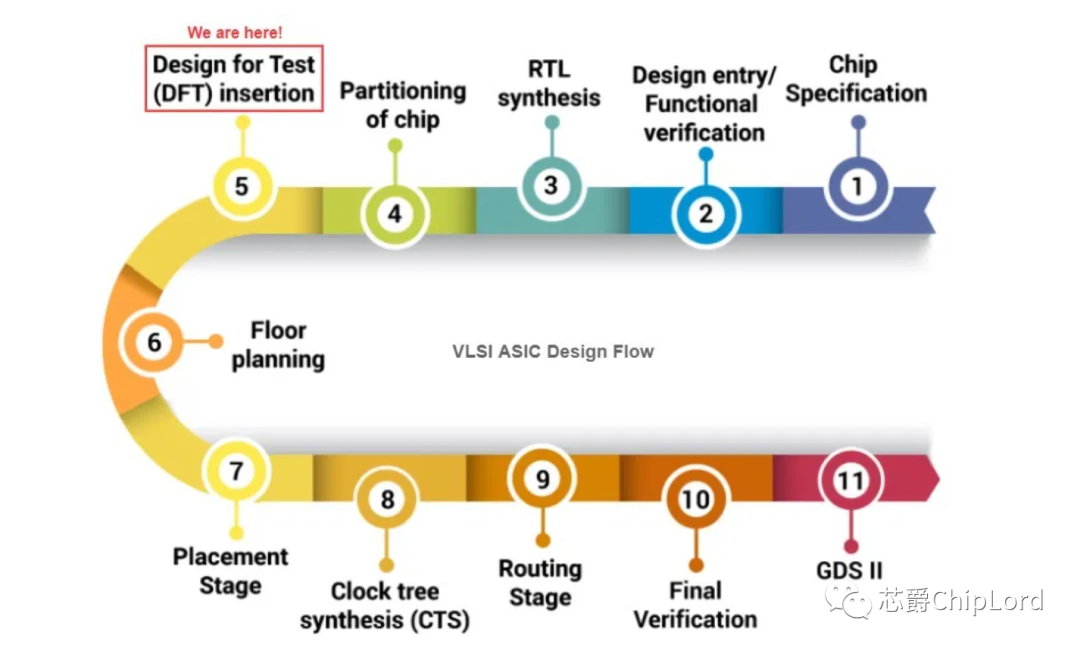

验证证明设计的正确性和逻辑功能,在使用硬件描述语言(VHDL/Verilog)对RTL设计进行编码后,即可完成该过程。它是用高级语言编写testbech来完成的。这仅在芯片实际制造之前执行一次,在设计中,通过system verilog进行验证,例如UVM。验证本身是一个单独的话题,这里不深入讨论。

相反,测试试图在芯片设计过程的每个抽象级别上保证所制造的芯片的正确性。由于在芯片制造和封装过程中均有可能发生故障,因此需要对每个芯片进行测试。通过测试,我们可以改善市场上出售的芯片的质量。

b. 职业选择?验证 vs DFT

让我们先讨论下这两个职位的工作内容。

验证和DFT在芯片设计行业中都很重要,从产品开发的角度,这两者的范围都很广,你可以根据自己的兴趣爱好,自行选择。

芯片设计大约2/3的时间用于验证,从而使其成为VISL设计流程中最耗时的过程,因此与DFT工程师相比,验证工程师的数量也是很大的,如果你是DFT工程师,那么与验证团队相比,团队规模会小很多。

DFT:

对于DFT,你需要精通CMOS VLSI,数字电路,数字电路测试,Verilog和一些脚本语言,这些技能将在你日常工作中发挥重要作用。你工作中会用到perl,shell和TCL等脚本语言。同时,DFT相关的EDA工具如:DFT compiler,TetraMAX,Tessent等。你将会和后端物理设计工程师和前端设计工程师紧密合作,职业道路,可能更适合后端物理设计,并且必须面对新技术的发展。

验证:

对于验证领域,你将从事设计开发和某些高级的testbench的编写,这需要分析和软件编程能力,以及硬件技能。需要具有verilog,system verilog,C++的专用知识等。

验证分为两个阶段:功能验证和物理验证。大多数验证工程师不会直接参与电路设计,晶体管或后端设计部分,主要着眼于前端领域。要成为验证专家,你需要实际项目经验。

4. 测试的分类

从等级角度,测试类别可分为:

- Chip-level

- Board-level

- System-level

有一条经验法则,叫十倍原则,从低级到高级(chip-->board-->system),测试成本要高10倍,如果在不同阶段发现芯片失效,损失的代价也是10倍左右。所以我们要尽早发现失效芯片,以减少损失。

5. 芯片失效的来源

下面是一些可能的故障来源:

- 芯片制造,例如contact的短路或开路。

- 材料缺陷,例如基底材料的裂纹或缺陷,表面杂质等。

- 老化损耗,介电击穿,电子迁移等。

- 封装过程,接触点短路或断路等。

6. 故障的分类

故障可以分成如下类别:

7. DFT技术

DFT技术广泛的分为如下两种类型:

Ad-hoc techniques

这些是从设计经验中学到的芯片设计过程的技术或规则集合,以使设计可测性更容易实现。基本上,这些是在遇到各种错误之后随着时间的推移而收集到的规则。

- Advantage

测试向量易于生成,没有设计规则约束,并且不会增大面积

- Drawbacks

测试结构不能重复利用,因为每种设计都有其特定的要求和可测性问题。无论使用哪种电路,都无法保证较高的可测性,系统性不足,无法采用统一的方法来进行可测性电路设计。

- Example

以下是一些专用DFT技术必须遵循的规则:大规模电路应划分为较小的子电路,以降低测试成本。必须插入测试点,以增强电路的可控性和可观察性,可以通过增加节点数或为要观察的内部节点多路复用现有的主要输出来完成。

Structured techniques

在这种技术中,额外的逻辑和信号被添加在电路中,以允许根据一些预定义的过程进行测试。

- Advantage

和专用DFT技术相比,结构化DFT技术意味着无论电路功能如何,始终可以使用相同的设计方法并确保良好的可测性。该技术是解决当今世界DFT问题的唯一解决方案。

- Disadvantage

但是,需要付出一定的代价,通常包括接受一定的设计规则,并且需要承受额外的面接和延迟。

- Example

以下是结构化DFT技术的一些示例,我们后续会详细介绍。

- scan path

- partial scan

- level sensitive scan

- BIST

- Boundary Scan

8. 总结

本文对VLSI中可测性设计做了简短介绍,关键点在于,IC制造过程很容易出现问题,这些故障可能在经济上造成更多损失。

-

DFT在信号处理中的应用 DFT与FFT的区别2024-12-20 4148

-

解析什么是DFT友好的功能ECO?2023-05-05 2843

-

什么是DFT友好的功能ECO呢?2023-03-06 3385

-

一个典型设计的DFT组件2022-11-30 1560

-

请问DFT是什么原理?2021-06-17 1576

-

可测试性设计(DFT):真的需要吗?2020-10-12 5249

-

离散傅里叶变换(DFT)2016-12-28 1030

-

让你彻底理解DFT2016-05-25 33831

-

DFT算法与FFT算法的优劣分析2014-05-22 5200

-

DFT工程师经典教程书籍2012-01-11 96676

-

超完善的DFT学习资料2011-12-15 76860

-

什么是DFT,DFT是什么意思2010-06-07 31530

全部0条评论

快来发表一下你的评论吧 !