谈谈CMOS反相器的静态特性与动态特性

电子说

描述

直观综述

反相器是所有数字设计的核心。静态CMOS反相器具有以下重要特性:

①输出高电平为V DD ,输出低电平为GND;

②属于无比逻辑,功能不受晶体管相对尺寸影响;

③具有低输出阻抗,输入电阻极高;

④理论上具有无穷大扇出,单个反相器可以驱动无穷多个门,增加扇出会增加传播延时,动态特性会变差,但不会影响稳态特性;

⑤在稳态工作情况下,电源线和地线之间没有直接通路,没有电流存在,意味着理论上没有静态功耗。

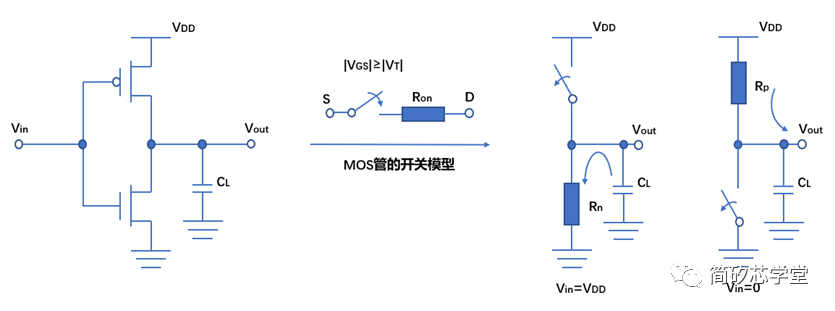

如下图是一个静态CMOS反相器的电路图,由一个上拉的PMOS器件和一个下拉的NMOS器件组成。通过使用MOS管的开关模型,可以将其等效成右边所示的反相器开关模型。当V in =VDD时,下拉NMOS器件开始工作,PMOS器件断开,将存储在负载电容CL上的电压放电至0V。当V in =0V时,上拉PMOS器件开始工作,NMOS器件断开,向负载电容CL充电至V DD 。

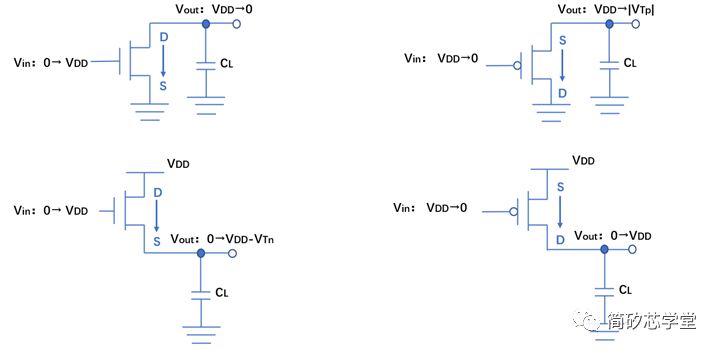

我们为什么要使用NMOS器件作为下拉器件,PMOS器件作为上拉器件呢?主要原因是PMOS器件是强1器件,而NMOS器件是强0器件。如下图所示,使用NMOS器件放电时可以将存储在负载电容CL上的电压放电至0V,而使用PMOS器件只能放电至|V Tp |。同样,使用PMOS器件充电时,可以向负载电容CL充电至V DD ,而使用NMOS器件只能充电至V DD -V Tn 。

PART TWO

静态特性

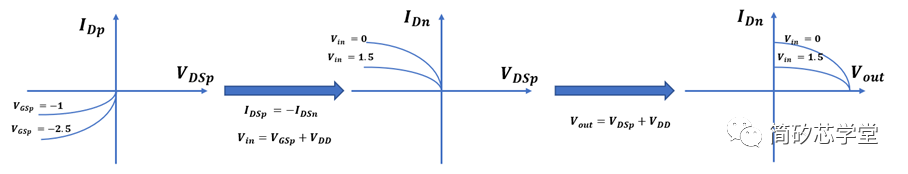

我们可以通过公式进行关系转换,将PMOS器件的I-V特性曲线转换到与NMOS器件相同的坐标系中。

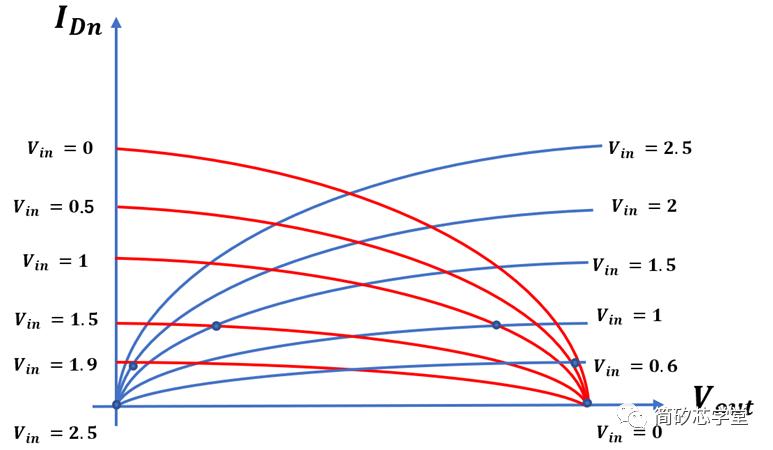

然后利用图解法迭加NMOS和PMOS器件I-V特性曲线,便得到了如下图所示的负载曲线,图中红线代表PMOS器件,蓝线代表NMOS器件。

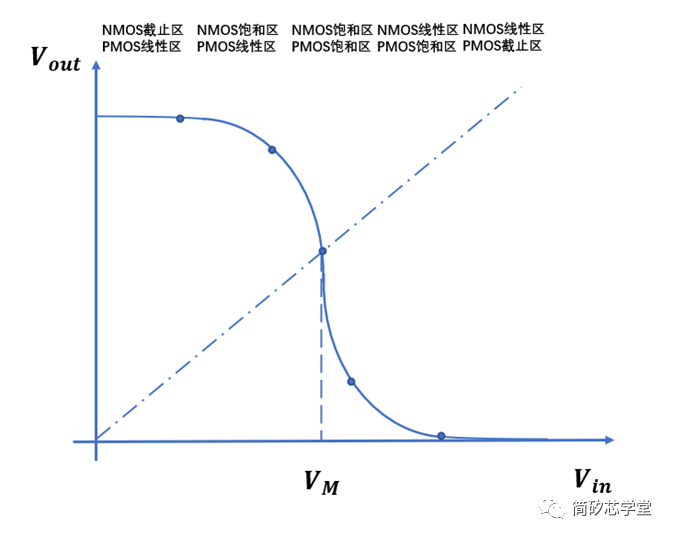

由于任何一个DC工作点成立,通过NMOS和PMOS器件的电流必须是相等的,再加上Vin是同样的,便可以找到图中的这些圆点,将这些圆点处的Vin和Vout整理出来,这样就得到了下图所示的反相器电压传输特性曲线。

电压传输特性曲线中有一个VM点,它便是开关阈值,一般定义为V in =Vout的点。图解法求VM是找出y=x函数与电压传输特性曲线的交点。

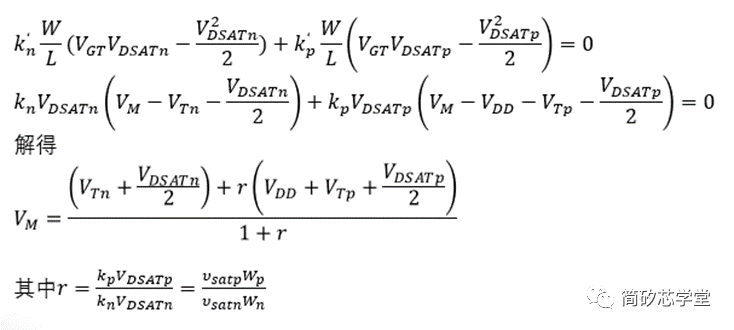

公式法是使用手工分析的通用MOS模型,代入V in =V M 。假设两个器件处于速度饱和,忽略沟道长度调制效应,于是有

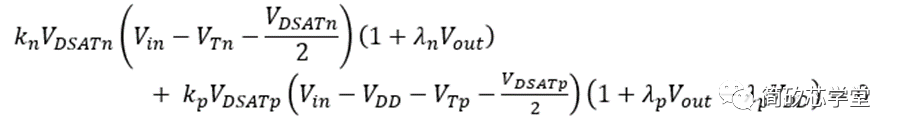

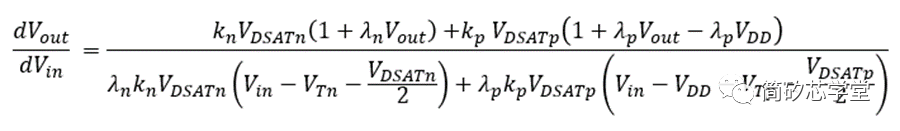

反相器在VM处的增益可以通过对Vin求导得到。假设两个器件处于速度饱和,不能忽略沟道长度调制效应。

在开关阈值附近对Vin求导,并求解:

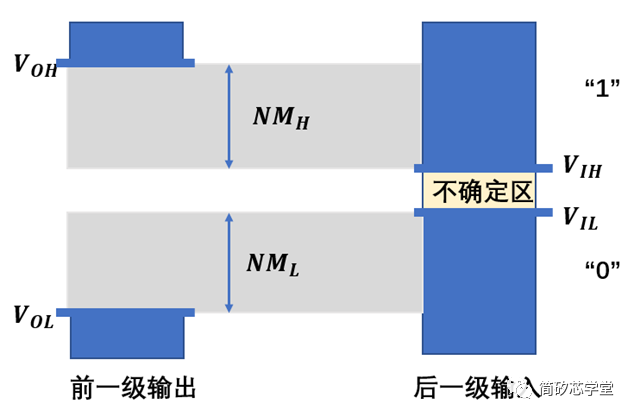

噪声容限是指在前一级输出为最坏的情况下,为保证后一级正常工作,所允许的最大噪声幅度。

其中NMH指的是高电平噪声容限,NML指的是低电平噪声容限。V IL 、VIH可以在VTC中求增益等于-1的工作点得到。

动态特性

传播延时表示一个信号通过一个门时所经历的时间,定义为输入和输出波形的50%翻转点之间的时间。

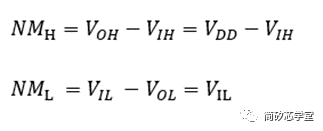

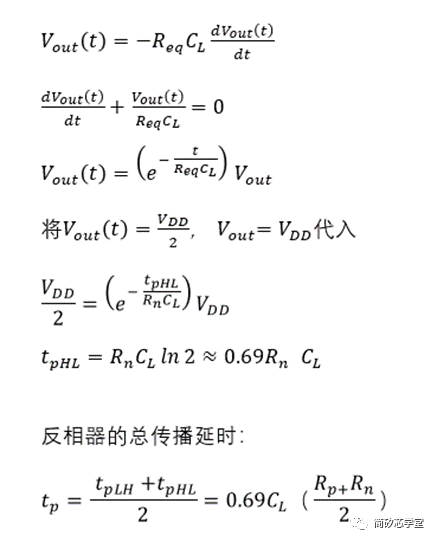

我们将充电过程的开关模型转换成一阶RC网络,列出电压关系:

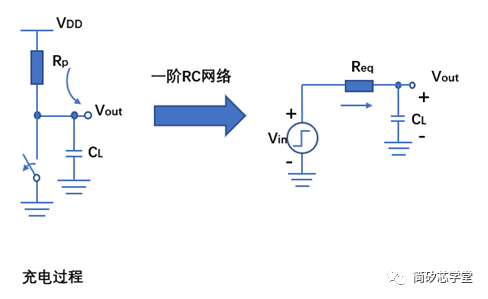

同理,我们可以求出放电过程的传播延时t pHL :

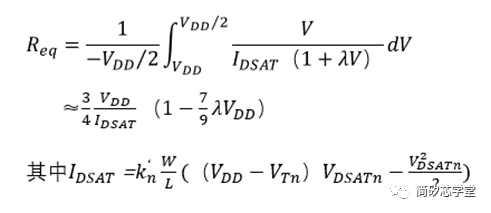

接下来我们看一下等效电阻的计算方法,计算通过NMOS晶体管放电时的等效电阻:

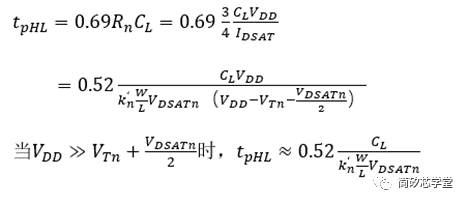

将等效电阻公式代入传播延时公式中,忽略沟道调制:

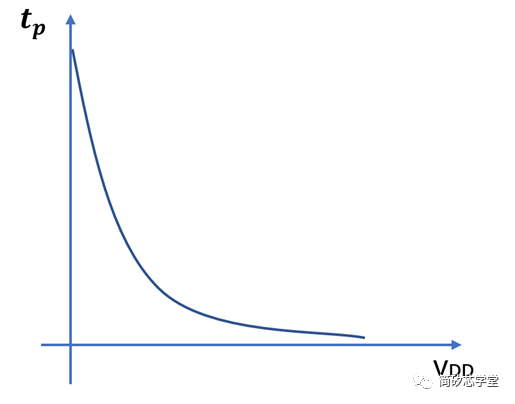

下图是CMOS反相器传播延时与电源电压的关系,我们可以观察到当V DD »V tn +V DSATn /2时,延时对于电源电压的变化较不敏感;当VDD接近2VT时将看到延时开始迅速增长。

通过以上讨论,我们可以采取以下措施来减小传播延时:

① 减小负载电容C L :包括三部分电容:门本身的内部扩散电容,互连线电容和扇出电容;

② 增加晶体管宽长比:会减小门的等效电阻,但增加晶体管尺寸也会增加本身的扩散电容,因而增加了C L ,当增加的扩散电容开始超过由连线和扇出形成外部负载,增加门的尺寸就不再对延时有贡献,这也被叫做自载效应;

③ 提高V DD :会增加功耗,并且当增加的电压超过一定程度后改善非常有限。

功耗

CMOS反相器的总功耗分为动态功耗和静态功耗,我们首先看一下动态功耗。动态功耗主要有两种,由充放电电容引起的动态功耗和由直接通路电流引起的动态功耗。充放电电容引起的动态功耗大致过程是在充电过程中,一半能量被PMOS管消耗,一半能量存储在CL负载电容中;放电过程中,存储在电容上的能量被NMOS管消耗。

f 0→1 :称为开关活动性,是消耗能量的翻转频率,也就是每秒通断次数

另一种动态功耗是由于输入波形存在上升和下降时间,导致在开关过程中从VDD到GND之间在短期内出现一条直流通路,造成短路电流。

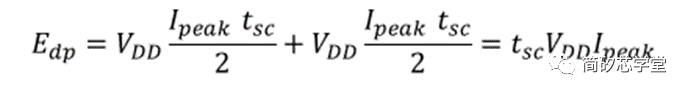

每个开关周期消耗的能量:

由直接通路电流引起的动态功耗:

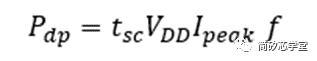

接下来,我们分析一下峰值电流Ipeak

• 当负载很大,输出的下降时间明显比输入上升时间大,输入在输出改变之前就已经通过了过渡区,PMOS的源漏电压近似为0,P管就基本关断了,所以Ipeak很小

• 反之,当负载很小,输出下降时间明显小于输入上升时间,PMOS的VDS大部分时间等于V DD ,所以导致了最大的短路电流

我们得到的结论是:使输出的下降时间大于输入上升时间可以减小短路功耗,但输出的上升/下降时间太大会降低电路速度,并在扇出门中引起短路电流。换句话说,当负载电容比较小时,直接通路电流引起的动态功耗将占主导,而当负载电容较大时,充放电负载电容引起的动态功耗将占主导。

静态功耗一般由源(或漏)与衬底之间的反偏二极管漏电和亚阈值漏电构成:

①源(或漏)与衬底之间的反偏二极管漏电

通常情况下非常小,该部分漏电是由热产生的载流子引起的,该数值随结温而增加,并且呈指数关系。

②亚阈值漏电

VGS接近阈值电压时会有源漏电流,在深亚微米工艺下,电源电压降低导致这一电流越发显著。

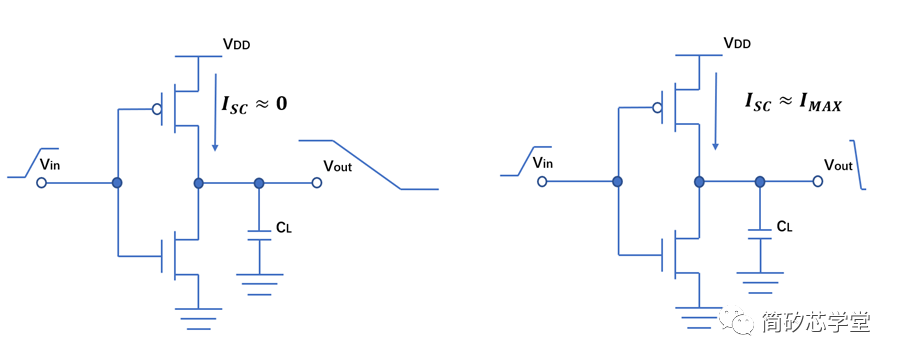

静态功耗计算公式为:

I stat :指在没有开关活动存在时在电源两条轨线之间流动的电流。

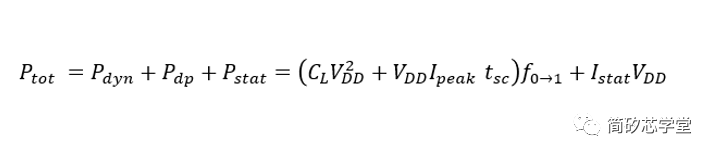

CMOS反相器的总功耗为:

应当指出的是在典型的CMOS电路中由充放电电容引起的动态功耗占主导地位,直接通路电流引起的功耗可以通过设计控制在限定范围内,而漏电造成的静态功耗在未来的工艺制程下会占据更大比重。

-

TTL反相器和CMOS反相器的区别2024-07-29 6538

-

CMOS反相器的工作示意图 影响CMOS反相器特性的因素2024-02-26 9872

-

什么是传感器的静态特性和动态特性?2024-01-30 8999

-

影响CMOS反相器特性的因素2024-01-26 4424

-

什么叫CMOS电流源(漏)反相器?它有什么优点?2023-09-12 3255

-

virtuoso中进行CMOS反相器和静态寄存器的电路设计2021-11-12 5220

-

MOS反相器和CMOS反相器的详细资料说明2020-03-20 3875

-

cmos反相器的输出特性2018-08-16 26168

-

cmos反相器设计电路图2018-03-27 86912

-

详细讲解cmos反相器的原理及特点2017-11-30 92969

-

传感器的静态特性和动态特性2016-04-26 4450

-

有比型动态MOS反相器2009-12-04 1579

-

CMOS反相器工作原理及传输特性2009-04-06 27580

全部0条评论

快来发表一下你的评论吧 !