SOC V3.0与V2.0的区别是什么?

电子说

描述

soc v3.0项目介绍

模块升级

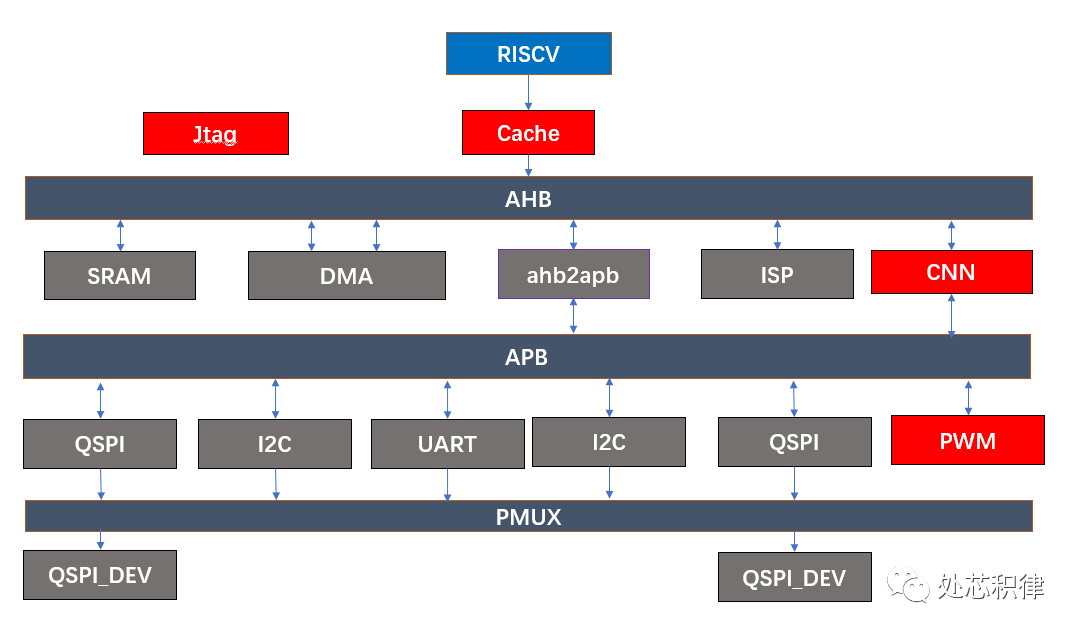

SOC V3.0在2.0项目的基础上增加了Jtag、iCache、CNN 和PWM模块。

所以3.0版本总共含有QSPI、I2C、UART、PMUX、ISP、DMA、JTAG、ICACHE、CNN、PWM和RISCV等11个模块,涵盖了协议类、算法类、存储类和AI 相关的各个IP,满足了大部分IC设计、验证工程师的实践需求。

研发工具升级

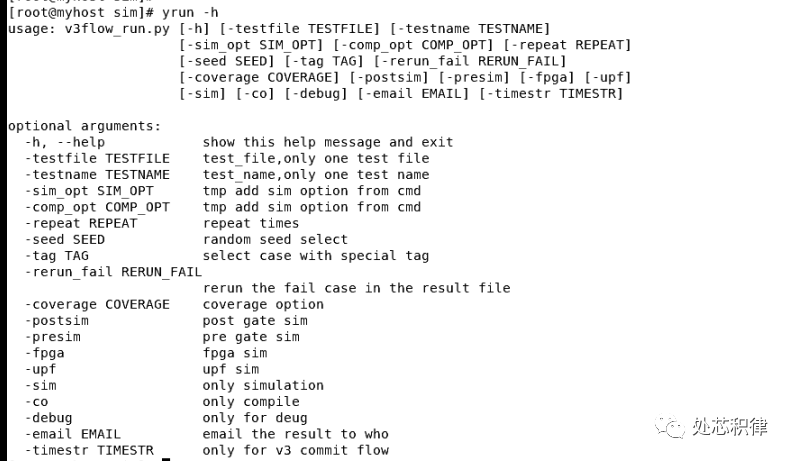

在环境上,我们研发了yrun 回归/仿真辅助工具,yrun支持以下的功能:

简洁的test 添加机制;

simulation和compile 分开管理;

支持只编译模式;

支持只simulation模式;

支持特定的 test list的 regression;

支持同时跑不同的regression;

支持 simulation 进行时在终端上打印log;

支持simulation 在后台运行;

支持特定 test list 中 特定test的 simulation;

支持 fail test的rerun机制;

支持中间查看特定regression的运行状态;

支持将regression的结果通过mail的方式发给指定的用户;

支持将regression的fail test的error 显示在regression的结果中;

支持用户定义FPGA simulation,Gate lever simulation,UPF simulation等。

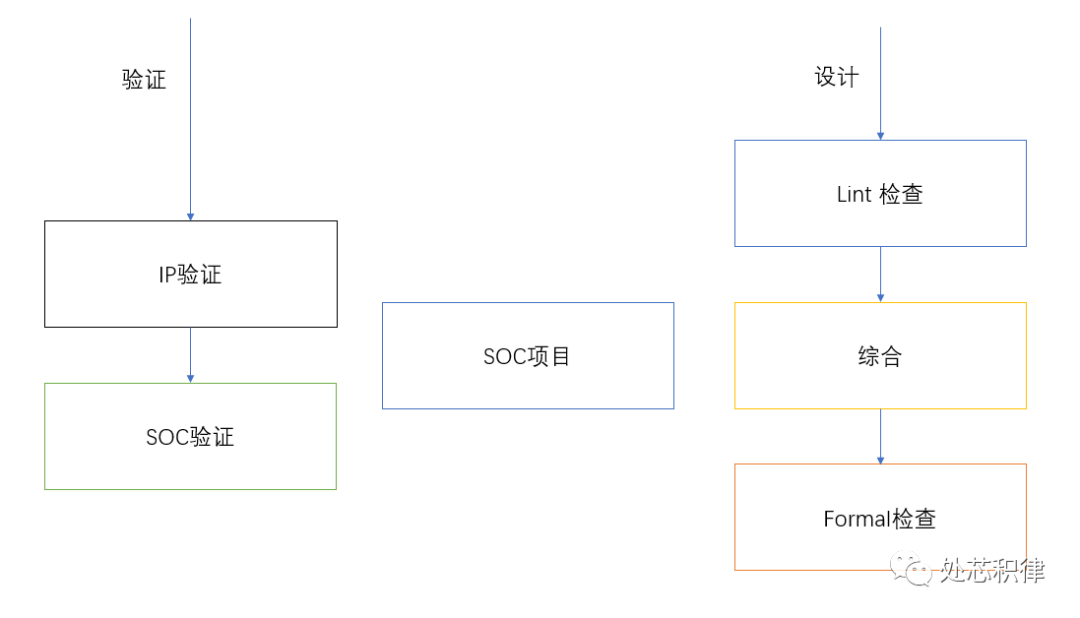

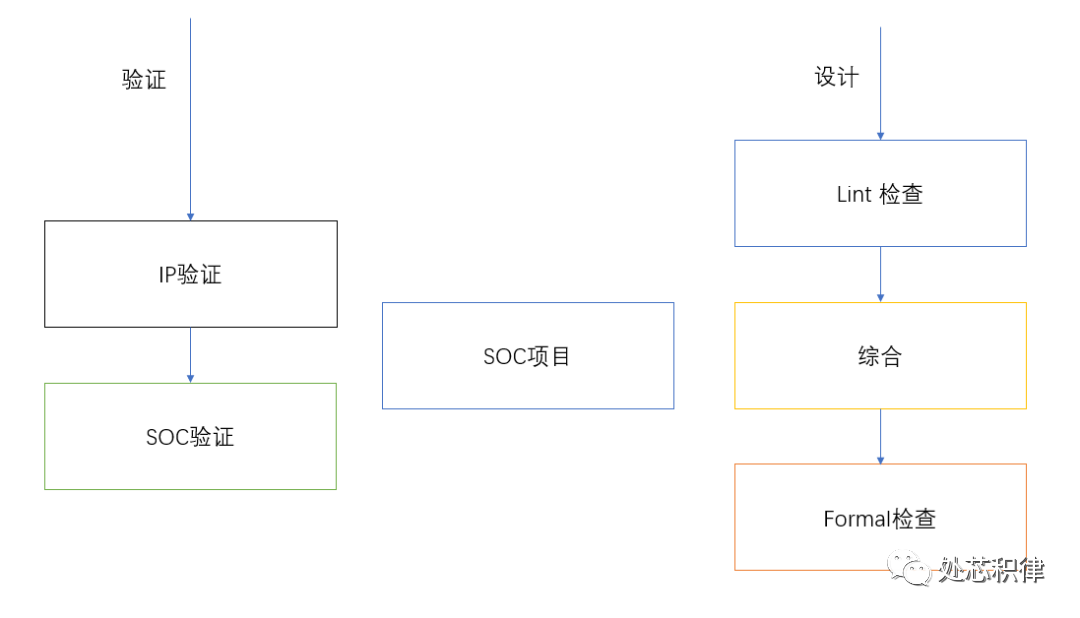

完善前端研发流程

我们在原有的基础上增加了Lint检查,综合 和Formal检查的脚本。

综合采用130 nm的工艺。

验证环境升级

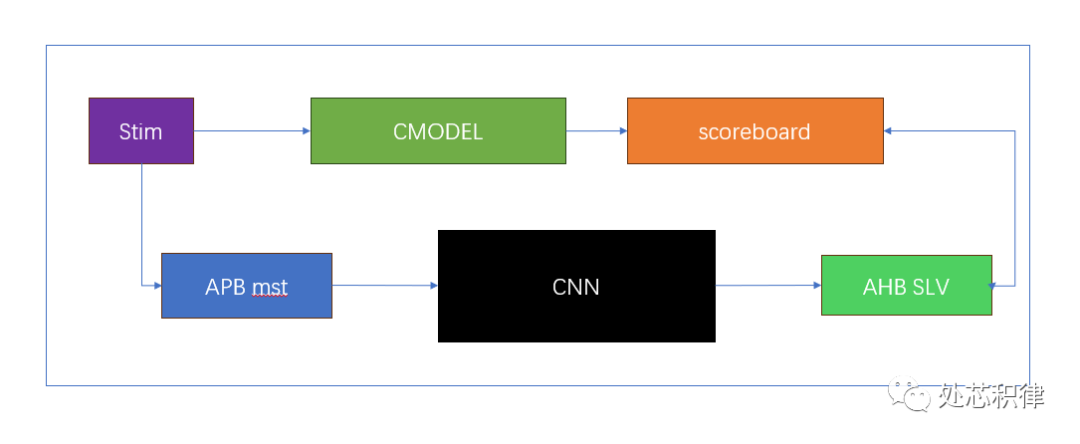

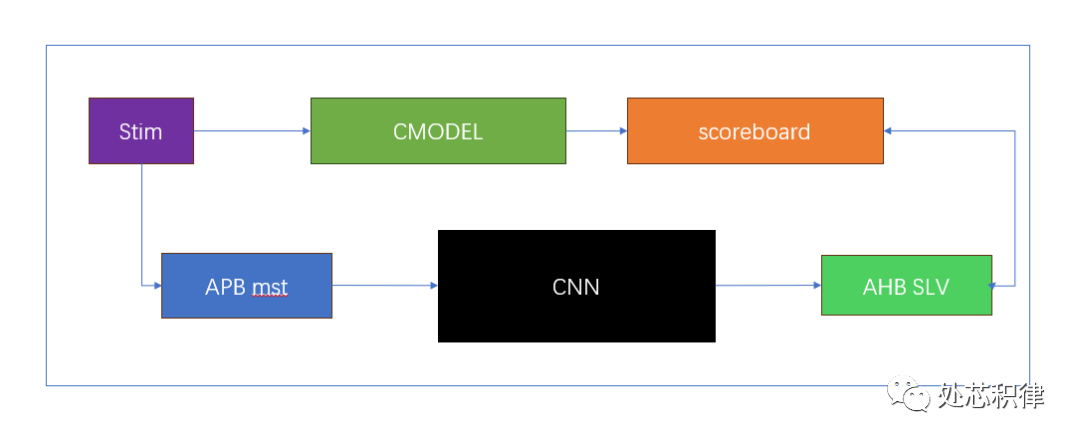

增加CNN验证环境,使用DPI进行验证:

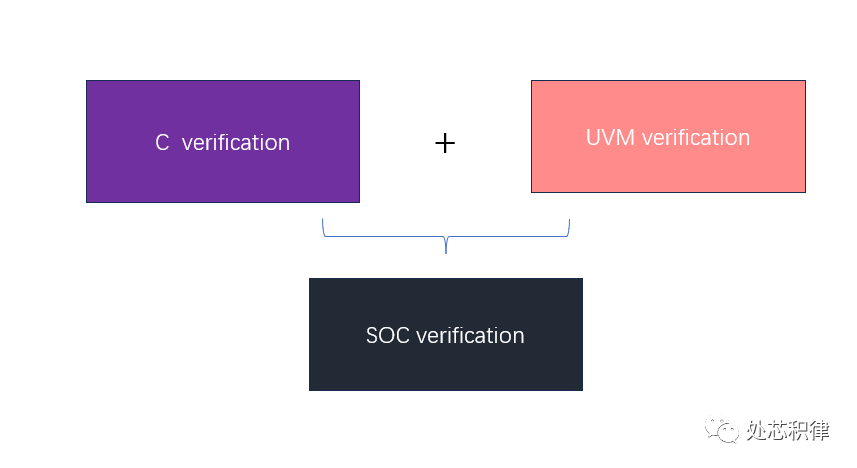

增加SOC UVM验证环境,使得SOC既支持使用C code 进行验证,又可以使用UVM进行验证。

基于AI的验证

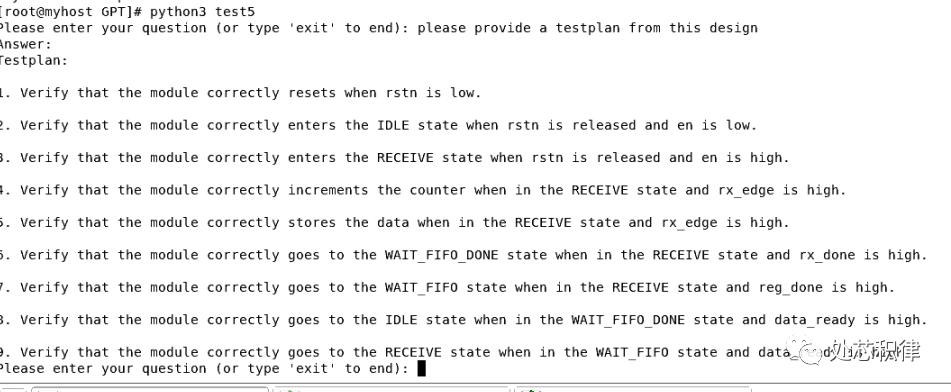

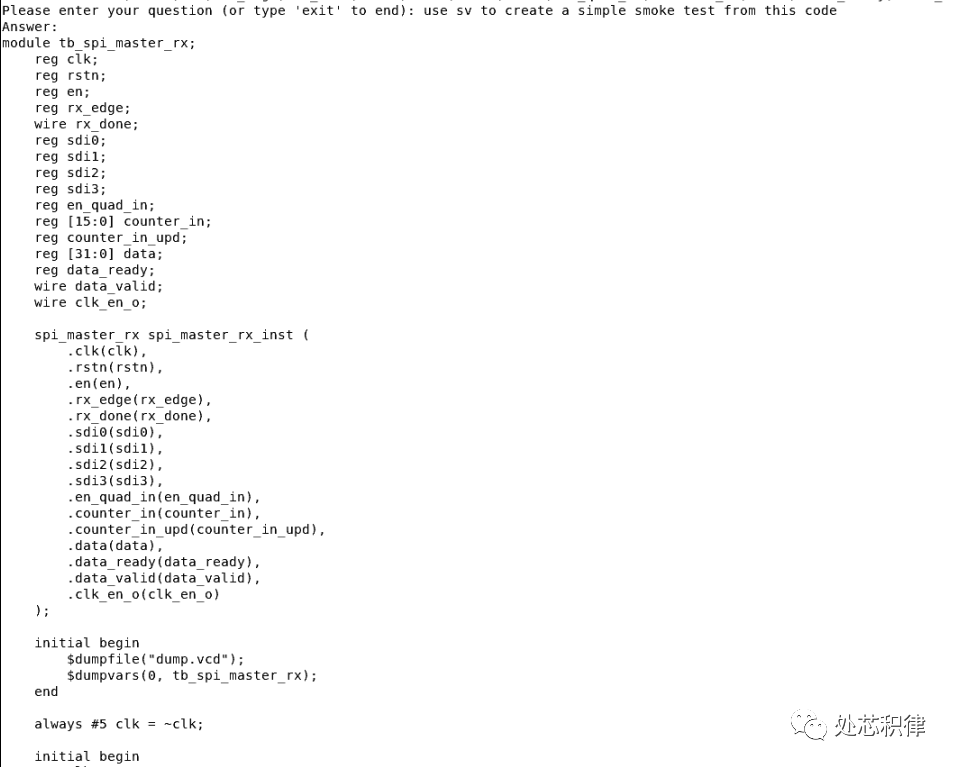

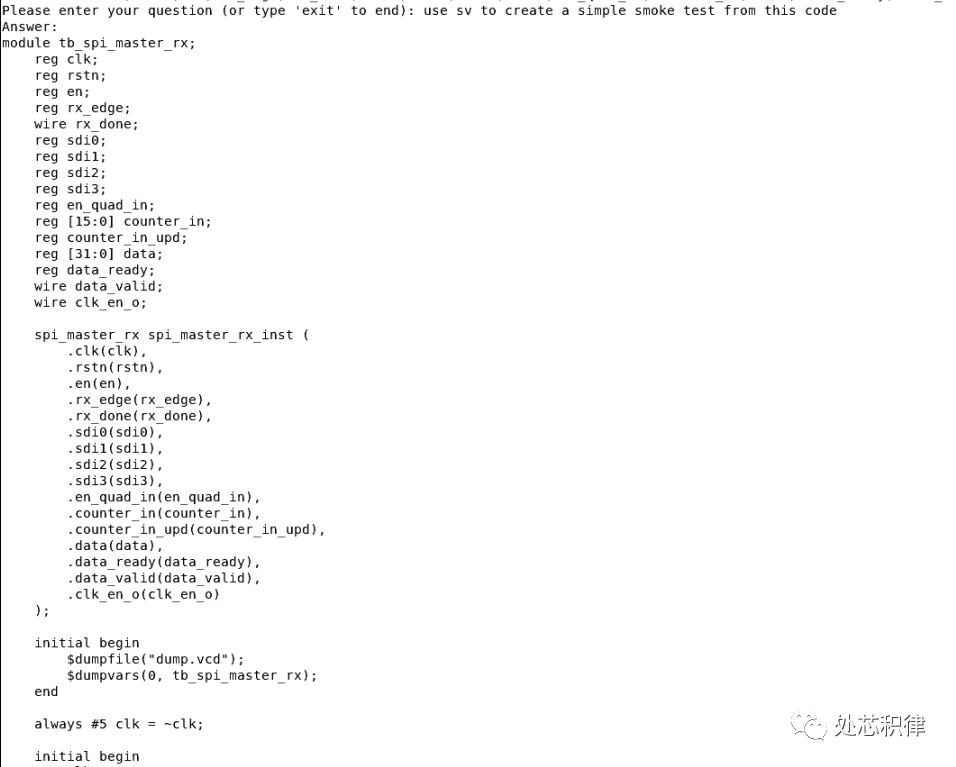

在SOC V3.0中,我们集成了使用chatgpt 检查代码,提取验证计划,以及产生简单的test的功能。

提取验证计划:

生成简单的test:

除上述之外,我们还在SOC V3.0中集成了SOC V1.1的改动:

1. 补全了I2C_DEV 和UART_DEV;

2. 实现C代码中字符串打印;

3. 完善的QSPI验证计划,验证用例和coverage数据;

4. 提供了QSPI 和CNN的问题代码,供大家自己debug使用。

编辑:黄飞

-

从EDMA v2.0迁移到TMS320DM644X DMSoC的EDMA v3.02024-10-16 540

-

从EDMA v2.0迁移到EDMA v3.0 TMS320C64X DSP2024-10-15 378

-

启英泰伦语音AI平台V3.0功能介绍2022-11-01 2246

-

MCUBootUtility v3.0怎么样?2022-02-10 961

-

NodeMCU V3.0 Arduino开发之点灯测试程序2021-11-01 1551

-

NodeMCU V3.0 Arduino开发之点灯2021-10-25 976

-

求普中单片机HC6800-EM3 V2.0开发板的光盘资料2018-08-21 4245

-

VORX-NH 说明书V3.02016-12-30 1412

-

STM32F4 EMWIN开发手册V3.02016-07-25 1236

-

EP1122集合版V3.02015-11-30 1897

-

求普中科技的板子HC6800-EM3 V2.0的光盘资料2015-06-02 28799

-

FilterPro v3.0设计工具的最新版本2010-05-17 8569

-

Protel for Windows v2.0 SCH 汉化2009-03-21 598

全部0条评论

快来发表一下你的评论吧 !