基于ICL的可扩展性和灵活性可以抽取设计中的IEEE 1687结构

电子说

描述

随着SoC芯片逐渐复杂化,其DFT(Design for Test)架构也由单层向多层网络发展。IEEE 1687是DFT多层网络结构的通用标准,其核心内容包括Heirachical Architecture,模块连接语言ICL(Instrument Connectivity Language)和过程描述语言PDL(Procedural Description Language)。

其中,ICL是一种硬件架构描述语言,用于描述设计中IEEE 1687的网络结构(又称IJTAG网络结构),即不同类型嵌入式模块之间的层级连接,使得硬件的可扩展性和访问的灵活性得到极大地加强。

一、ICL的组成

ICL是描述模块间连接的语言,它不包括设备内部具体操作的细节。因此可以概括地说,ICL是由Instruments 及其Connection描述组成的。

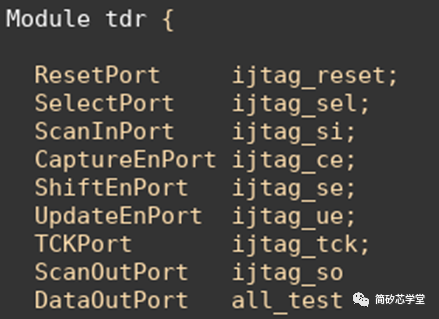

1、Instrument

ICL中的Instrument包含TAP、SIB、TDR及DFT IPs(EDT,OCC,MBIST…),它们是构成1687网络的关键节点,每一个Instrument都在Module中定义,如图定义的TDR。

2、Connection

ICL中的Connection是对Instrument的Keywords 、Attribute、Scan_Cell、Interface以及PortsToPorts连接等的描述。

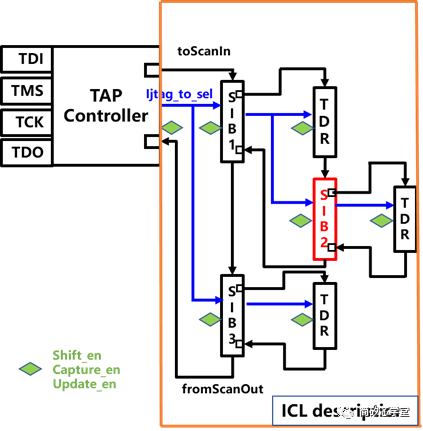

如图是ICL描述的网络结构的部分示意图,SIB和TDR为Instruments,不同颜色的连线即ICL描述的Connection。以SIB_2为例,其ICL描述语言如下:

Instance sib_* Of sib_2 {

InputPort ijtag_reset = ijtag_reset;

InputPort ijtag_sel = ijtag_sel;

InputPort ijtag_si = sib1.ijtag_so;

InputPort ijtag_ce = ijtag_ce;

InputPort ijtag_se = ijtag_se;

InputPort ijtag_ue = ijtag_ue;

InputPort ijtag_tck = ijtag_tck;

InputPort ijtag_from_so = tdr.ijtag_so;

Attribute tessent_design_instance = "sib_*";

}

二、ICL的Bottom Up

IEEE 1687的多层网络结构决定了ICL是以Bottom Up的方式逐步实现对Core层、Subsys层及Chip层的描述。

1、Core层的描述

Core层的ICL会对Modified Core内部的Module逐一按照如下步骤描述:

首先,ICL会整理出该Module的IJTAG网络端口及Interface,可能包括ClkPort、ToClkPort、SelectPort、CaptureEnPort、ShiftEnPort、ScanInPort、ScanOutPort、UpdataEnPort、DataOutPort等,并且会source这些端口的来源,描述它们的属性,比如Clock_Domain、Connection_Rule等;

接下来,ICL逐一将module内部实例化的DFT IP的Client/Host端口与其他实例连接,具体到端口对端口,形成DFT网络;

最后,Core内部Module的ICL集成得到整个Core的ICL。

2、Subsys层的描述及与Core层ICL的衔接

Subsys层ICL的描述步骤与Core一致。如果Subsys内含有上述已经存在ICL的Core,那么首先,该Subsys会将内部Core当成一个Box,抓取Core_Top层的IJTAG端口加入到Subsys层的描述,从而将Subsys层的IJTAG网络与Core层的IJTAG网络进行组合。

而后,Core内部的关于Module和Instance的ICL描述都会复述到Subsys的ICL中,使得Subsys与Core在ICL文件中形成一个完整的DFT网络。

Chip层的描述及其与Subsys层的衔接

Chip层的ICL描述步骤与Subsys一致,对于内部已存在ICL的Module的处理方式也与Subsys一致。

将分层的ICL集成,会得到整个Chip的完整ICL网络。

三、总结

基于ICL的可扩展性和灵活性,它可以抽取设计中的IEEE 1687结构,方便用户从高层次的角度去配置相应的寄存器。ICL语言还可以帮助用户了解和配置复杂的IEEE 1687网络,解决了在配置寄存器时网络复杂、难以确定输入数据长度和值的问题。

-

什么是云计算的可扩展性?2023-08-08 3467

-

如何去提高电源管理的灵活性?2021-04-23 1595

-

视频监控系统新结构必须具备可扩展性2017-11-25 2694

-

基于软件定义网络控制可扩展性研究2017-12-19 1236

-

Beyond 100G标准的灵活性和可扩展性2018-11-22 3647

-

如何解决区块链的可扩展性问题2019-03-20 2619

-

区块链可扩展性的要点分别是什么2019-10-31 3056

-

影响软件高可扩展性的六大因素2021-02-17 9632

-

AIoT开放平台可实现灵活且可扩展的开发2022-10-19 1805

-

接入 5G:NVIDIA CloudXR 4.0 现已发布,优化 XR 部署的灵活性和可扩展性2023-03-28 1787

-

什么是可扩展性,为什么它很重要2023-04-21 6677

-

西部数据推出全新产品助力数据中心提升灵活性和可扩展性2023-08-09 1679

-

SD-WAN组网的可扩展性怎么样?2023-08-18 1197

-

可扩展性对物联网管理系统有哪些影响?2023-10-11 1259

-

如何评估电能质量在线监测装置的扩展性?2025-10-22 726

全部0条评论

快来发表一下你的评论吧 !