Chiplet与SoC、SiP的比较

制造/封装

描述

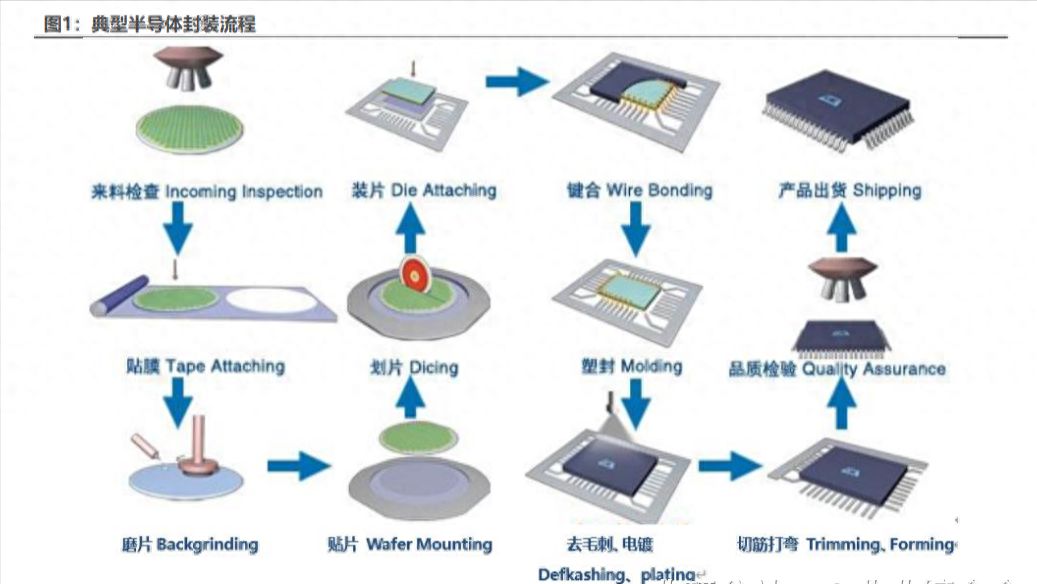

半导体封装是半导体制造工艺的后道工序,是指将通过测试的晶圆加工得到独立芯片的过程,即将制作好的半导体器件放入具有支持、保护的塑料、陶瓷或金属外壳中,并与外界驱动电路及其他电子元器件相连的过程。

先进封装发展历程

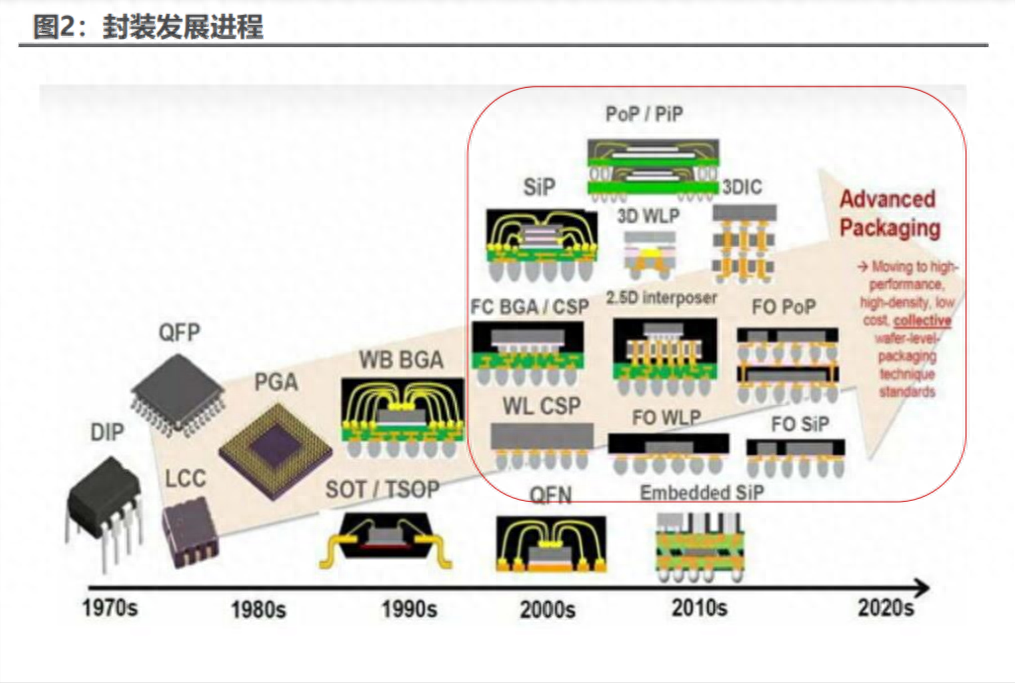

迄今为止全球集成电路封装技术一共经历了五个发展阶段。通常认为,前三个阶段属于传统封装,第四、五阶段属于先进封装。当前的主流技术处于以 CSP、BGA 为主的第三阶段,且正在从传统封装(SOT、QFN、BGA 等)向先进封装(FC、FIWLP、FOWLP、TSV、SIP 等)转型。

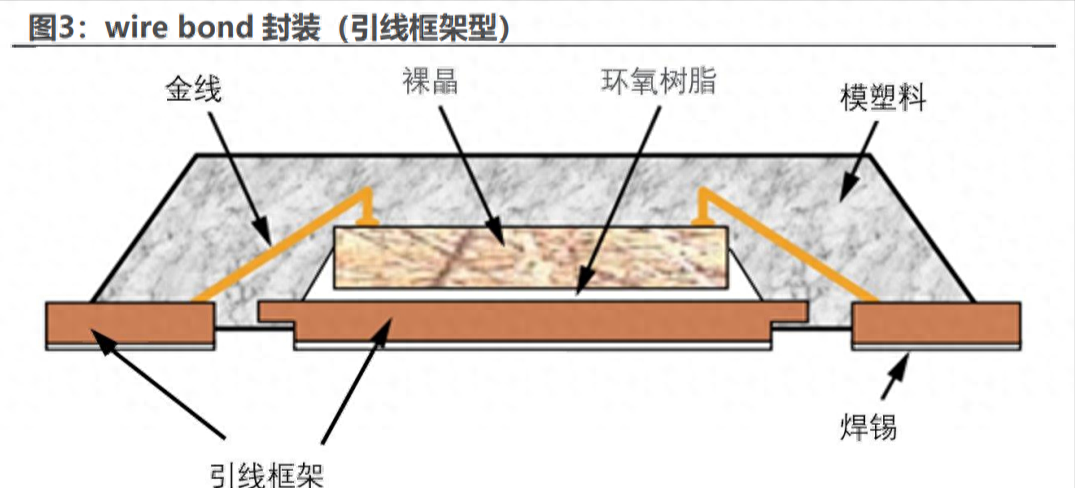

传统封装以引线框架型封装为主,芯片与引线框架通过焊线连接,引线框架的接脚连接 PCB,主要包括 DIP、SOP、QFP、QFN 等封装形式。

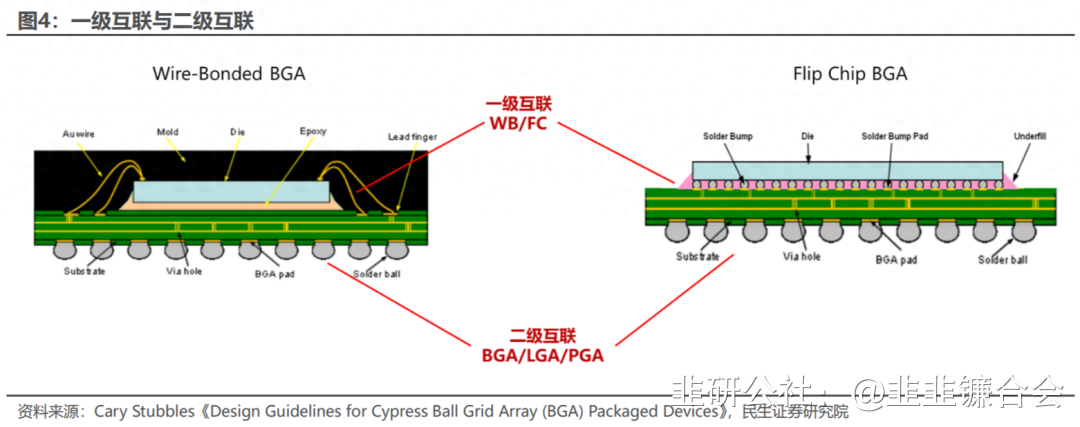

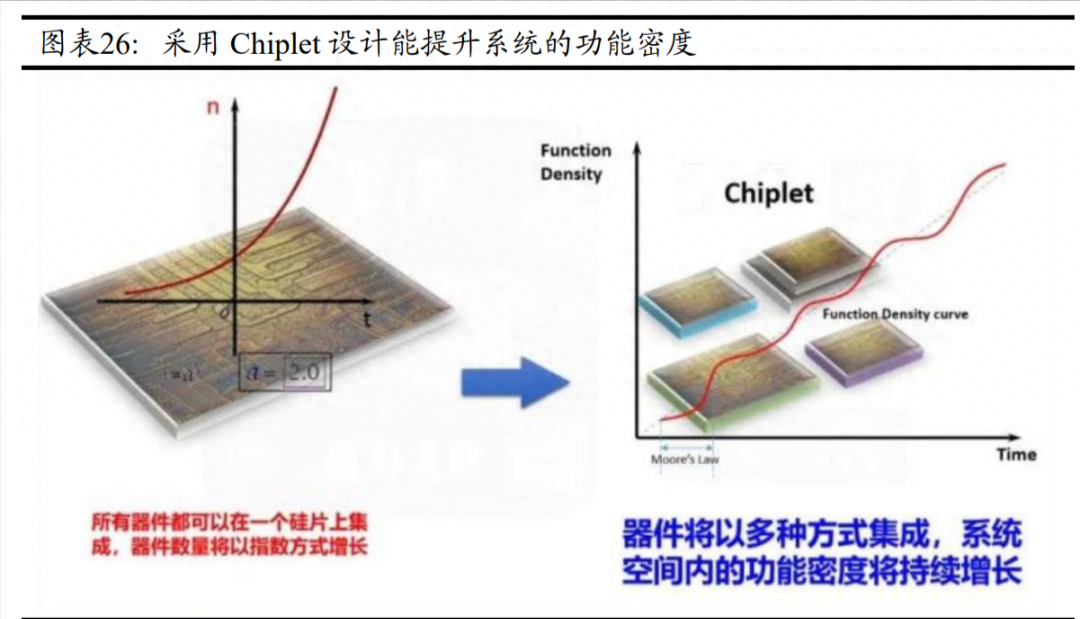

传统封装的功能主要在于芯片保护、尺度放大、电气连接三项功能,先进封装技术则对芯片进行封装级重构,能有效提高系统高功能密度。现阶段先进封装主要是指倒装焊(Flip Chip)、晶圆级封装(WLP)、2.5D 封装(Interposer)和3D 封装(TSV)等。先进封装与传统封装的主要区别在于一级互联和二级互联方式的不同。 一级互联方式主要包括:传统工艺—Wire Bonding(WB);先进工艺—Flip Chip(FC)。 二级互联方式主要包括:传统工艺—通孔插装型/表面贴装;先进工艺—球栅阵列型(BGA)/平面网格阵列 LGA/插针网格阵列(PGA)。 因此 FCBGA、FCLGA 等封装就称为先进封装。同时,传统的元件封装也演变为系统封装,封装对象由单芯片向多芯片发展,由平面封装向立体封装发展。

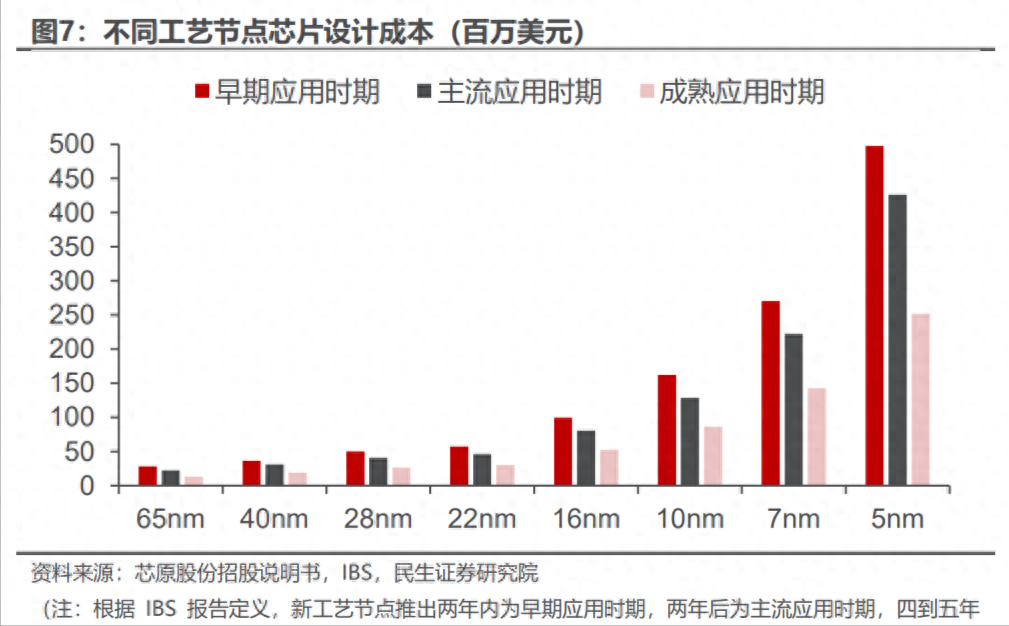

先进封装助力摩尔定律延续 摩尔定律主要内容为:在价格不变时,集成电路上可以容纳的晶体管数量每18-24 个月便会增加一倍,即:处理器性能大约每两年翻一倍,同时价格下降为之前的一半。 自 2015 年以来,集成电路先进制程的发展开始放缓,7nm、5nm、3nm 制程的量产进度均落后于预期。随着台积电宣布 2nm 制程工艺实现突破,集成电路制程工艺已接近物理尺寸极限;与此同时芯片设计成本快速提升,以先进工艺节点处于主流应用时期设计成本为例,工艺节点为 28nm 时,单颗芯片设计成本约为 0.41 亿美元,而工艺节点为 7nm 时设计成本提升至 2.22 亿美元。

为有效降低成本、进一步提升芯片性能、丰富芯片功能,各家龙头厂商争相探索先进封装技术。先进封装技术作为提高连接密度、提高系统集成度与小型化的重要方法,在单芯片向更高端制程推进难度大增时,担负起延续摩尔定律的重任。

Chiplet 优势明显,是***“破局”路径之一 高性能计算的应用场景不断拓宽,对算力芯片性能提出更高要求,进而拉动了先进封装及Chiplet工艺的需求。随着AI大模型数据处理需求的持续提升,对算力芯片性能提出更高要求。Chiplet是高性能算力芯片的封装解决方案之一,其在设计、生产环节均进行了效率优化,能有效降低成本并持续提高系统集成度。Chiplet需要采用先进封装工艺中的异构集成技术进行实现,因而Chiplet的高增长亦将带动异构集成的需求提升。根据Omdia预测,随着人工智能、高性能计算、5G等新兴应用领域需求渗透,2035年全球Chiplet市场规模有望达到570亿美元,2018-2035年复合年均增长率为30.16%,发展势头强劲。

与传统SoC相比,Chiplet在设计灵活度、良率等方面优势明显。相对单片集成技术SoC而言,Chiplet是由不同工艺节点的模块共同组成,在相同的系统性能目标下,部分模块对制程的要求有所降低,节省了部分开发时间;由于芯片面积越大越容易产生缺陷,而Chiplet每个模块的载体都是较小的硅片,有效降低了生产中产生的缺陷数量;同时每个小硅片拥有单独的IP,并且可以重复使用,根据特定客户的独特需求定制产品,节省开发时间。不同工艺生产制造的Chiplet可以通过SiP技术结合,典型的方案就是XPU+DRAM,通过异构集成把内存和算力单元直接整合到一起,提升系统性能、突破算力瓶颈。

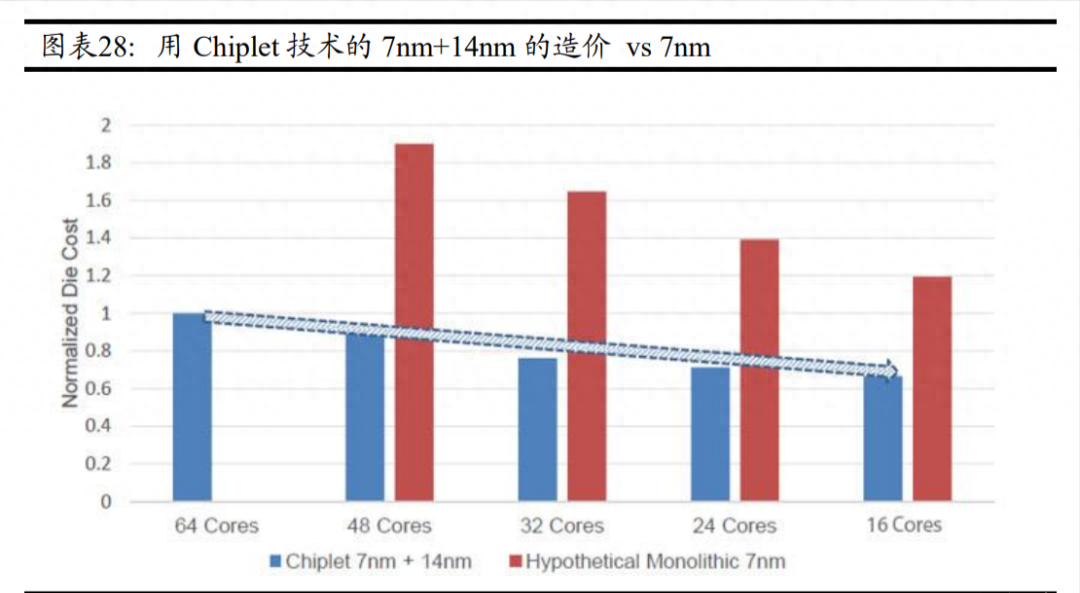

针对先进制程,Chiplet更具成本优势。一方面小芯片形式的制造良率有所提升,另一方面是Chiplet允许使用不同的制程制造异构芯片,例如高性能模块采用7nm,其他模块只需要14nm或28nm就可以做到性能最大化,使系统整体的功能密度非常接近于7nm的集成。AMD采用“7nm+14nm”的Chiplet设计方案,较7nm的单芯片集成的成本下降了接近一半。AMD认为是否使用Chiplet设计思想的动机,在于性能、功耗与造价能否妥协。Chiplet对成本下降的效果会随着核数(芯片核心的数量)的降低而边际减小,因此未来可能会出现一个价格的均衡点来判断采用Chiplet技术是否更具有经济效益。

Chiplet降低了芯片设计的成本与门槛,且其IP复用的特性提高了设计的灵活性,是***“破局”路径之一。

编辑:黄飞

-

手把手教你设计Chiplet2025-09-04 934

-

深入解析:SiP与SoC的技术特点与应用前景2025-02-14 2719

-

Chiplet是否也走上了集成竞赛的道路?2024-02-23 1901

-

chiplet和sip的区别是什么?2023-08-25 5797

-

什么是Chiplet?Chiplet与SOC技术的区别2023-03-29 4099

-

芯片厂商从SoC架构转向Chiplet2022-11-17 2538

-

关于HIC、MCM、SIP封装与SOC的区别2022-05-05 2135

-

chiplet是什么意思?chiplet和SoC区别在哪里?一文读懂chiplet2021-01-04 60966

-

如何使用Die-to-Die PHY IP 对系统级封装 (SiP) 进行高效的量产测试?2020-10-25 3713

-

SiP与Chiplet成先进封装技术发展热点2020-09-17 10916

-

SiP的特点与SOC的区别和SiP的应用和发展方向的参考资料2018-04-29 33349

-

简单介绍SoC与SiP中芯片解密的应用2017-06-28 3089

-

一文读懂SIP与SOC封装技术2016-10-29 22910

-

SoC与SiP混合设计出多样化手机2009-02-12 3483

全部0条评论

快来发表一下你的评论吧 !