一个集成滤波功能的低噪声放大器设计原理图

模拟技术

描述

研究意义

随着5G的发展,毫米波通信成为一项关键技术,前端芯片是5G毫米波系统的核心组成之一。GaN工艺由于具有高频率、高功率、高效率等特性是5G毫米波芯片的一个很好选择,然而毫米波GaN射频前端芯片设计在输出功率、效率和系统噪声等方面面临一系列挑战。同时,滤波器在前端中也有着重要的作用,在接收机下变频时,镜像频段处的信号会变频到中频带处,引入干扰,此时滤波器可用于抑制镜像频段处的干扰。而在常见的前端设计中,低噪声放大器和滤波器通常是分开设计的,它们的互连会带来额外的损耗,单独设计在集成电路上的滤波器则会占用较多的面积,不利于电路小型化。

本文工作

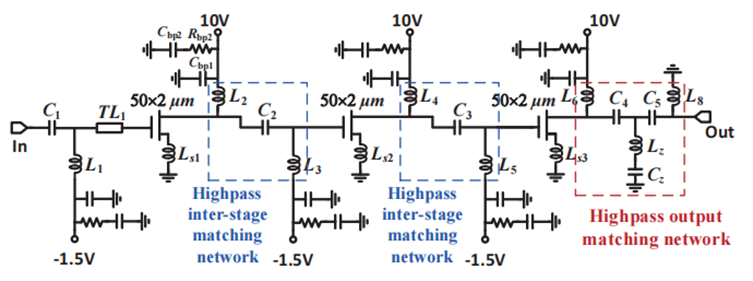

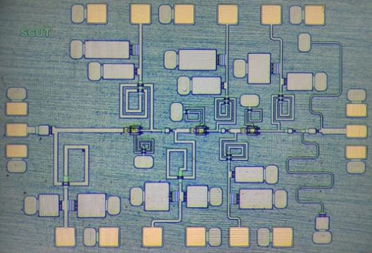

为了解决上述问题,本文提出了一个集成滤波功能的低噪声放大器,该放大器将高通滤波电路融入到阻抗匹配网络中,实现了对低频干扰信号的抑制。提出的电路原理图如图1(a)所示,采用三级放大结构,由于放大器的噪声系数主要由第一级决定,输入匹配电路采用低噪声系数匹配,用以获得尽可能低的噪声系数。级间以及输出匹配由电容和电感构成L-C-L的π型网络,实现高通滤波阻抗匹配。电路采用150-nm GaN-on-SiC工艺实现,具体版图如图1(b)所示,面积约为1.65×1.15 mm2。

(a)

(b) 图1 集成滤波功能的低噪放 (a) 原理图;(b) 版图

本文的创新点如下:

(1)级间匹配网络设计为π形高通滤波阻抗匹配网络,该网络由两个并联电感和一个串联电容组成(L-C-L),在实现复阻抗匹配的同时实现高通滤波响应。

(2)输出匹配中,使用L-C-L-C-L网络,由两个级联的L-C-L的π型网络构成,合并中间的两个并联电感,并由串联LC电路来代替这个电感,使得在低频处引入一个传输零点,在不加大电路尺寸的情况下,可以有效的抑制镜像频段或卫星频段上的杂波。

实验结果

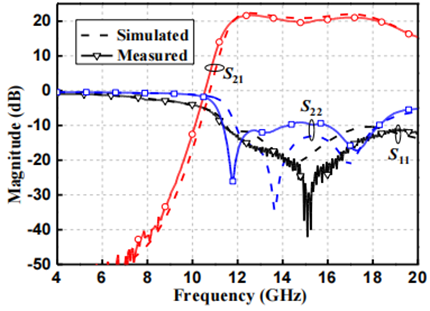

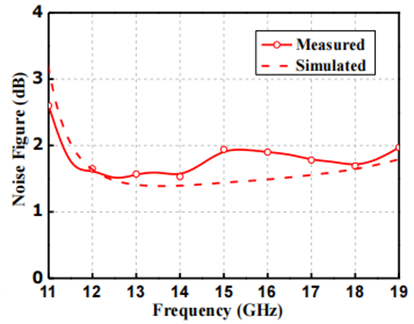

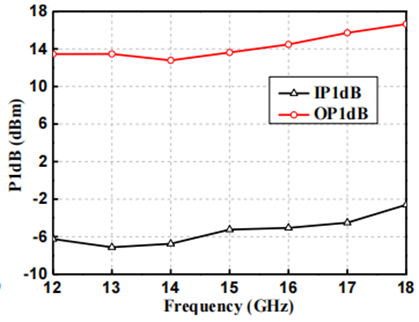

本文对所提出的低噪声放大器进行了测试验证。仿真和测试的结果如图3所示,测试结果显示,该电路工作在12~18.2 GHz频段,频段内最大增益为21.7 dB,3 dB通带为11.6~18.9 GHz,在该频段内可以实现1.5~1.9 dB的噪声系数,整体的直流功耗为530 mW。带外在10 GHz和8 GHz以下频段分别有34 dBc和64 dBc以上的抑制效果,在具有良好的选择性。在通带内,线性度IP1dB大于-7dBm。与先前发表的论文进行了比较,该设计实现了良好的低噪声放大器性能和高阻带抑制。

(a)

(b)

(c) 图3 芯片仿真和测试结果 (a) S参数;(b) 噪声系数;(c) 测试的输入输出1dB 压缩点

Hui-Yang Li, Jin-Xu Xu & Xiu Yin Zhang. A Ku-band image-rejection filtering LNA MMIC in 150-nm GaN-on-SiC technology. Sci China Inf Sci,doi: 10.1007/s11432-023-3849-x

编辑:黄飞

-

宽带低噪声放大器噪声分析2010-05-13 3301

-

低噪声放大器,低噪声放大器型号参数2017-09-11 6252

-

QPB9331低噪声放大器2018-06-13 1457

-

RFFM4527低噪声放大器2018-06-14 1511

-

新款集成低噪声放大器满足市场挑战设计介绍2019-06-26 2241

-

新型宽带低噪声放大器电路设计2019-07-09 2287

-

怎样设计和仿真低噪声放大器?有什么流程?2021-04-07 2552

-

请问怎样去设计一种全集成的低噪声放大器?2021-04-21 1302

-

低噪声放大器介绍2021-07-27 3648

-

低噪声放大器,低噪声放大器是什么意思2010-03-05 4128

-

Ku波段低噪声放大器的设计与仿真2011-10-13 1171

-

低噪声放大器的设计原则2023-07-25 3188

-

低噪声放大器工作原理详解2023-09-05 6893

-

GNSS 低噪声放大器前端模块,集成前滤波器和后滤波器 skyworksinc2025-06-06 159

-

低噪声放大器前端模块,带有 GPS/GNSS 预滤波器 skyworksinc2025-06-09 116

全部0条评论

快来发表一下你的评论吧 !