景芯SoC的图像CSI-2解码技术解析

控制/MCU

描述

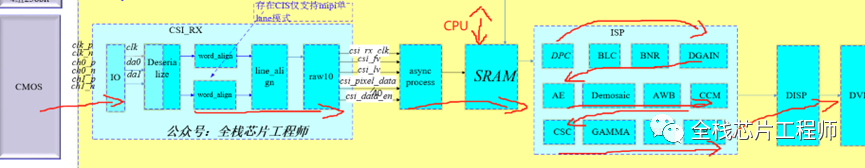

CSI-2针对摄像头,规定了主机与外设的通信数据包格式。MIPI Rx支持RAW10/RAW12/RAW14格式的像素数据解析。

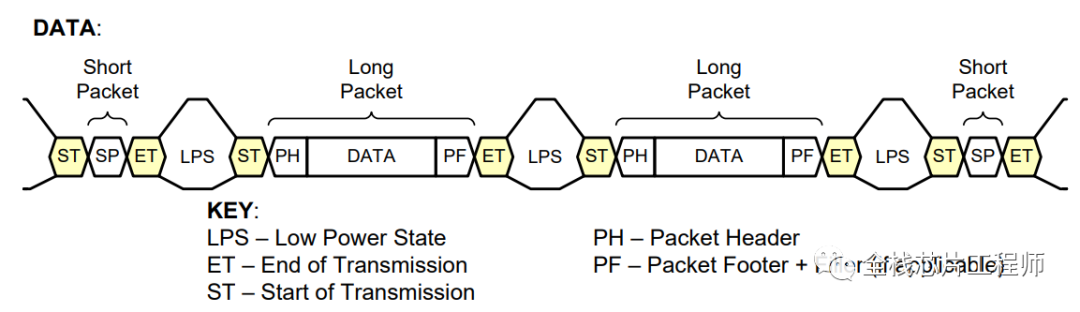

CSI-2的数据包有两种:长帧和短帧。无论是长帧还是短帧,帧的开头都是ST,帧的结尾都是ET。此外,长帧的ST之后还有包头(PH),ET之前还有包尾(PF)。在两次HS传输过程之间,插入的是LP状态,一般是LP11等Control状态,当然也可以进入Escape状态进行LPDT或者进入UPLS。

LPS:Low Power State,封包之间的spacing间距。

ST:Start of Transmission(SoT),封包的起始信号,一般为低速转换为高速的暂态信号。

ET:End of Transmission(EoT),封包的结束信号,一般为高速转换为低速的暂态信号。

PH:Packet Header,32bit表示,封包的标头。

PF:Packet Footer,16bit表示,封包的结尾。

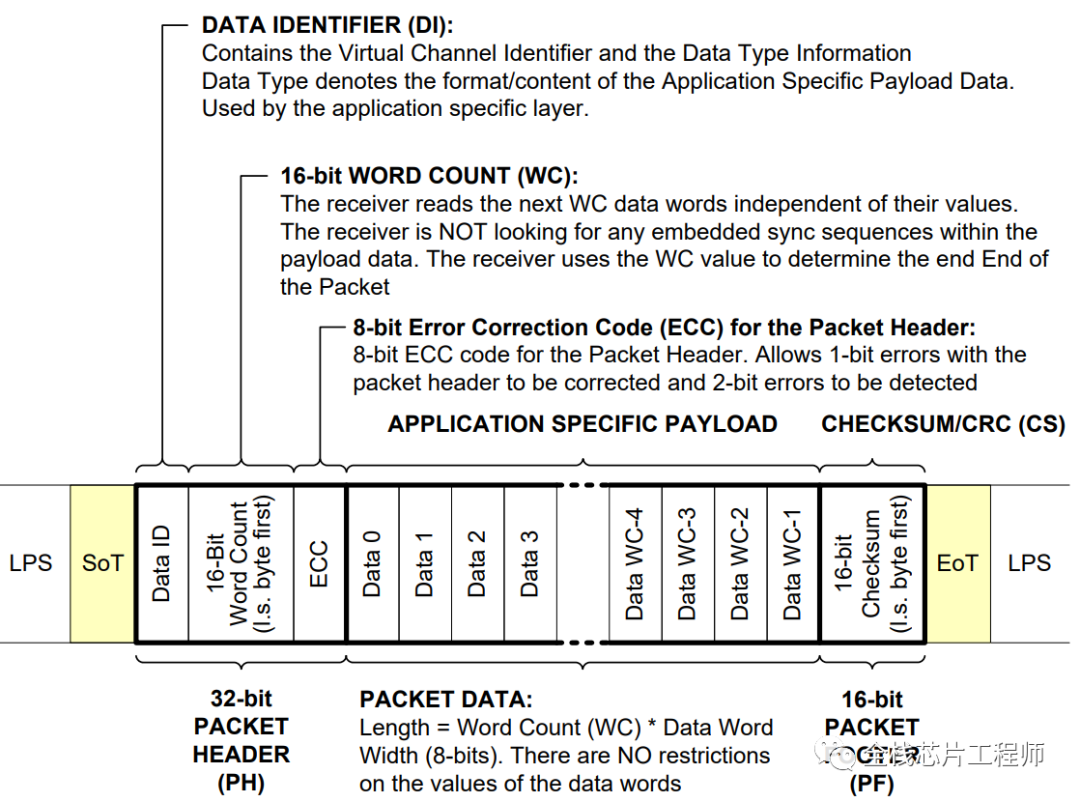

长帧结构

数据标识(DI) :1个字节。包括VC和DT两部分数据,具体结构会在下文中介绍。

数据计数(WC) :2个字节。从PH结尾到PF起始位置中间的填充数据的长度,单位为字节。接收端通过WC来判断包的结尾位置。

错误检测(ECC) :1个字节。采用Hamming Code的方式,用来纠正PH中一位的错误或者发现两位的错误。

数据填充(0~65535 字节) :长度=WC*8bits。对数据内容没有任何限制。

检验和(CS):2个字节。CHECKSUM采用CCITT的16-bit的CRC校检,即x16+x12+x5+x0。CRC只能检测出一个或者多个错误,并不能纠正错误。

DI、WC、ECC共同构成PH,Checksum单独构成PF。

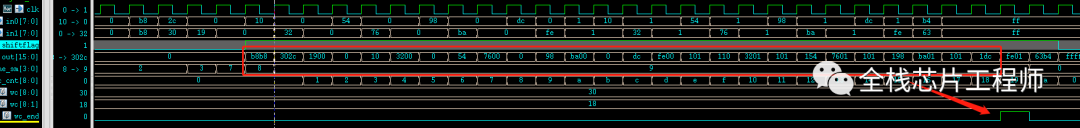

请学员登录服务器查看景芯SoC的设计中,WC的位宽是多少?请debug:

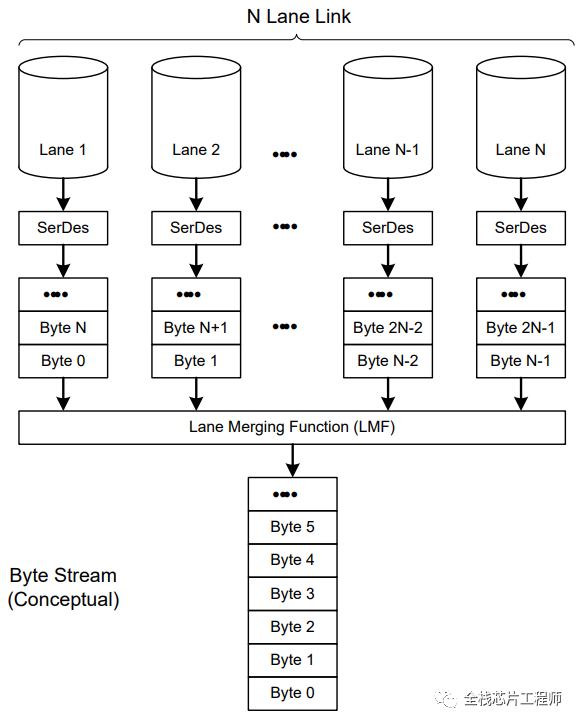

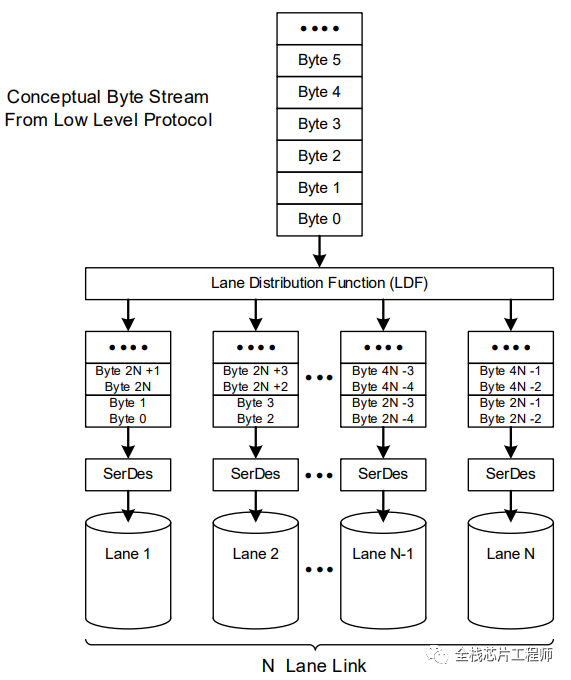

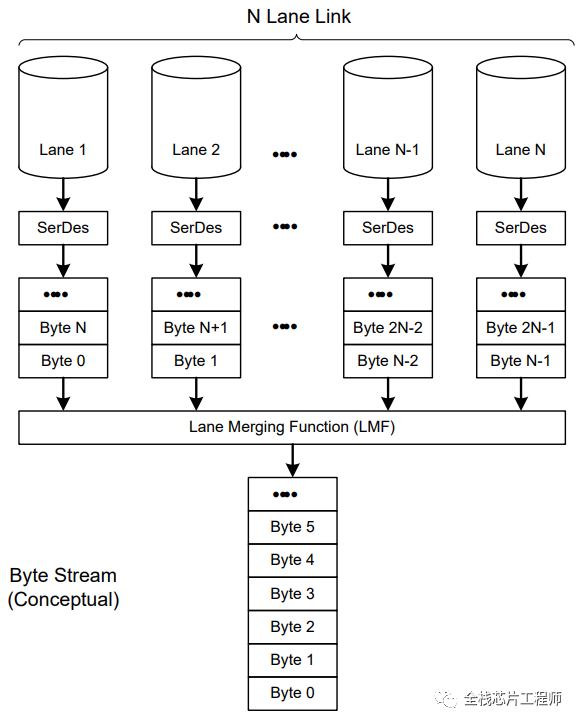

数字电路中经典设计:多条通信数据Lane Merging设计实现

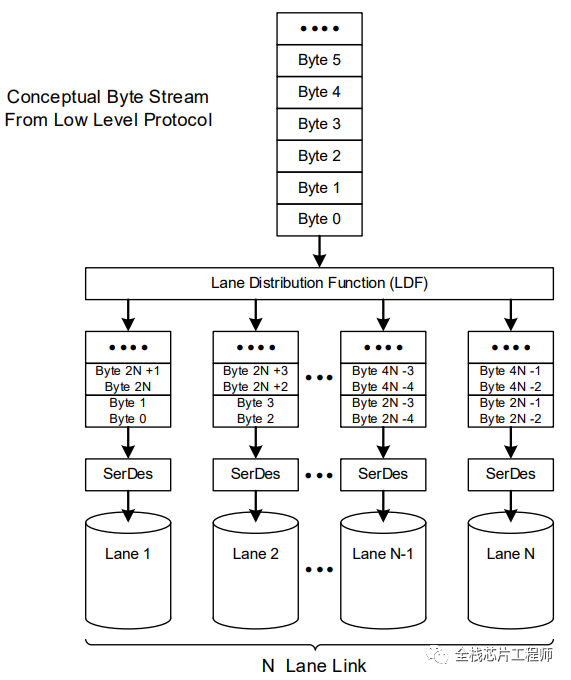

数字电路中经典设计:多条通信数据Lane Distribution实现

【景芯SoC培训营使命】:让每个人都能独立设计一颗自己的MCU芯片!

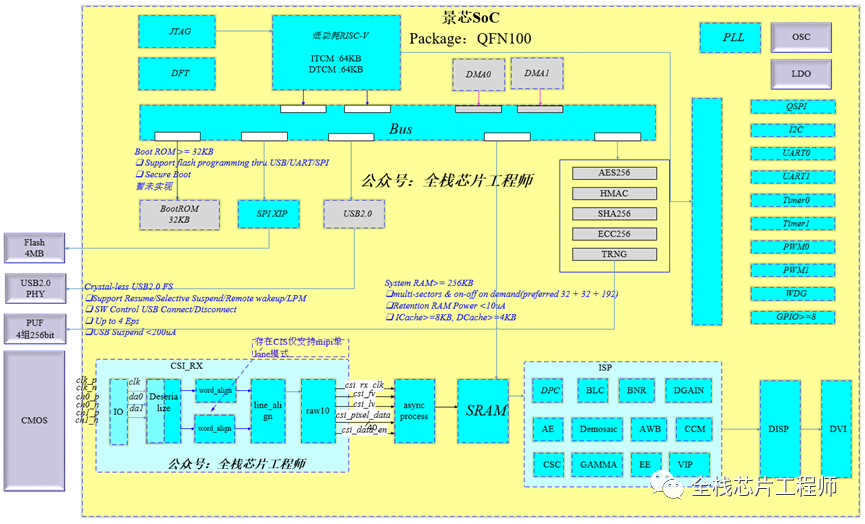

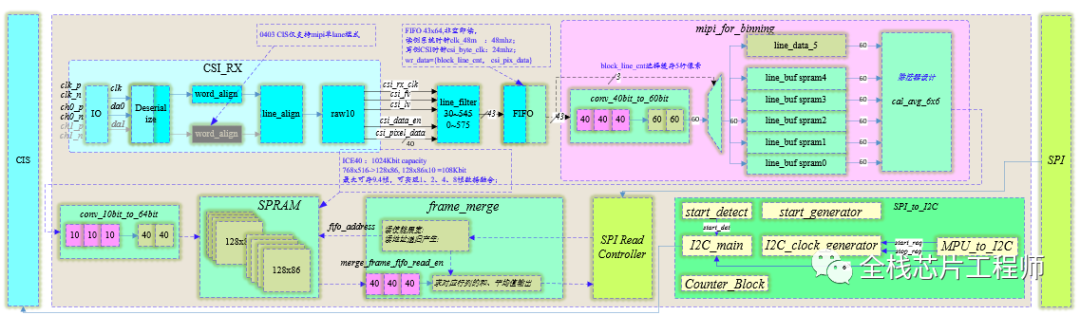

【全网唯一】景芯SoC是一款用于芯片全流程培训的低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、CNN、QSPI、UART、I2C、GPIO、百兆以太网等IP,采用SMIC40工艺设计流片。

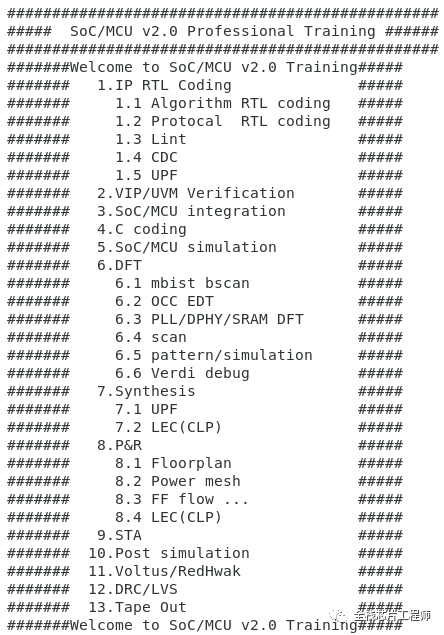

培训数据包括SoC前端设计、DFT设计、低功耗UPF设计、布局布线,提供服务器供大家实践!带你从算法、前端、DFT到后端全流程参与SoC项目设计。更多内容,请报名登录服务器实践,工程数据分割为如下三个部分。

图像处理的数据通路

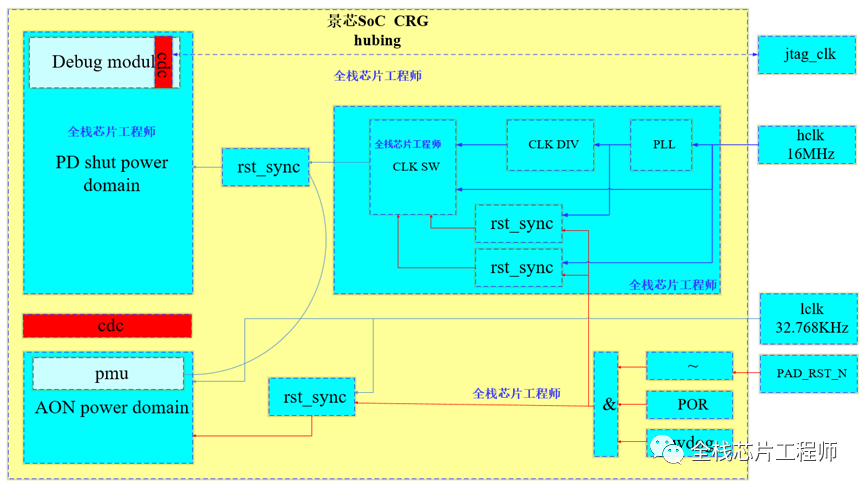

景芯SoC的CRG设计

一键式完成C代码编译、仿真、综合、DFT插入、形式验证、布局布线、寄生参数抽取、PT分析、DRC/LVS、后仿真、形式验证、功耗分析等全流程。升级后的芯片设计工程V2.0 flow如下:

SoC一键式执行flow

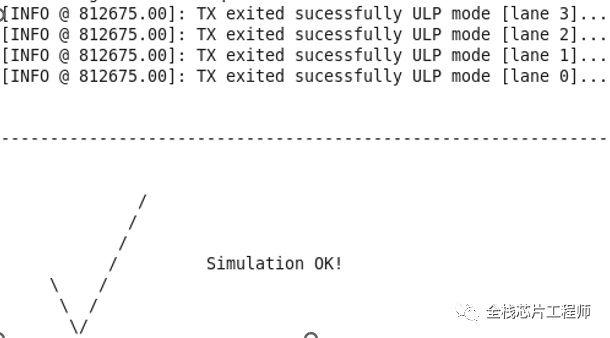

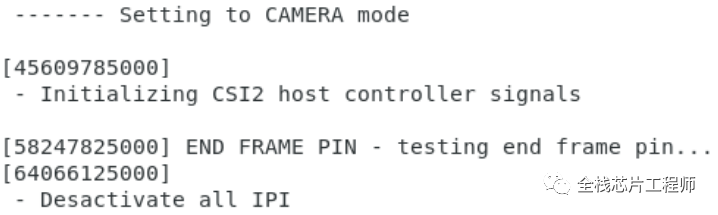

MIPI DPHY+CSI2解码

数字电路中经典设计:多条通信数据Lane Merging设计实现

数字电路中经典设计:多条通信数据Lane Distribution实现

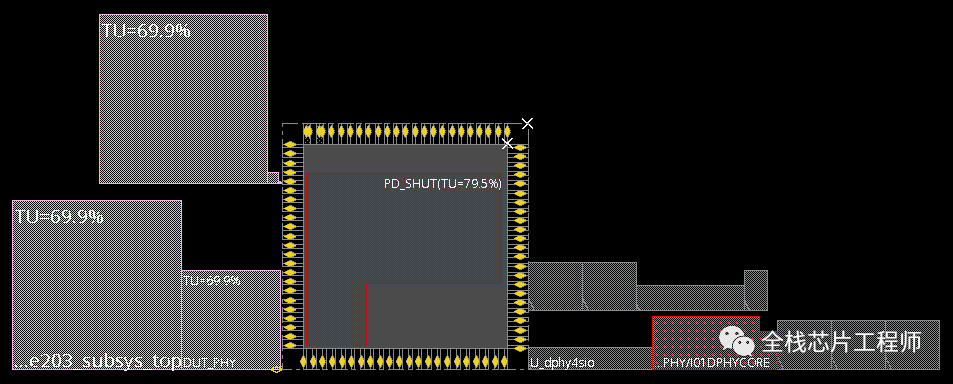

UPF低功耗设计

全芯片UPF低功耗设计(含DFT设计)

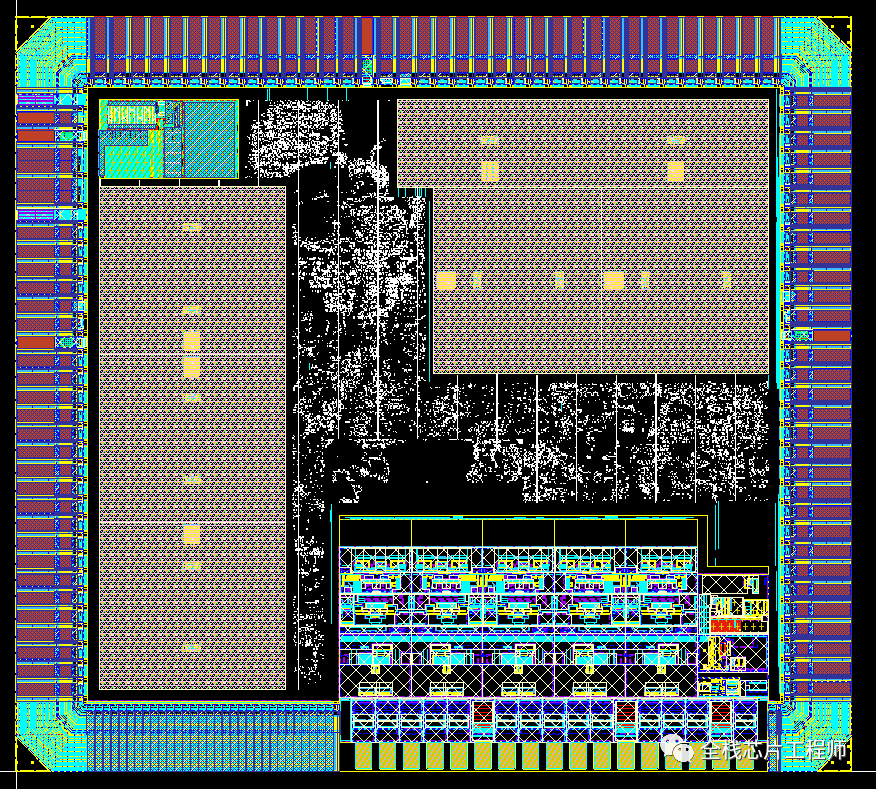

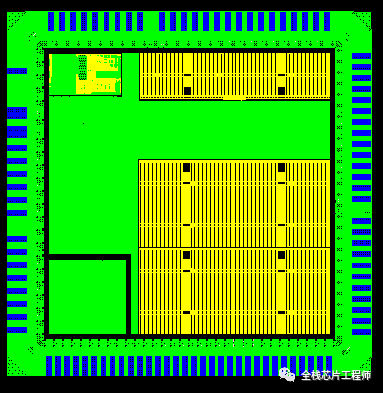

芯片的版图设计V1.0

芯片的版图设计V2.0

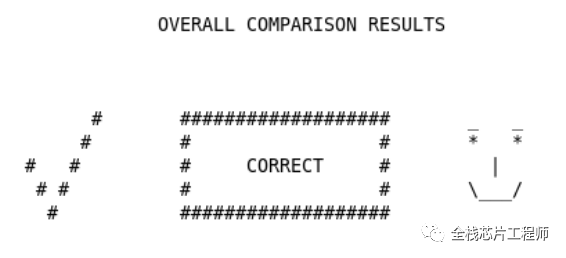

低功耗设计的DRC/LVS,芯片顶层的LVS非常具有挑战性!业界独一无二的经验分享。

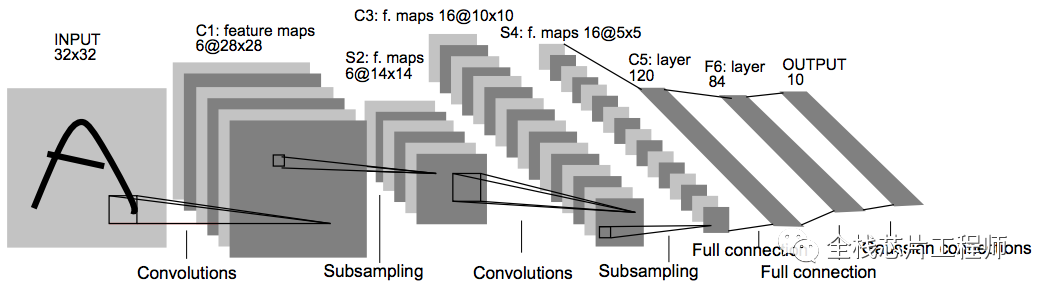

CNN图像识别

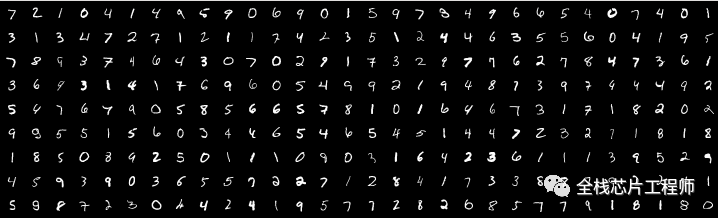

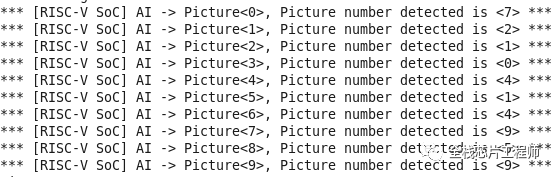

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

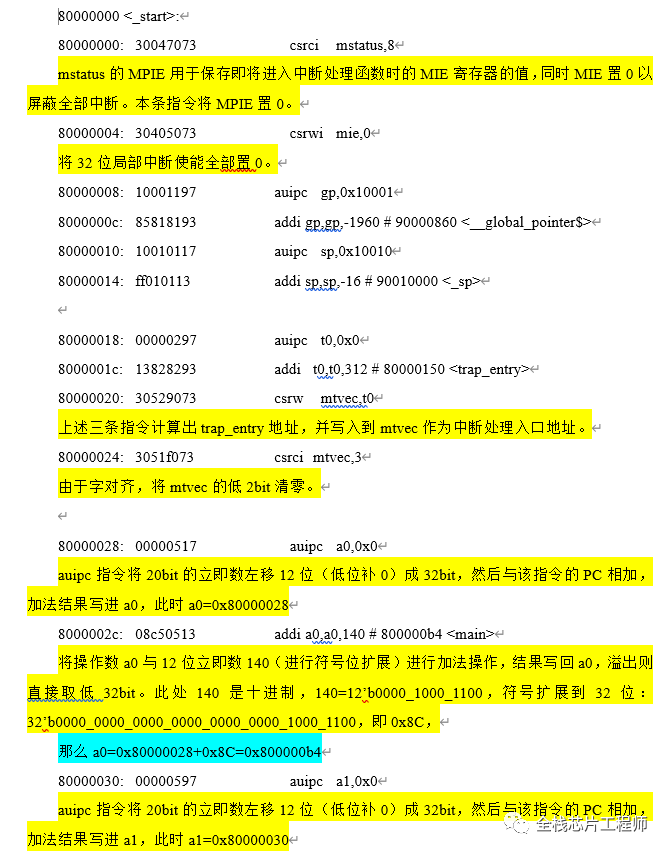

CPU启动指令分析

编辑:黄飞

-

移动行业处理器接口MIPI CSI-2接收桥参考设计2020-04-29 2601

-

基于MIPI的移动行业处理器接口CSI-2发送桥2020-05-01 2439

-

具有MIPI CSI-2输出的汽车ADAS参考设计2022-09-14 2135

-

如何为RAW10位设置MIPI CSI-2和/或Pixel Link?2023-03-21 826

-

美高森美公司推出新的图像/视频解决方案 用于支持带MIPI CSI-2接口的图像传感器2018-05-02 2354

-

MIPI CSI-2协议的简介CSI-2有什么功能和结构与组成等资料免费下载2018-09-18 3268

-

基于MIPI CSI-2 Receive Bridge图像传感器的参考设计2021-01-14 1500

-

基于MIPI CSI-2 Transmit Bridge图像传感器的参考设计2021-01-15 1328

-

AN-1337:ADI视频解码器与MIPI CSI-2接收器连接的设计考虑2021-04-19 1050

-

MIPI CSI-2 相机规格增加了先进的始终在线成像解决方案2022-08-19 2154

-

MIPI CSI-2 RX Subsystem IP介绍和PHY实现浅谈2023-07-07 4337

-

MAX96717:CSI-2至GMSL2序列器数据表 ADI2023-10-09 199

-

MAX96714: Single GMSL2/GMSL1 to CSI-2 Deserializer Data Sheet MAX96714: Single GMSL2/GMSL1 to CSI-2 Deserializer Data Sheet2023-10-12 146

-

基于Microchip MIPI CSI-2 Transmitter FMC卡的技术解析与应用实践2025-09-29 1102

-

STEVAL-CAM-M0I MIPI CSI-2套件技术解析与应用指南2025-10-20 754

全部0条评论

快来发表一下你的评论吧 !