看看两个使用Verilog HDL设计的简单电路

电子说

描述

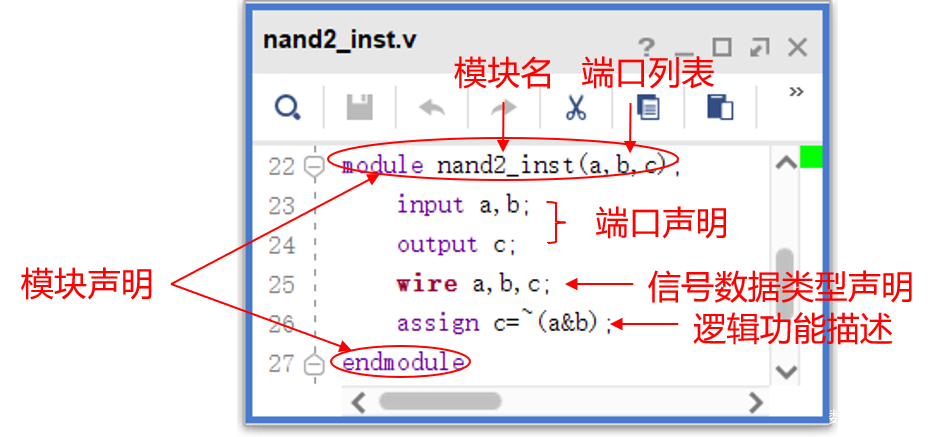

举例:与非门

与非门的Verilog 描述如下图所示,源程序文件的后缀为.v。

Verilog语言的基本描述单元是模块,也就是module。可以看到每一个功能模块都是以module开始,endmodule结束的。一个.v文件可以同时包含多个这样的模块。但是,我们建议大家一个.v文件只包含一个模块,这样便于程序的管理、调试以及复用。

在模块声明中还包含这个模块的名称,以及端口列表,模块就是通过这些端口与其他功能模块进行通信的。我们可以将模块看作一个具有特定功能的电路或集成芯片,端口就相当于这个电路的引脚。

这个与非门模块包含了abc三个端口,那么这些端口哪些是输入,哪些是输出呢,我们需要对其进行声明。并且还要声明这些端口的类型,最常用的就是wire和reg两种类型,其中wire是默认类型,可以省略。后续我们会详细讲解,这里不多做介绍。接下来就是模块的主体部分“逻辑功能描述”,这里使用的是组合逻辑常用assign连续赋值语句。

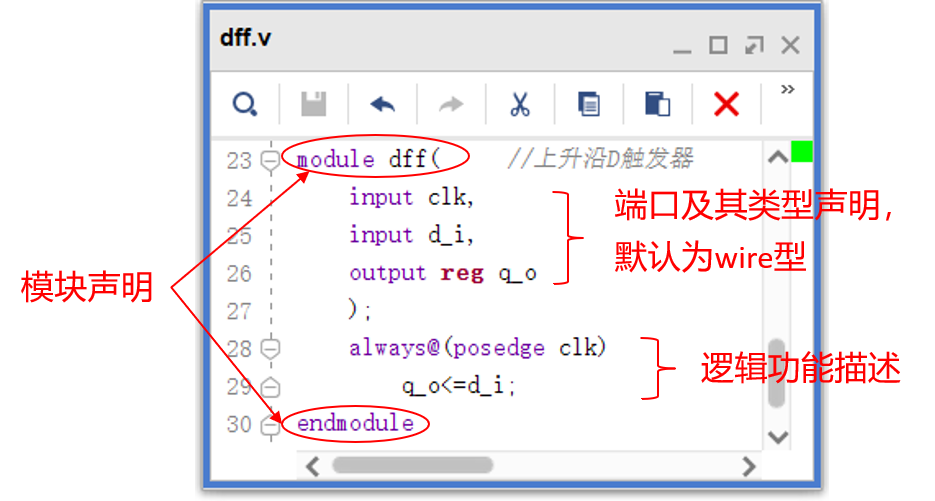

举例:D触发器

再来看一个简单的上升沿d触发器的例子,如下图所示。

D触发器是时序电路的基本组成单元。可以看到模块声明和刚才的格式略有不同(两种格式均可),但整个模块仍然是以module开始,endmodule结束的。module后面是模块名,这里模块名后面的括号中将端口声明和端口类型声明放在了一起,这是vivado自动生成的格式。

这里的clk和d_i是输入信号,没有指明类型,则默认为wire型。q_o是一个reg类型的输出端口。接下来就是逻辑功能描述,这里采用了时序逻辑主要使用的always语句。

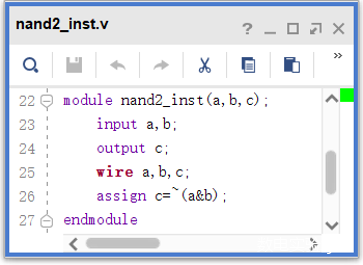

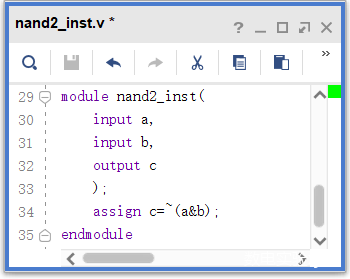

两种端口声明格式

下面是与非门模块的两种描述格式。

总结

- 一个Verilog HDL模块是以module开始,endmodule结束的。

- module后面是模块名,是所设计电路的标识符。

- 模块名后面的括号中是模块的端口名,使用逗号隔开,最后一个端口后面没有标点符号。

- 端口及其类型声明:端口还需要定义是输入还是输出,以及端口信号的类型是wire型还是reg型,这些都可以放在端口名后面的括号中一起声明。此外,在模块中所使用的一些内部信号和数据对象也要进行数据类型声明。

一般使用assign赋值的信号声明为wire型,在always或initial语句中赋值的信号声明为reg型。还可以使用参数来定义常量,增加程序的可读性。Verilog的数据类型有很多,但80%的情况只用到这三种。

- 模块的主体用于描述模块的逻辑功能。常用的有:① assign连续赋值语句,多用于描述组合电路。② always语句可以描述时序逻辑也可以描述组合逻辑。③ 还可以通过实例化已有的模块的方式来建立新的模块,像搭积木一样快速搭建一个系统。

-

Verilog HDL入门教程-Verilog HDL的基本语法2022-01-07 2387

-

Verilog HDL语言是什么2021-11-08 1870

-

Verilog HDL verilog hdl和vhdl的区别2021-07-23 12300

-

Verilog HDL基础语法入门2021-05-06 1063

-

Verilog HDL的礼物-Verilog HDL扫盲文下载2021-04-30 1167

-

如何使用Verilog HDL描述可综合电路?2021-04-04 5168

-

Verilog HDL入门教程之Verilog HDL数字系统设计教程2018-09-20 2457

-

Verilog HDL入门教程2016-07-15 1133

-

Verilog+HDL实用教程-电科2016-05-11 752

-

Verilog HDL电路设计指导书—华为2011-09-07 1532

-

Verilog HDL程序基本结构与程序入门2010-02-08 2629

-

Verilog-HDL实践与应用系统设计2009-11-14 1104

全部0条评论

快来发表一下你的评论吧 !