便携式FPGA实验平台EGO1介绍

可编程逻辑

描述

口袋实验平台EGO1是赛灵思大学计划官方合作伙伴依元素科技有限公司与上海交通大学联合开发的便携式FPGA实验平台。

板载芯片: 该平台板载了Xilinx 28nm工艺的Artix-7系列FPGA芯片,型号为XC7A35T-1CSG324C。

其中,A表示Artix-7系列,35表示逻辑单元数量大约是35k,-1是速度等级,数字越大速度等级越高,csg是芯片的封装形式,324表示芯片有324个引脚。

FPGA芯片的引脚都排列在芯片的背面。有关该芯片片内资源可在赛灵思官网搜索ds180进行下载查看。

板卡供电: 可以通过Type-C接口连接pc机,也可以在这里外接5V的直流电源。在板卡的背面有电压转换电路,负责将+5V的供电电压转换为板卡所需要的各类工作电压。

例如,内核电压和Block Ram工作电压为1.0V,辅助电压为1.8V,而IO供电电压为3.3V。内核电压是FPGA内部逻辑的工作电压,FPGA器件的功耗主要来自内核功耗;辅助电压用于给FPGA内各功能模块的互联资源供电。

**系统时钟:**由 100MHz 的时钟芯片提供,输出的时钟信号直接与 FPGA 全局时钟输入引脚(P17) 相连 。设计中所需要的其他频率的时钟信号,可以使用硬件描述语言设计分频电路也可以直接使用IP核产生。

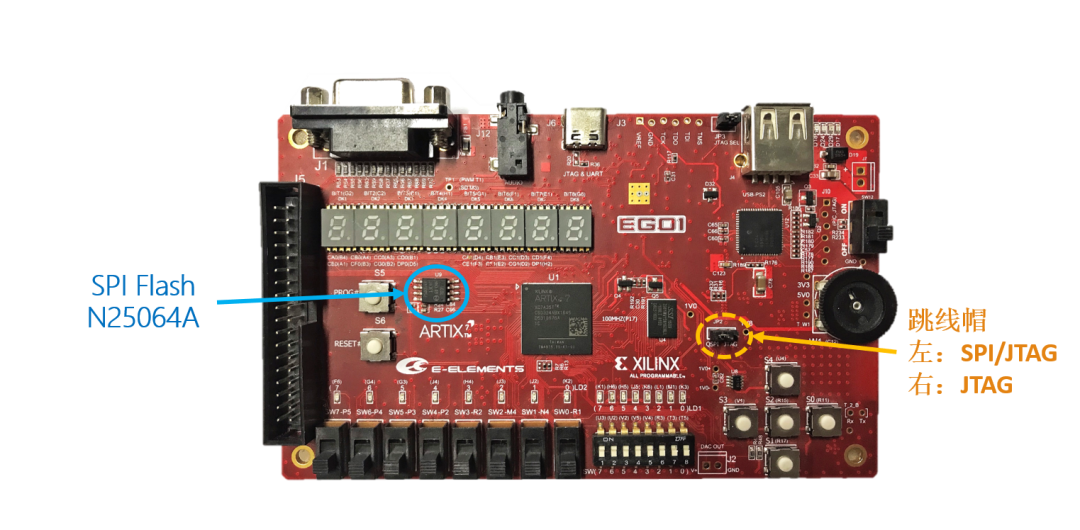

配置方式: FPGA的配置有两种方式。

①一种是通过usb转JTAG接口,也就是用于供电的Type-C接口进行配置,将程序直接配置到fpga中,进行运行。此方式的配置文件后缀为.bit,由vivado自动生成。

由于一般的FPGA都是基于SRAM工艺,断电后数据消失,上电需要重新进行配置。一般在调试程序时,采用这种配置方式,速度较快。

②如果设计要脱机运行,可以采用SPI Flash上电自启动配置方式,需要vivado设置产生后缀为.bin的配置文件,然后烧录到配置芯片中,也就是板载的FLASH中。当上电时,fpga会自动读取FLASH中的配置数据。

这里的跳线用来选择配置方式,跳线帽在左,两种方式都可以,跳线帽在右,则为JTAG配置模式。详细的配置方法参考,ug470文档。

SRAM: 板卡还搭载了一个8M容量的SRAM,用于FPGA存储容量的扩展。

通用I/O:

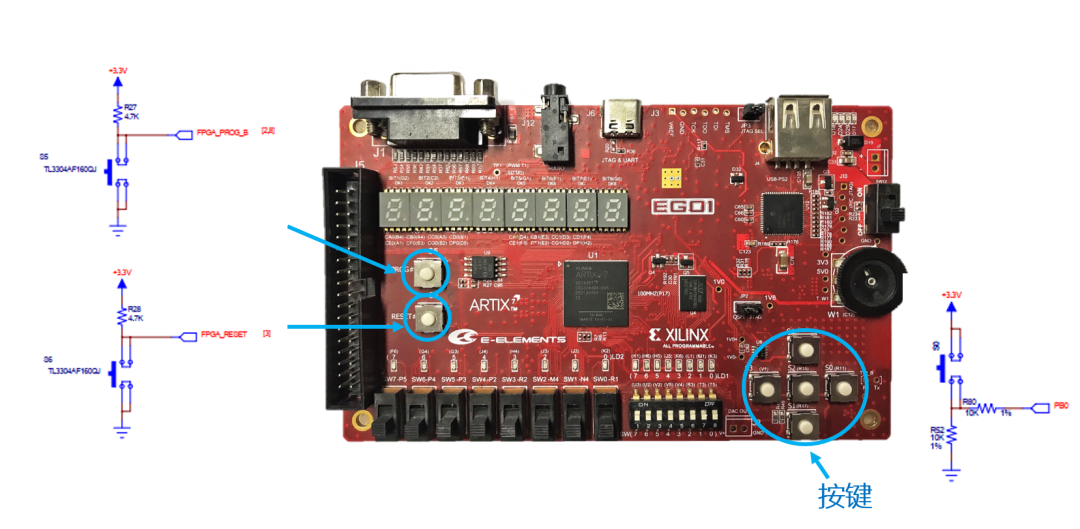

--按键(输入): 板卡左边有两个按键,上面的S5用于擦ca除配置(重配置引脚,重新加载配置代码),下面的S6可以作为低电平复位按键。板卡右下方也有五个按键供用户使用。

这些按键按是低有效还是高有效呢?我们需要查找板卡的电路图,电路图是我们要经常查看的文档,是第一手资料。我们要使用按键,要点灯,点亮数码管,输入输出引脚应该置高还是置低,要根据电路图的设计来确定。

从电路图可用看出,左边这两个按键在没有按下的时候引脚连接的是3.3V电压,是高电平,当按键按下的时候,引脚接地,电位被拉低,因此,按键按下是逻辑0。而右边的按键在没有按下时为逻辑0,按下时接通3.3V电压,为逻辑1.

--开关(输入): 通用IO还包括8个独立的拨码开关,和1个8位的DIP开关,总共可提供16位输入。

**--LED灯(输出):**还有16个led灯,可用来指示输出逻辑,输出高电平时被点亮。

--数码管(输出): 板卡还提供有8个七段数码管。

--扩展I/O引脚: 板卡最左边引出32个双向IO,用来作I/O扩展 。最上面两个引脚是3.3V电压,下面两个是接地。最下面的七对引脚可以作为XADC的差分输入。

**其他接口:**EGO1还提供有VGA接口,音频输出接口,以及可以连接键盘鼠标的USB接口。通过这些接口,同学们可以进行很多有意思的项目设计。例如,大家都很感兴趣的游戏设计,都是通过EGO1实现的。

通信接口包括UART接口,也使用的是这里的Type-c接口,接上主机后会自动识别为串口。板卡背面还有蓝牙模块。

**XADC:**FPGA芯片内部集成了两个 12bit 位宽、采样率为 1MSPS 的 模数转换器,叫做XADC。通用IO中的部分引脚可以作为XADC的差分输入。通过板卡自带电位器可以提供0-1V的模拟电压。相关使用方法可以查看文档ug480。

**DAC:**板卡还集成了 8 位的数模转换芯片DAC0832。

-

便携式示波器的技术原理和应用场景2024-10-24 3828

-

ego1原理图介绍2023-12-21 1238

-

EGO1电路图完整版免费下载2021-12-31 2519

-

ISO14443介绍2021-07-27 1963

-

EFR32介绍2021-07-23 2439

-

便携式产品具有低功耗意识的FPGA设计方法是什么?2021-05-08 2457

-

FPGA能否满足便携式存储应用的低功耗要求?2021-04-29 1531

-

Xilinx EGO1口袋实验开发板全套资料合集2020-11-17 3709

-

digilent适便携式电路实验室介绍2019-11-26 3720

-

Xilinx EGO1 口袋实验开发板全套资料2018-10-05 15323

-

EGO1配备的FGPA(XC7A35T-1CSG324C)教学平台,哪里购买2018-04-20 4628

-

基于DSP与FPGA的便携式超声探伤仪2017-10-19 1177

-

便携式产品具有低功耗意识的FPGA设计方法2009-11-30 943

全部0条评论

快来发表一下你的评论吧 !