FPGA的引脚是如何命名的?引脚是如何分布的?

可编程逻辑

1396人已加入

描述

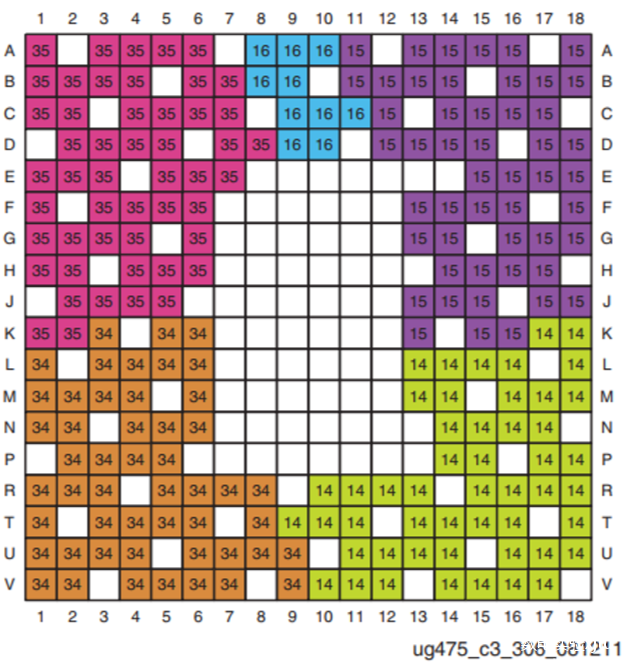

FPGA的引脚排布在芯片背面,以EGO1板载芯片XC7A35T-1CSG324C 为例,下图中每个小格代表一个引脚,共有18行18列,共324个引脚。

XC7A35T I/O Bank

FPGA引脚命名通过英文+数字的方式,英文表示所在行,数字表示所在列。

在EGO1上可以看到,在每一个通用IO的丝印标识名称旁边都有一个英文加数字的标识,就是该外设与FPGA相连接的引脚名称。每一个外设与FPGA的具体连接,在EGO1开发板的电路原理图中都可以找到。

例如,开关SW0连接的是FPGA的R1引脚。当使用SW0作为输入时,就是要读入R1引脚的状态。因此,在vivado设计中,进行管脚约束时,要将模块的输入端口约束到R1引脚上。

XC7A35T-1CSG324C所有324个引脚包括了:

① 210个用户可用引脚。这些引脚被划分为50个一组的Bank,在I/O Bank 图中,同一颜色的引脚为一个Bank。可以看出该芯片有5个Bank,分别是Bank34,Bank35,Bank15,Bank14,以及部分bank16。这些引脚都可以作为普通IO使用,其中有一些是多功能引脚,当有特殊要求时,只能使用相对应功能的IO,例如差分输入引脚,高时钟输入引脚等等。

② I/O Bank 图中,空白没有标注的引脚为专用引脚(芯片配置,全局时钟)和电源引脚,有固定的功能和作用,用户不能占用。中间空白的部分主要是内核电压、辅助电压,Bram电压的供电引脚。

③ 每个I/O Bank中,有一些白色小方块,这些空白处大都是I/O的电源和地 ,不同的I/O Bank可以使用不同的电平标准单独供电。外部信号输入FPGA的电平、IO Bank供电电压和约束文件里声明必须一致。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

IN628E的引脚复用橙群微电子 2024-05-21

-

#硬声创作季 01-引脚醉 2022-10-26

-

Pico板具有哪些特性?引脚是如何分布的?2022-01-20 1598

-

FPGA怎么对引脚进行分块?DDR3与FPGA的引脚连接2021-11-29 8479

-

SPI引脚分布2021-08-11 2493

-

FPGA配置引脚说明2021-02-03 6494

-

FPGA的引脚交换是怎么实现的2020-01-20 4721

-

如何在函数中给引脚命名?2019-07-10 1199

-

原理图和符号引脚如何命名和检查2018-11-27 2810

-

FPGA上的引脚和区域约束语法介绍2018-07-14 12157

-

FPGA引脚配置问题2017-06-12 4205

-

Xilinx-FPGA-引脚功能详细介绍2016-09-01 1068

-

关于FPGA引脚分配的问题2013-01-06 9079

-

fpga的引脚问题2012-10-27 2968

全部0条评论

快来发表一下你的评论吧 !