浅析去补偿与完全补偿运算放大器及实现补偿的外部方法

电子说

描述

米勒频率补偿(Miller frequency compensation)使得可以使用相当小的补偿电容Cf值。这是非常需要的,不仅因为Cƒ可以在片上制造,而且因为它导致比例如并联电容补偿更快的动态。这是因为压摆率(slew rate,),开环带宽和全功率带宽与C f成反比。

现在,就Cƒ的大小而言,对闭环增益的补偿一直到单位增益是最保守的。有许多应用涉及闭环增益大于最小值,例如大于Amin = 10 V / V,这将适用于更小的Cƒ,从而享受更快的动态。

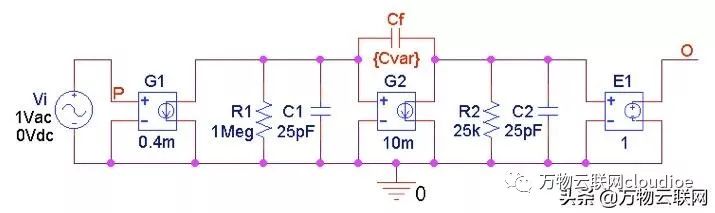

让我们使用我们运行的PSpice电路示例,首先在我的运放频率补偿文章中介绍的,来比较去补偿(decompensation)与完全补偿:

图1

图1. PSpice电路绘制完全补偿和去补偿(decompensation)的开环增益。

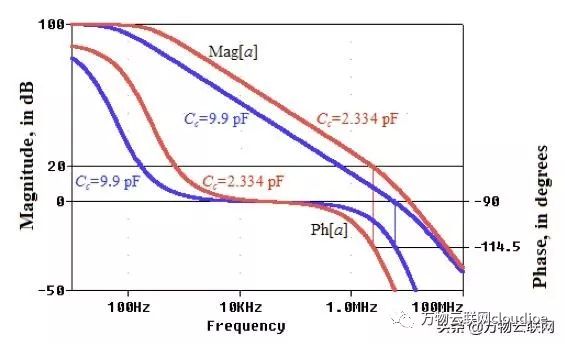

PSpice的结果如下图所示:

图2

图2.具有完全补偿的开环增益(对于闭环增益≥0dB,Cƒ= 9.90 pF)和去补偿(decompensation)(对于闭环增益≥20dB,Cƒ= 2.334 pF)。两种补偿均享受φm≥65.5°

结果引出以下观察:

在完全补偿(Cƒ= 9.90 pF)的情况下,0 dB增益的交叉频率ƒx≈5.86MHz,相位裕度φm= 65.5°。此外,如果我们将全补偿运算放大器配置为20 dB闭环增益,则它具有ƒx≈633kHz和φm≈87°,甚至比0 dB增益更大。

通过去补偿(decompensation)(Cƒ= 2.334 pF),20 dB增益具有ƒx≈2.37MHz(带宽比完全补偿更宽),并且仍然是φm= 65.5°。但是,如果我们将去补偿(decompensation)运算放大器配置为0 dB闭环增益,它将具有ƒx≈11.1MHz和φm≈24°,这是一个很差的余量,因为去补偿(decompensation)的器件意味着增益≥20dB。当φm≈24°时,20-dB增益将呈现约7%的峰值,并且瞬态响应具有约50%的过冲,这两者通常都是不可接受的。

现在让我们继续考虑如何利用外部因素在电路中实现补偿;例如,电阻器。

使用电阻器进行外部补偿

尽管失代偿运算放大器的闭环增益高于Amin(在上例中为Amin = 20 dB),但它们的优越动态性使其对于增益低于Amin的应用也具有吸引力。

但这会降低相位裕度φm,因此用户有责任在外部补偿电路,以便将φm保持在所需的水平。

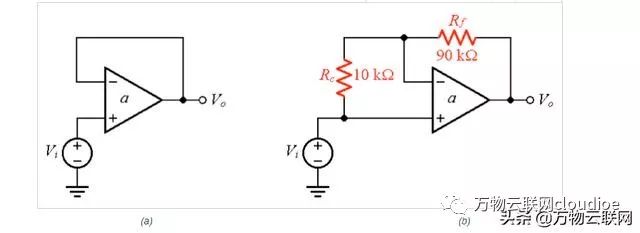

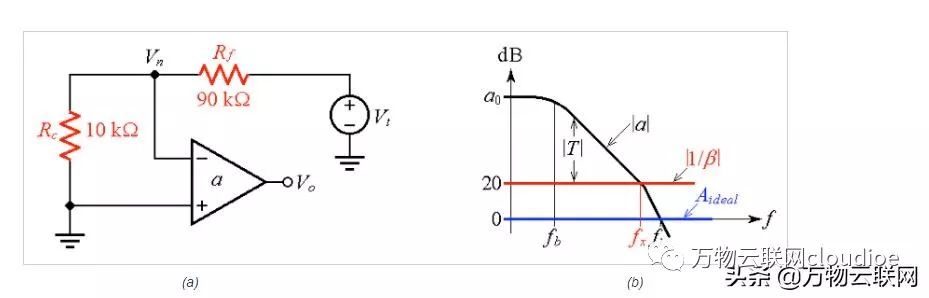

为了说明,让我们将图1的运算放大器用于Cƒ= 2.334 pF的失代偿形式,让我们将其配置为电压跟随器操作,如图3(a)所示。

图3

图3.电压跟随器:(a)去补偿(decompensation),(b)外部补偿φm≈65.5°。

如上所述,该电路的相位裕度仅为φm≈24°。我们如何将其提高到φm= 65.5°?一个简单的解决方案是将其1 /β曲线提高到20 dB,同时仍然确保单位增益。我们通过以1比9的比例连接电阻对Rc-Rf来实现这一点,如图3(b)所示。理想化极限a→∞的闭环增益仍然存在:

方程1

(这种情况是因为对于a→∞,运算放大器输入端的电压趋于零。这意味着通过Rc的电流为零,因此通过Rf也是零电流。因此,Rƒ两端的电压为零,所以我们有Vo = Vi。)

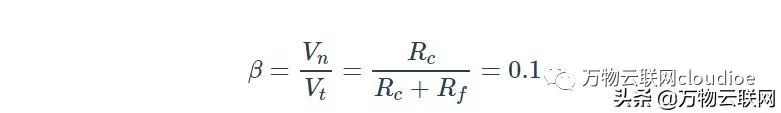

然而,我们通过图4(a)的测试电路找到的反馈因子β是:

或1 /β= 10 = 20 dB(注意本例中1 /β≠Aideal)。

图4

图4.(a)找到图3(b)的电压跟随器的反馈系数β的电路,以及(b)Bode-plot可视化的电路。

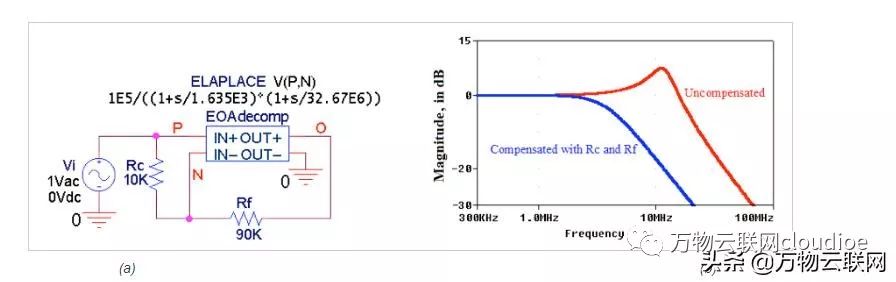

响应如图5所示。

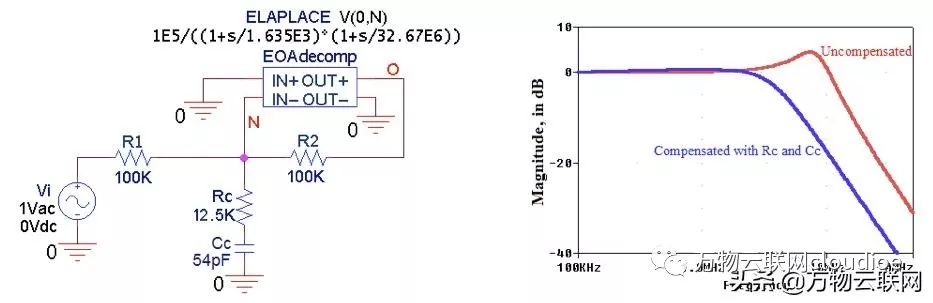

图5

图5.(a)PSpice电路可视化(b)图3的电压跟随器的响应。拉普拉斯模块模拟图2的去补偿(decompensation)响应,用C = 2.334pF获得。

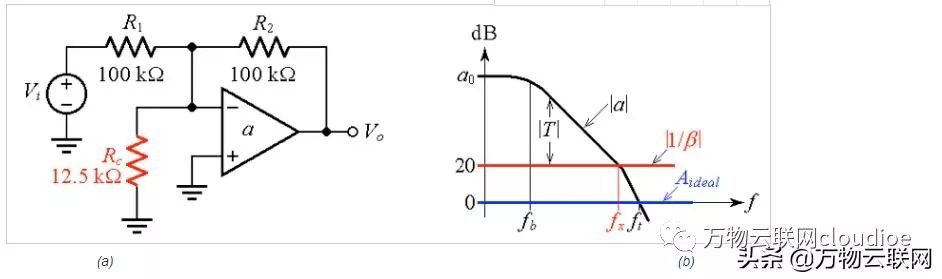

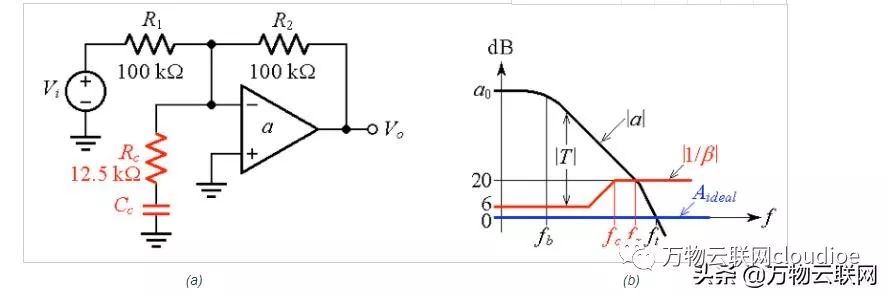

类似的推理线适用于图6(a)的单位增益反相放大器。

图6

图6.单位增益反相放大器的外部补偿。

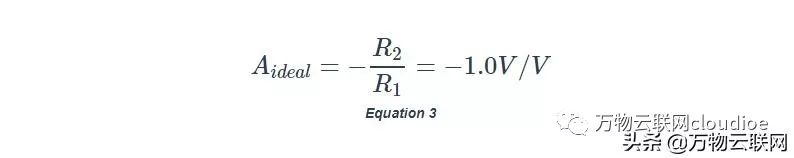

在这种情况下,在极限a→∞,我们有:

方程3

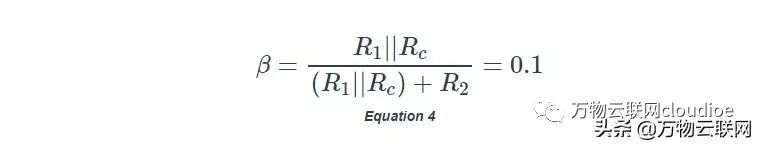

通过观察,现在反馈因子变为:

方程4

在这种情况下,选择Rc以使(R1 || Rc)= R2 / 9。

电阻补偿的应用(和缺点)

专门针对单位增益同相和反相放大器的上述讨论可以很容易地推广到除了单位闭环增益之外的情况,但仍然是1 <(1 + R2 / R1)

该电路是用作同相放大器(Aideal = 1 + R2 / R1)还是作为反相放大器(Aideal = -R2 / R1),只要条件(1 + R2 / R1)

电阻补偿虽然简单,但有两个缺点:

a、任何可以用与非反相输入串联的电压源建模的噪声,例如输入失调电压VOS,都会被放大1 /β,因此也被称为噪声增益。

b、环路增益T =(图4(a)中的aβ= -Vo / Vt)减小(在本示例中为10倍),导致电路的闭环DC精度下降。

输入滞后补偿

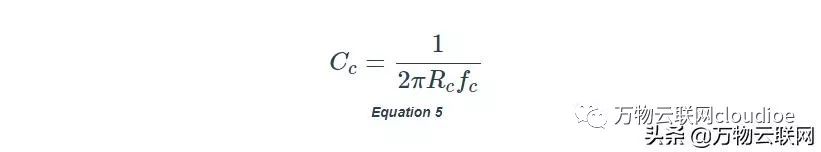

我们可以通过将合适的电容Cc与Rc串联来减轻电阻补偿的限制,如图7(a)所示,用于反相放大器。

图7

图7.(a)单位增益反相放大器的输入滞后补偿,以及(b)波德图可视化。

注意,为了确保所需的相位裕量,我们需要仅在交叉频率ƒx附近欺骗放大器进入所需的闭合速率(ROC),而不是一直到DC。

物理上,1 /β曲线在电容阻抗幅度等于Rc的频率ƒc处断开,或| 1 /(j2πCc| = Rc,给定:

方程5

为了防止相位裕度φm的明显侵蚀,通常将ƒc放置在低于ƒx的十倍左右,或者:

对于图7(a)的电路,这意味着Cc≈54pF。图8的模拟产生测量值ƒx= 2.38MHz和φm= 61°。

图8

图8.(a)PSpice电路到(b)可视化单位增益反相放大器的输入滞后补偿的稳定效应。

外频补偿的另一种方法

输入滞后补偿因在闭环响应中产生零极点双重而臭名昭着,这导致了不可忍受的长建立时间特性。Michael Steffes提出的替代补偿方法避免了这些缺点,如图9所示。

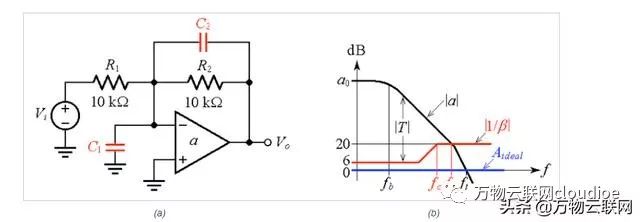

图9

图9.(a)Michael Steffes对去补偿(decompensation)运算放大器的补偿技术,以及(b)波德图可视化。

我们在先前关于杂散输入电容补偿的文章中已经遇到过这种类型的电路,因此在那里做出的许多考虑也适用于本电路,唯一的区别是现在C1是有意的。

我们有兴趣开发两个条件来指定C1和C2的值。在高频时,阻抗C1和C2的幅度比R1和R2小得多,我们可以忽略R1和R2,并说明在高频时我们有1 /β→1 + C1 / C2。

施加1 + C1 / C2 = 20 dB = 10给出了我们电路示例的第一个条件:

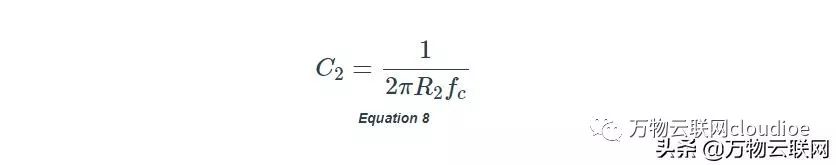

第二个条件源于这样的事实:

所以C2的值取决于我们决定定位ƒc的位置。

我们采用启发式方法,而不是应用Steffes的详细分析,因为这超出了本文的范围。

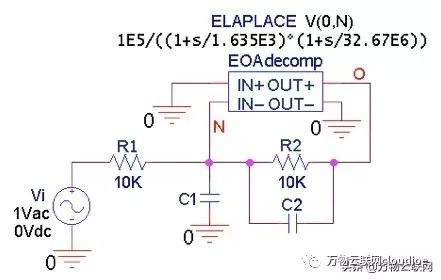

我们从等式(6)和(8)开始,并使用图10的PSpice电路观察AC响应,因为我们通过减少C2逐渐增加ƒc,同时保持等式(7)的条件。

图10

图10.用于绘制图9a的反相放大器的AC响应的PSpice电路。要绘制瞬态响应,请将AC输入源更改为脉冲源。

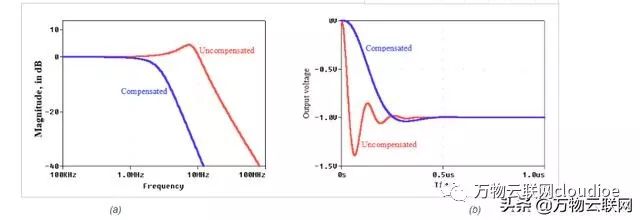

当AC响应刚开始显示峰值时,我们停止。该方法给出C2 = 12pF和C1 = 9C2 = 108pF,导致图11的良好响应.AC响应具有2.36MHz的-3dB频率。

图11

图11.(a)AC响应和(b)图10的反相放大器的阶跃响应。

值得指出的是,通过将C1的值改变为9C2-Cn,可以将存在于反相输入端的任何杂散电容Cn并入该补偿方案中。因此,如果Cn = 20 pF,那么我们使用C1 = 88 pF。

在本文中,我们研究了去补偿(decompensation)和外部补偿的运算放大器。我们使用示例电路来演示可以通过各种方式实现运放频率补偿,并考虑每种方法的优缺点。

-

应用笔记1604:去补偿运算放大器2024-09-29 410

-

如何使用米勒电容对运算放大器补偿?2023-09-18 6536

-

运算放大器的补偿方法:Miller补偿2022-12-19 17732

-

如何利用RISO及CL补偿稳定驱动容性负载的运算放大器?2021-04-13 2307

-

关于运算放大器的相位补偿如何选择?2021-04-06 3145

-

运算放大器频率补偿/内部补偿解析2020-11-19 9974

-

四路解补偿低噪声的失衡运算放大器2020-06-19 2080

-

想知道分立式3运算放大器仪表放大器是否需要任何补偿电容?2019-03-09 2148

-

二级米勒补偿运算放大器设计2016-07-25 1534

-

运算放大器真流补偿漂移测试电路2009-09-24 1106

-

带温度补偿断点的非线性运算放大器2009-09-05 789

全部0条评论

快来发表一下你的评论吧 !