超结VDMOS的结构和应用

描述

超结VDMOS是一种发展迅速、应用广泛的新型功率半导体器件。

它在常规纵向双扩散金属氧化物半导体(VDMOS)基础上,引入超结(Superjunction)结构,使之既具有VDMOS输入阻抗高、开关速度快、工作频率高、电压控制、热稳定性好、驱动电路简单的特性,又克服了VDMOS的导通电阻随击穿电压急剧增大的缺点,提升了系统效率。

目前超结VDMOS已广泛应用于电脑、手机、照明等消费电子领域、服务器电源、通讯电源等工业电子领域、以及充电桩、车载充电机等汽车电子领域。

一、超结理论

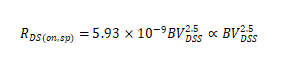

功率器件要得到较高的击穿电压,就必须使用较厚的外延层漂移区与较低的掺杂浓度,常规VDMOS的特征导通电阻与击穿电压关系如下式所示[1]:

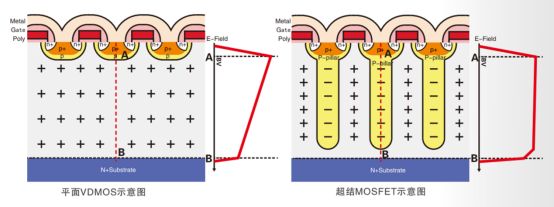

因而特征导通电阻会随着击穿电压的增大而急剧增大,对于常规结构功率器件的导通电阻受此“硅限”的约束而无法进一步降低。在传统的VDMOS结构中,阻断状态时漏端加高电压,Pdody和N型外延层形成的PN结承受了这一电压。如下图左所示外延层的电场近似呈三角形分布,峰值电场出现在上述PN结处,减小漂移区的掺杂浓度和增大外延层厚度,可以增大击穿电压,但特征导通电阻与击穿电压成2.5次方关系增加。

图:平面VDMOS结构与超结MOSFET电场分布图

为了减小功率器件漂移区的导通电阻,1988年飞利浦公司的工程师David J. Coe申请的美国专利[2],首次在横向高压MOSFET中提出采用交替的PN结结构代替传统功率器件中低掺杂漂移层作为耐压层的方法。

1993年,电子科技大学的陈星弼教授提出了在纵向功率器件[3]中用多个PN结结构作为漂移层的思想,并把这种结构称之为“复合缓冲层”(Composite Buffer Layer)。

1995年,西门子公司的J. Tihanyi申请的美国专利[4],提出了类似的思路和应用。

1997年日本的学者Tatsuhiko等人对上述概念进行总结,提出了“超结”(Superjunction)理论[5]。

在超结VDMOS中,耐压层由交替的高掺杂N柱和P柱构成,且N柱和P柱中的掺杂总量相等。在导通状态下,电流从源区经N柱流到漏区,P柱中不存在导电通道,而在阻断状态下,超结VDMOS的漂移区通过P柱的辅助耗尽作用在较低漏电压下就完全耗尽,由于完全耗尽,P柱与N柱的等量异种电荷相互抵消而实现电荷平衡,如上图右所示电场在外延层漂移区中近似于处处相等,因而击穿电压约等于临界电场与漂移区长度的乘积,这使得超结VDMOS的特征导通电阻与其击穿电压近似呈线性关系,而不是传统器件的2.5方关系,进而可以减小特征导通电阻[6]。

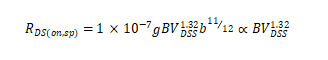

对于超结VDMOS的比导通电阻与击穿电压的关系,可由下式表示[7]:

其中,g为与元胞形状有关的常数,取值范围1~2.5;BVDSS为击穿电压,单位V;b为单位元胞宽度,单位μm;RDS(on,sp)的单位是mΩ.cm2。

图:超结MOSFET突破常规VDMOS硅限

二、超结理论的应用

1998年Infineon公司首次将超结器件商业化,推出了超结VDMOS即“CoolMOSTM”,其P柱是采用多次外延和多次离子注入的方式实现的,CoolMOS显著地降低了导通电阻。目前超结结构主要有两种工艺实现方式:多次外延及深槽刻蚀加外延填充。

(一)多次外延工艺

该工艺是在N+衬底上采用多次外延方式生长很厚的外延层漂移区,每一次外延工艺均伴随一次P型离子注入,随后推结形成连续的P柱。制作一个约40μm深的的外延层漂移区,一般需要进行5到6次外延生长和离子注入。

多次外延与深槽外延方式相比工艺难度较低,但制作超结结构需要多次外延、多次光刻、多次离子注入及推结过程,大大增加了工艺复杂度和制造成本。

图:多次外延工艺超结VDMOS

采用多次外延工艺的公司有Infineon、ST、Fairchild。

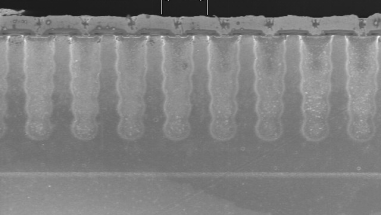

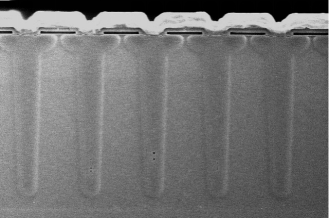

(二)深槽刻蚀加外延填充

该工艺是在N外延层上刻蚀出深沟槽,然后在深沟槽中进行P型外延生长,制作一个约40μm深的P柱,只需进行一次深槽刻蚀及一次深槽外延生长,较多次外延工艺大大简化了工艺步骤,进而降低了生产成本。

图:深槽外延工艺超结VDMOS

采用深槽外延工艺方式的公司有上海华虹、Fairchild、Fuji Electric、Toshiba。

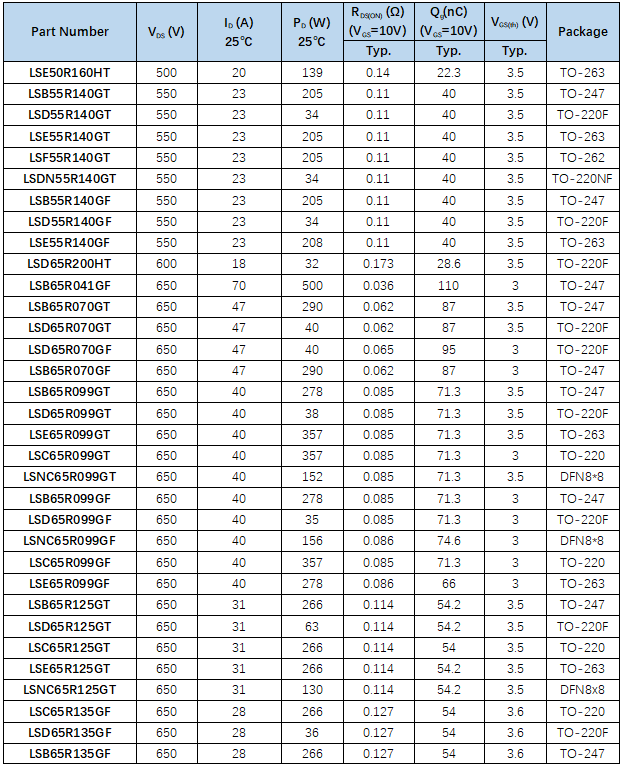

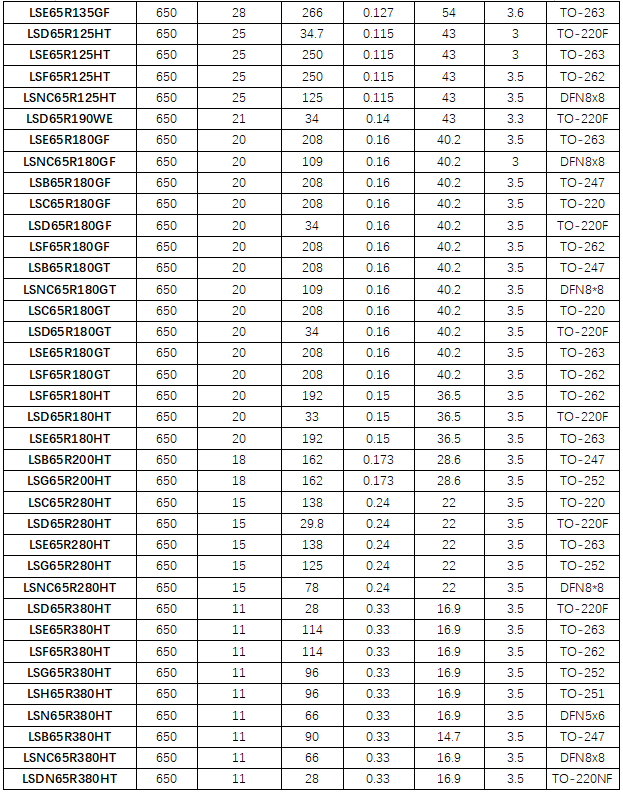

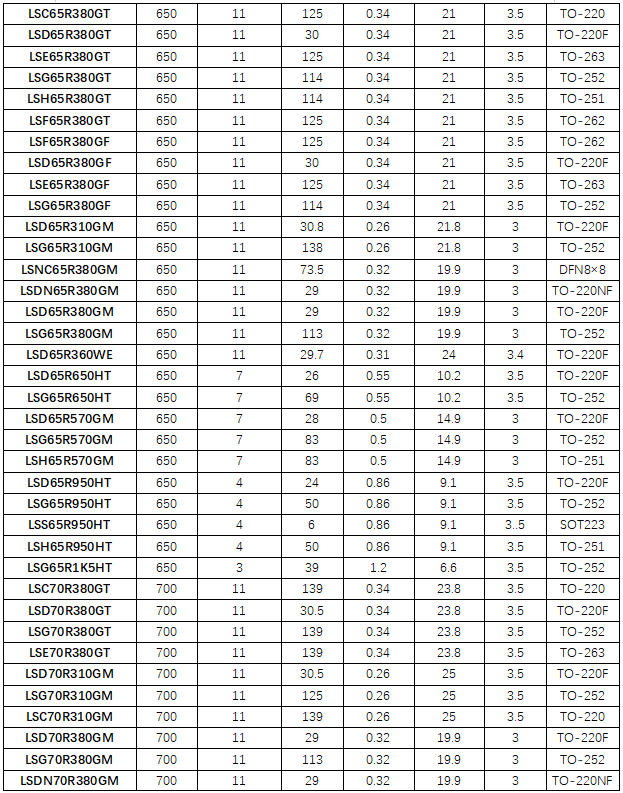

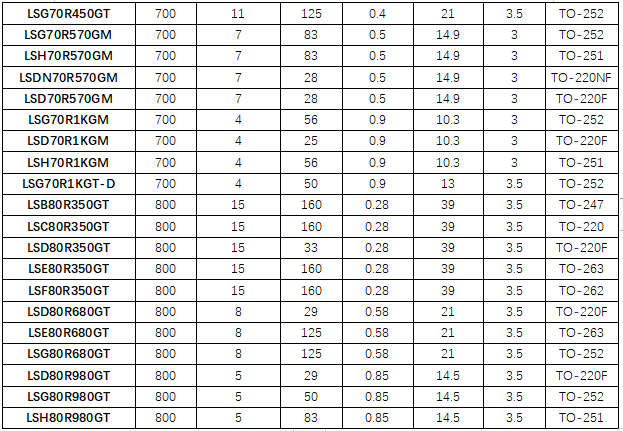

三、龙腾超结MOS主推产品列表

审核编辑:汤梓红

-

超结MOSFET的基本结构与工作原理2026-01-04 3045

-

vdmos和mos有什么区别2024-09-29 4248

-

平面型VDMOS和超结型VDMOS的雪崩耐量有何差异以及如何选择?2023-11-24 2689

-

超结理论应用:平面VDMOS结构与超结MOSFET技术介绍2023-09-18 8768

-

超结IGBT的结构特点及研究进展2023-08-08 1456

-

求一种减少VDMOS寄生电容的新结构?2021-04-07 2049

-

一种VLD结构VDMOS终端设计2017-01-07 902

-

一种900VJTE结构VDMOS终端设计2017-01-03 1079

-

VDMOS器件结构2011-12-01 4664

-

一种减少VDMOS寄生电容的新结构2009-11-25 1461

全部0条评论

快来发表一下你的评论吧 !