玩转单片机的重要功能-DMA,你的MCU编程设计有可能成为卷王!

电子说

描述

直接存储器访问(DMA)控制器,可以在内存和/或外设之间传输数据,而不需要CPU参与每次传输。合理利用DMA控制器,可以减轻CPU的负担。本文通过介绍DMA结构与工作原理,以及两种模式(兵乓模式与多数据包缓冲传输模式),来看看使用DMA如何提高MCU效率。

DMA结构与工作原理

先进的DMA控制器,如STMicroelectronics的STM32F4系列中包含的控制器,可以通过灵活的数据流分配和传输管理功能进一步减轻CPU的负担。

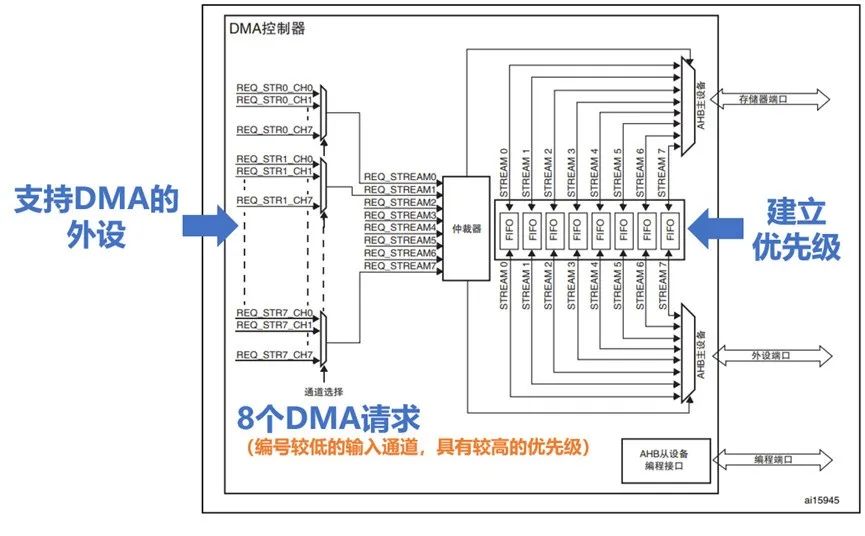

如图左侧所示,来自8个不同的通道DMA请求,并到仲裁器上,从而建立优先级(编号较低的输入通道,具有较高的优先级)。然后激活最高优先级的传输,传输到图中右侧的两个AHB 主设备(存储器端口和外设接口),提高了外设到存储器传输的效率。这可能是DMA在基于CPU的设计中最常见的情况。

图 1. STM32F4系列DMA控制器(图片来源于STMicroelectronics)

为每个路径分配单独的FIFO,如图1中间所示,允许针对每个外设接口的特性调整FIFO特性。例如,FIFO的阈值级别(请求传输的深度)可以单独设置为FIFO大小的¼,½或¾。这允许低速通道等待,直到FIFO几乎满了才进行传输,以最小化开销。更快的通道会更早地启动传输,可能只有一半大小,以避免FIFO溢出。

我们来通过一个实例,来看看DMA怎么工作的。

实例:“使用 STM32 来控制 NeoPixels LED”

硬件部分采用 STM32 开发板,与 NeoPixel LED、灯带、矩阵等相连接。

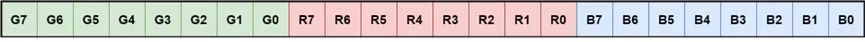

RGB NeoPixels实际上是WS2812智能控制LED。下面是WS2812 LED的3字节数据协议的结构,分别代表绿红蓝三个信息。

图 2. WS2812 LED的3字节数据协议的结构

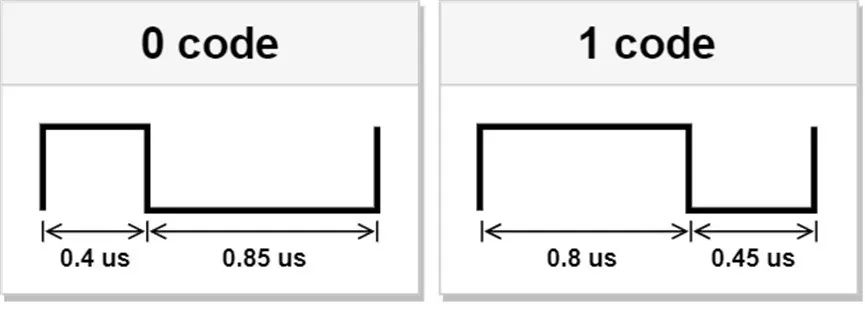

使用计时器来PWM控制波形,然后配置DMA使CPU高效并且易于实施。

图 3. WS2812 LED的0和1位的计时图

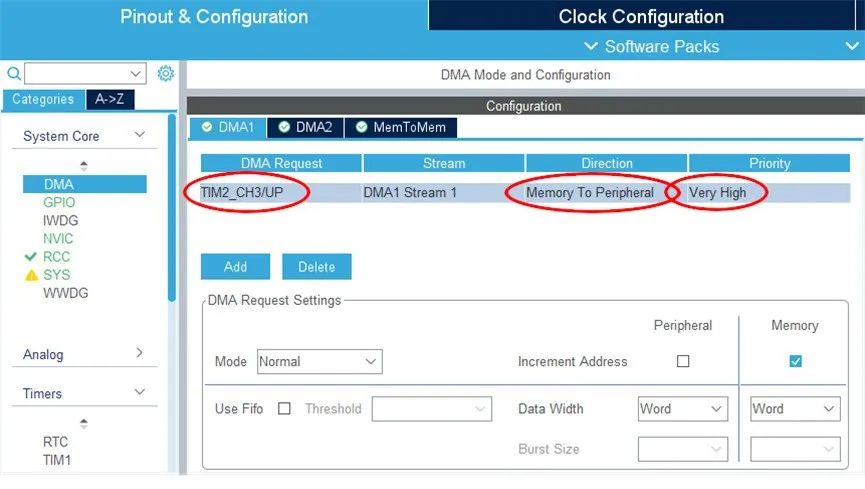

在软件中,配置DMA, 选择了“TIM2_CH3/UP”, 将方向改为“内存到外设”, 同时,将优先级改为“非常高”,最后保存.ioc 文件,以生成项目代码。

图 4. 配置DMA流,以便有效更新PWM信号的占空比

更多内容请看下面文章:使用 STM32 来控制 NeoPixels

DMA的两种模式

合理使用两种DMA模式(兵乓模式与多数据包缓冲传输模式),可以帮助提高MCU效率。

USB外设是一个很好的外设示例,早期的USB实现的最大吞吐量只有1.5 Mb/秒。随着更高性能的标准版本的出现。比如要接近12 Mbit/s全速USB标准的理论最大值。我们来看看,数据传输方面DMA如何帮助提高MCU效率!

我们以Microchip的ATXMEGA16D4-MH举例。

01、兵乓模式

之前通常使用单个存储器缓冲区进行外设数据传输。如果数据缓冲区已满,MCU将响应NAK(否定确认)消息。接收到NAK后,主机将等待并稍后重试传输。它将继续重试,直到MCU能够成功接收数据。

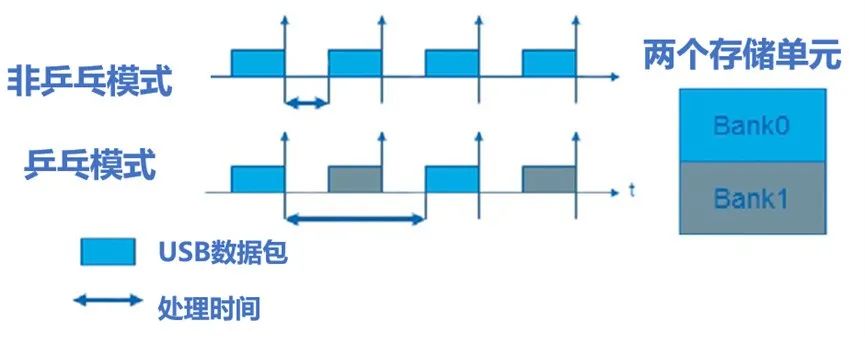

ATXMEGA16D4-MH使用乒乓模式来消除这个问题。乒乓模式使用两个存储单元(memory banks)进行数据传输。当一个存储单元满时,主机可以将数据传输到另一个存储单元。在两个存储单元之间交替传输可以避免复审,并提高整体数据带宽。

图 5. 乒乓模式提高了效率(图片来源于Microchip)

此外,如上图所示,以乒乓模式还使MCU有更多时间来处理数据。如图所示,没有乒乓,CPU只能处理传输之间的数据。使用乒乓模式,CPU可以在传输周期的一部分时间内处理数据,并降低NAK被要求“赶上”数据处理要求的可能性。

02、多数据包缓冲传输模式

另一个很有用的模式,可以让MCU的数据传输更高效。这个特性叫做“多数据包缓冲传输模式”。如果你要通过USB端口传送的数据包,超过了全速USB的BULK传输模式所允许的最大值(64字节),那么就可以用上这个模式。以前,你需要在主机上把数据包分成小块,然后在接收端把它们合并,这会增加中央处理器(CPU)的负担。不过现在,多数据包缓冲功能加入了USB设备,它会在数据包超过USB标准大小时自动帮你分割和合并数据。重要的是,这个模式还能减少中断的次数,因为只有在整个传输结束后才需要中断CPU。这意味着,CPU可以处理其他任务,或者进入休眠模式,直到整个传输完成并且准备好处理。

总结

合理利用DMA控制器,可以减轻减轻CPU的负担,事半功倍。结合“乒乓缓冲”和“多传输模式”,你可以把传输的带宽从基准BULK传输模式的5.6 Mb/s提升到8.7 Mbits/s,这是一个不小的提升。更重要的是,在使用这两个功能的情况下,CPU的负担从基准的46%降低到只有9%。这两个功能的结合,不仅在性能上有所改进,而且还能节省能源。

来源:得捷电子DigiKey(作者:Alan Yang)

审核编辑:汤梓红

-

笙泉科技:专注提供8051 MCU单片机2010-03-08 1704

-

【高手问答】第2期——阿东带你走进fpga的逻辑编程设计2014-07-07 20734

-

如何升华51单片机基础,成为一个出色的开发工程师。2014-10-09 24868

-

如何成为单片机编程高手2021-02-01 1366

-

云计算为什么能成为物联网的秘密武器?2021-06-18 2326

-

如何才能成为一名单片机高手?2021-07-01 1960

-

STC89C52_51单片机_例程5_长短按键_定时***_要怎样努力才能成为很厉害的人? 精选资料分享2021-07-20 1076

-

单片机多功能编程器有哪些主要功能2021-09-18 2382

-

如何才能成为一个硬件工程师?2021-11-11 2015

-

如何才能成为一名单片机工程师?2021-12-23 4114

-

单片机的ISP在线编程设计2009-03-29 2201

-

怎么由芯片的时序图写程序?_单片机对1602液晶时序图编程设计2018-01-06 11795

-

华大单片机HC32F460 系列MCU2021-11-18 1446

-

AVR单片机为何能成为8位机中的佼佼者?2023-10-29 1603

-

按照这样学习C语言,成为卷王不是梦!2024-07-06 1199

全部0条评论

快来发表一下你的评论吧 !