如何理解 RAMECC FAR 寄存器的值

电子说

描述

1.问题原因

某客户测试 STM32H753xi 板子上的 ECC 功能,用于监控 AXI-SRAM 区域,但不是很明白 RAMECC FAR 寄存器在 RM0433 中的描述, “Bits 31:0 FADD[31:0]: ECC error failing address”。

比如在 AXI-SRAM 中,如果客户示例显示的是 FAR = 0x2004,但是这个地址值 0x2004 并不在 AXI-SRAM 范围之内,客户该如何理解 FAR 寄存器?希望能够有详尽的描述,这个 FAR 寄存器的偏移地址是 Word 地址还是 Byte 地址或其他?我们先来看看相关参考手册中关于 RAMECC 的介绍去寻找答案。

2.RAMECC 控制单元

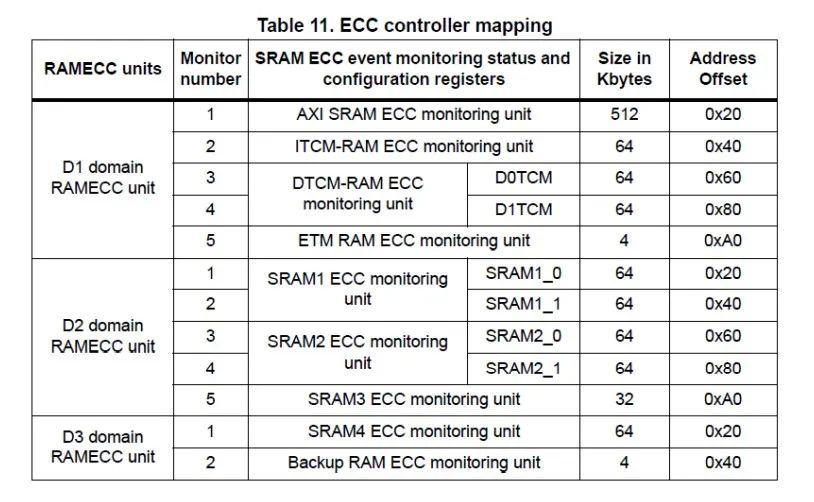

RAM ECC 控制单元的数量取决于不同的 STM32H7 系列。比如,对于STM32H74x/5x 和 STM32H72x/3x 它们的每一个域都有一个 RAMECC 的控制器单元,为了描述简单,表述如下:

Domain 1 (D1) RAMECC unit = RAMECC1Domain 2 (D2) RAMECC unit = RAMECC2Domain 3 (D3) RAMECC unit = RAMECC3

详细的说明请参考 RM0433 参考手册 rev7 中的截图:

3.RAMECC 寄存器地址

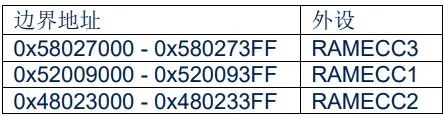

对于上图 Table 11 的 RAMECC 控制单元的地址总结成如下表格,具体的参考RM0433 的第二章节 Memory and bus architecture 中的 table 8.

4.RAMECC 寄存器

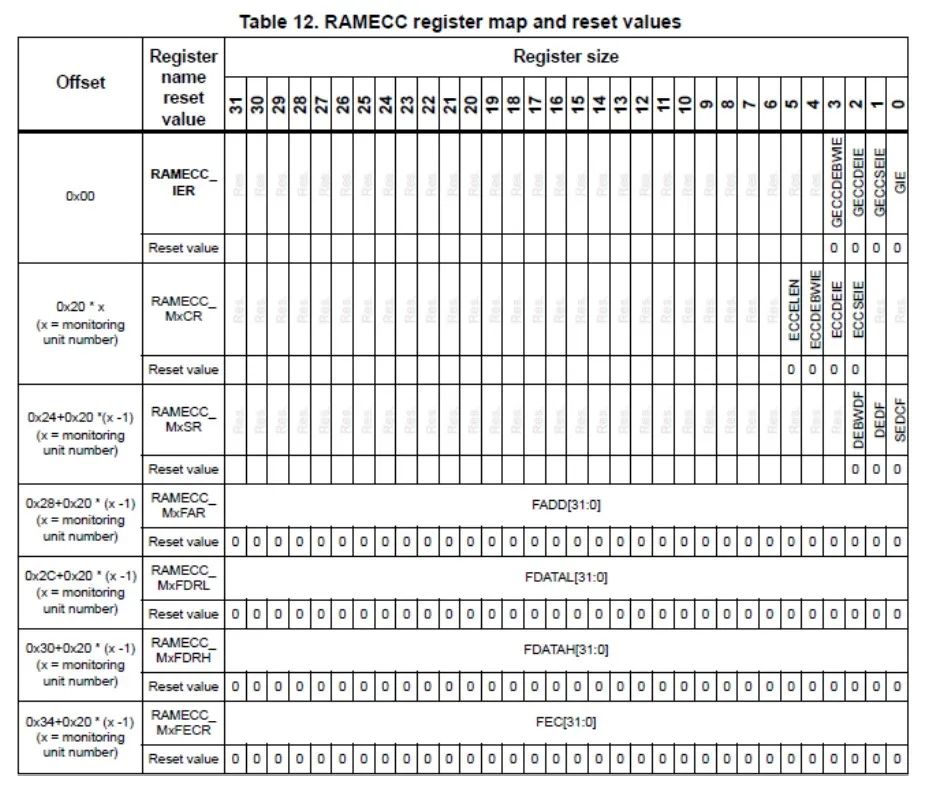

每一个 RAMECC 控制单元(RAMECC1、RAMECC2、RAMECC3)的监控单元Monitor number 均分别含有如下的一套寄存器组(其中 RAMECC_IER 为共同拥有)。

接下来我们以 RAMECC1 为例进行分析,其边界地址为:0x52009000 -0x520093FF,那么对于该 RAMECC1 控制单元中的寄存器组,对于每一个寄存器:

以 RAMECC1 的起始地址 0x52009000 为基准:RAMECC_IER:中断使能,偏移地址 0x00,该寄存器地址即为:0x52009000。

RAMECC_MxCR:配置寄存器,偏移地址 0x20 *x,x 为 ECC 监控单元号,该寄存器地址的表达式为:0x52009000 + 0x20 * x ,x 取值范围= [1..5](见上面表格 Table 11 ECC controller mapping),所以:

Monitor 1 - AXI SRAM ECC 监控单元,该寄存器地址即为 0x52009020,监控大小为整个 AXI SRAM 的 512KB 字节(0x24000000 -0x2407FFFF)。

Monitor 2 - ITCM-RAM ECC 监控单元,该寄存器地址0x52009040, 监控大小为整个ITCM RAM的64KB字节(0x00000000 -0x0000FFFF)。

Monitor 3、Monitor 4、Monitor 5 中该 RAMECC_MxCR 寄存器的地址,以此类推。

RAMECC_MxSR -- 状态寄存器,偏移地址: 0x24 + 0x20 * (x - 1),x 为 ECC monitor number 号码(见上面表格 Table 11 ECC controller mapping)。那么该寄存的地址为:0x52009000 + 0x24 + 0x20 * (x-1) ,x 取值范围 = [1..5]:

Monitor 1:0x52009024

Monitor 2:0x52009044

Monitor 3 : 0x52009064

Monitor 4 : 0x52009084

Monitor 5 : 0x520090a4

RAMECC_MxFAR --失败地址寄存器,表达式:0x52009000 + 0x28 + 0x20 * (x-1) , x取值 = [1..5]:

Monitor 1:0x52009028

Monitor 2:0x52009048

Monitor 3:0x52009068

Monitor 4:0x52009088

Monitor 5:0x520090a8

RAMECC_MxFDRL -- 失败数据低位,表达式 0x52009000 + 0x2c + 0x20 * (x-1) ,x 取值= [1..5]

Monitor 1:0x5200902c

Monitor 2:0x5200904c

Monitor 3:0x5200906c

Monitor 4:0x5200908c

Monitor 5:0x520090ac

RAMECC_MxFDRH -- 失败数据高位,表达式 0x52009000 + 0x30 + 0x20 * (x-1),x 取值= [1..5]

Monitor 1:0x52009030

Monitor 2:0x52009050

Monitor 3:0x52009070

Monitor 4:0x52009090

Monitor 5:0x520090b0

RAMECC_MxFECR --失败 ECC 错误代码,表达式 0x52009000 + 0x34 + 0x20 * (x1) ,x 取值 = [1..5]

Monitor 1:0x52009034

Monitor 2:0x52009054

Monitor 3:0x52009074

Monitor 4:0x52009094

Monitor 5:0x520090b4

5.解决问题

通过查询资料与试验,FADD[31:0]中表述的地址是 word 而不是 bit。为了计算真实的地址,客户需要用如下公式计算:真实地址= 所处内存的首地址 + FADD x 字节数。

现在举个例子,如上述提到的 FADD= 0x2004 :

- 对于 64-bit word 的内存 :如 AXI RAM : 0x2400 0000 + 0x2004 * 8 = 0x2401 0020;

- 对于 32-bit word 的内存 :如 SRAM1 : 0x3000 0000 + 0x2004 * 4=0x3000 8010 ;

来源: STM32单片机

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理

审核编辑 黄宇

-

LAT1170+如何理解 RAMECC FAR 寄存器的值2026-01-09 227

-

详解寄存器模型镜像值2024-10-23 2384

-

基于DWC2的USB驱动开发-发送相关的寄存器DMA寄存器详解2023-07-16 3472

-

RAL寄存器模型操作指南2023-07-12 2234

-

基于DUT内部寄存器值的镜像2023-06-24 1855

-

简化UVM寄存器模型的使用2023-05-29 2679

-

修改寄存器默认值的方法有哪些2023-01-30 3541

-

ARM通用寄存器及状态寄存器详解2023-01-06 9965

-

工程师笔记|如何理解 RAMECC FAR 寄存器的值2022-12-16 2398

-

修改寄存器默认值的方法2022-09-28 2468

-

教你们怎么去设定寄存器的初始值2021-04-01 8851

-

寄存器变量2019-06-03 2997

-

寄存器与移位寄存器2016-05-20 1295

-

寄存器,寄存器是什么意思2010-03-08 22412

全部0条评论

快来发表一下你的评论吧 !