使用SRAM来代指对SRAM和PSRAM芯片的支持

电子说

描述

MM32系列微控制器为用户提供了丰富的选择,可适用于工业控制、智能家电、建筑安防、医疗设备以及消费类电子产品等多方位嵌入式系统设计。在一些应用中,使用MM32F3270系列的片内SRAM还不够支持应用的需要,就要用外扩SRAM/PSRAM的方式来扩展。这时可以采用MM32F3270片内的FSMC接口来扩展SRAM/PSRAM。

因为SRAM和PSRAM的异步读写接口完全相同,只是时序方面需要根据不同的芯片所规定的参数不同而做相关的设置即可。本文接下来就使用SRAM来代指对SRAM和PSRAM芯片的支持。

前文已经介绍了MM32F3270的FMSC的接口功能与特色。结合MM32F3270 的FMSC外部接口信号,可使用异步方式访问SRAM,可以选用复用或非复用方式扩展SRAM,还可以通过配置实现外扩8位总线或16位总线接口的SRAM。

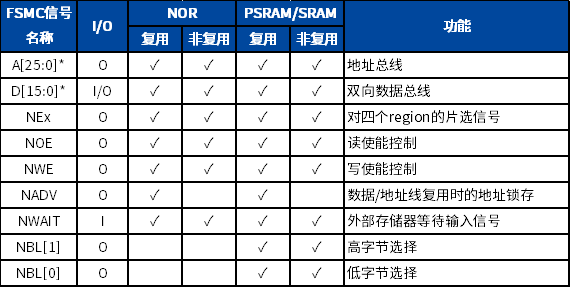

表1、FSMC控制器外部信号

表1、FSMC控制器外部信号

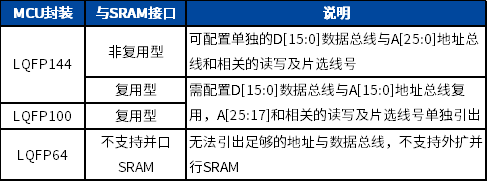

MM32F3270系列MCU因为封装的原因,导致只有部分MCU产品可以通过硬件复用出全部或部分的FSMC接口的相关GPIO,才能支持外接SRAM存储器扩展存储空间。其中LQFP144引脚封装MCU芯片支持连接地址数据非复用和复用方式外扩并行SRAM;而LQFP100引脚封装芯片因地址线缩减,仅支持连接地址数据复用方式外扩并行SRAM。LQFP64因为无法引出足够的地址与数据总线,不支持外扩并行SRAM。

表2、MM32F3270不同封装芯片与SRAM接口

表2、MM32F3270不同封装芯片与SRAM接口

目前市场上非复用型16位数据总线接口的SRAM/PSRAM较为普遍,下面就非复用方式,介绍MCU与SRAM的硬件原理图设计和软件寄存器配置。

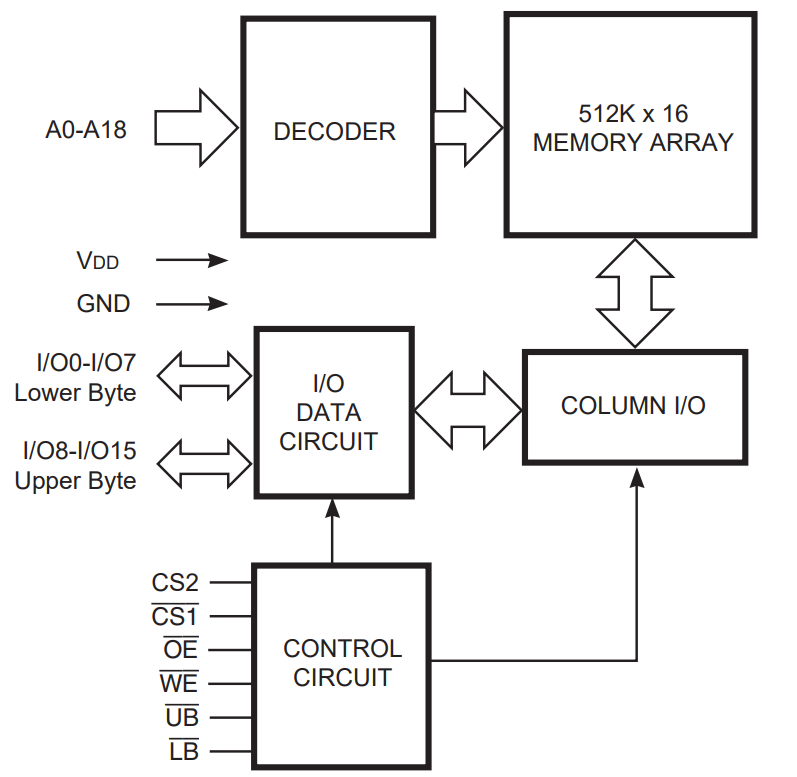

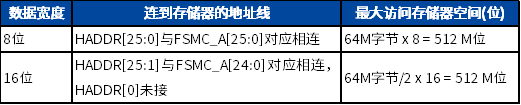

在此用MM32F3270扩展ISSI的SRAM :IS62WV51216,其原理框图如下:

图1、SRAM原理框图

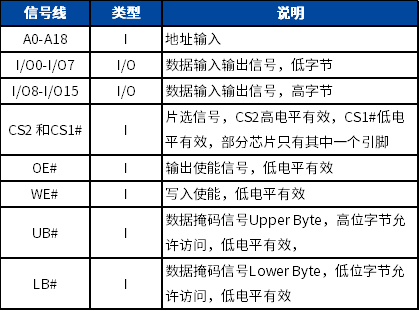

图1、SRAM原理框图 表3、SRAM引脚信号

表3、SRAM引脚信号

IS62WV51216的数据按 16 位的Half Word寻址,容量1M字节。IS62WV51216可以通过CS, OE, WR, UB, LB控制电路,结合Address与Data I/O实现数据的高速读写。

01、FSMC非复用方式控制SRAM的硬件设计

表4、SRAM信号对应的电源、复位与MCU接口的引脚说明

表4、SRAM信号对应的电源、复位与MCU接口的引脚说明

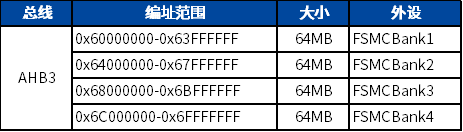

外部设备地址映像从FSMC的角度看,FMSC外扩寻址空间用于访问最多4个FSMC地址映射空间,可以用于访问4个NOR闪存或SRAM/PSRAM存储设备,并对应的有4个专用的片选FSMC_NE[4:1]。

外部存储器划分为固定大小为64M字节的四个存储块,见下图。

存储区块与片选信号对应关系:

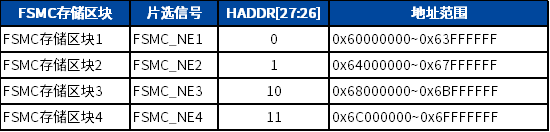

HADDR是需要转换到外部存储器的内部AHB地址线。HADDR[25:0]包含外部存储器地址。HADDR是字节地址,而存储器访问不都是按字节访问,因此接到存储器的地址线依存储器的数据宽度有所不同,如下表:

对于16位宽度的外部存储器,FSMC将在内部使用HADDR[25:1]产生外部存储器的地址FSMC_A[24:0]。不论外部存储器的宽度是多少(16位或8位),FSMC_A[0]始终应该连到外部存储器的地址线A[0]。

根据外部SRAM设计原理图:

02、FSMC非复用方式控制SRAM的硬件设计

根据配置的接口电路配置GPIO初始化程序与FSMC初始化程序。

void FSMC_SRAM_Init(void) { FSMC_InitTypeDef FSMC_InitStructure; FSMC_NORSRAM_Bank_InitTypeDef FSMC_BankInitStructure; FSMC_NORSRAM_BankStructInit( FSMC_BankInitStructure); FSMC_NORSRAMStructInit( FSMC_InitStructure); RCC_AHB3PeriphClockCmd(RCC_AHB3ENR_FSMC, ENABLE); FSMC_BankInitStructure.FSMC_SMReadPipe = 0; FSMC_BankInitStructure.FSMC_ReadyMode = 0; FSMC_BankInitStructure.FSMC_WritePeriod = 7; FSMC_BankInitStructure.FSMC_WriteHoldTime = 0; FSMC_BankInitStructure.FSMC_AddrSetTime = 1; FSMC_BankInitStructure.FSMC_ReadPeriod = 9; FSMC_BankInitStructure.FSMC_DataWidth = FSMC_DataWidth_16bits; FSMC_NORSRAM_Bank_Init( FSMC_BankInitStructure, FSMC_NORSRAM_BANK1); FSMC_InitStructure.FSMC_Mode = FSMC_Mode_NorFlash; FSMC_InitStructure.FSMC_TimingRegSelect = FSMC_TimingRegSelect_0; FSMC_InitStructure.FSMC_MemSize = FSMC_MemSize_64MB; FSMC_InitStructure.FSMC_MemType = FSMC_MemType_NorSRAM; FSMC_InitStructure.FSMC_AddrDataMode = FSMC_AddrDataDeMUX; FSMC_NORSRAMInit( FSMC_InitStructure); }

GPIO初始化

void SRAM_PIN_GPIO_Config(void) { GPIO_InitTypeDef GPIO_InitStructure; RCC_AHBPeriphClockCmd(RCC_AHBENR_GPIOB | RCC_AHBENR_GPIOC | RCC_AHBENR_GPIOA | RCC_AHBENR_GPIOD | RCC_AHBENR_GPIOE | RCC_AHBENR_GPIOF | RCC_AHBENR_GPIOG, ENABLE); RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE); GPIO_PinAFConfig(GPIOD, GPIO_PinSource0, GPIO_AF_12); //DA2 GPIO_PinAFConfig(GPIOD, GPIO_PinSource1, GPIO_AF_12); //DA3 // ……部分代码请参考样例程序 GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; GPIO_Init(GPIOB, GPIO_InitStructure); }

从选择的片选信号与FSMC外扩存储映像空间可以得出Bank1地址为0x64000000,使用该地址作为读写外部SRAM的基地址。

#define Bank1_SRAM3_ADDR ((uint32_t)(0x64000000)) //used NE2 PG9 p = (vu16*)Bank1_SRAM3_ADDR; for (i = 0x00; i < BUFFERLEN; i++) { *p++ = (u16)writebuffer[i]; } p = (vu16*)Bank1_SRAM3_ADDR; for (i = 0x00; i < BUFFERLEN; i++) { readbbuffer[i] = *p++; }

读写外部SRAM与读写片内SRAM是一样的操作,不同的是从不同的对应地址读写数据。通过上述代码可以观察到写入数据与读出的数据相同,表明配置准确,Demo实验成功。

审核编辑:彭菁

-

请问串口SRAM和并口SRAM的引脚区别?2020-06-17 7667

-

灵动微课堂 (第189讲) | 使用MM32F3270 FSMC驱动SRAM2021-11-10 2077

-

对SRAM时序进行分析2022-01-07 1452

-

AT32 支持的几种与SRAM/PSRAN/NOR FLASH界面简介2022-03-14 2270

-

PSRAM/SRAM与XMC硬件连接的推荐方法2023-10-24 508

-

新一代NV SRAM技术2008-11-26 1335

-

SRAM,SRAM原理是什么?2010-03-24 9270

-

sram作用2019-04-01 11739

-

PSRAM在数据缓冲应用中可以替代SRAM或SDRAM2021-01-20 2702

-

pSRAM与SRAM相比较,它的优势是什么2021-04-08 11142

-

如何采用MM32F3270单片机的FSMC接口来扩展SRAM2021-11-19 1171

-

32位MCU外扩SRAM芯片VTI7064MSME2021-12-07 1536

-

PSRAM融合SRAM与DRAM优势的存储解决方案2025-11-11 975

-

国产芯片伪SRAM存储器psram2026-03-03 128

-

PSRAM与DRAM/SRAM相比的优势是什么?2026-03-26 239

全部0条评论

快来发表一下你的评论吧 !