求一种不对称轻失配运算放大器的设计方案

电子说

描述

以应用于数模混合信号芯片中的运算放大器为对象,完成芯片设计验证的全流程,包括运算放大器的电路和版图设计、设计阶段的前仿和后仿验证、以及对PDK的验证全流程实验。

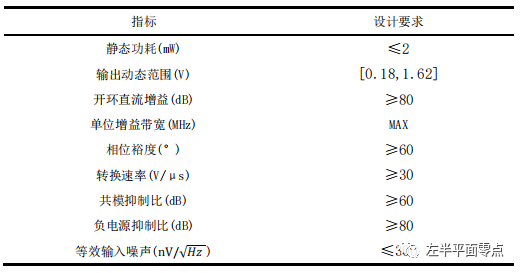

3.设计要求

①使用0.18μm工艺进行设计

②电源电压:1.8V±10%

③工作温度:25℃,0℃至50℃,-20℃至85℃,-40℃至+125℃

④详细指标要求:

4.作品特色

本作品在差分输入单端输出的共源共栅运算放大器基本架构的基础上,大胆尝试了一种新的设计架构,即故意失配的不对称结构。与常规的对称结构相比,节省了大约20%的版图面积以及10%的静态功耗。

5.作品介绍

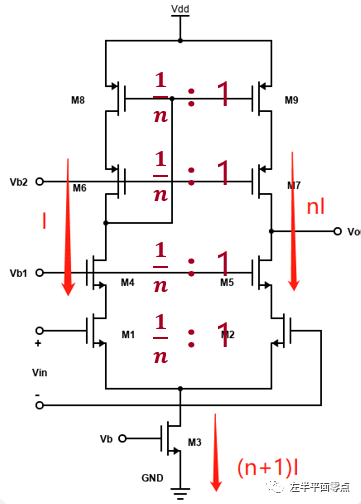

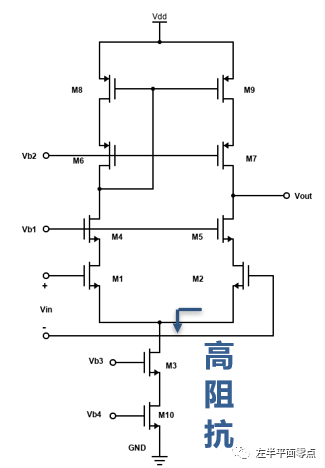

5.1 不对称结构

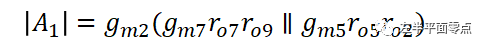

如上图,为运算放大器的主体部分结构。输出侧采用较大尺寸MOS,非输出侧采用较小尺寸的MOS,两侧尺寸之比n:1,形成故意失配结构,两侧电流之比也为n:1。增益由输出侧视入电阻、输入对管跨导确定:

此表达式与对称结构完全一致!同时节省了非输出侧的版图面积以及静态功耗,同时能实现对差分信号的处理。

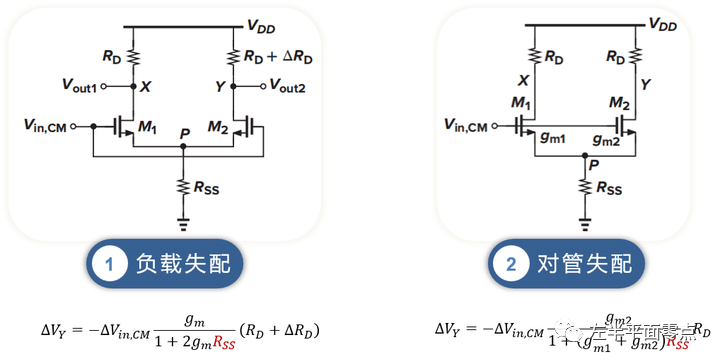

5.2 高等效视入电阻电流源解决共模抑制比的恶化

为了解决故意失配的不对称结构造成的共模抑制比恶化的问题,本团队改进了尾电流源,采用双管堆垛的电流源结构。尾电流源等效视入电阻增加gmro倍,从而同时优化了负载失配以及输入对管失配造成的从共模到输出结点的电压变化。

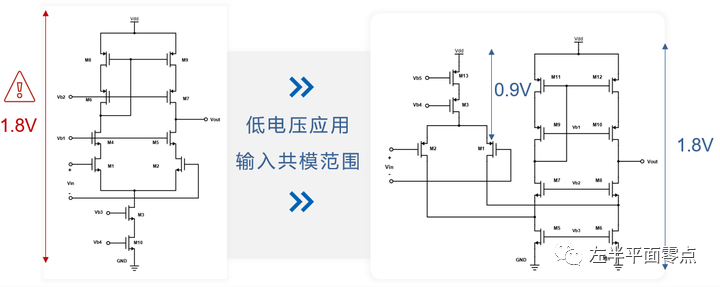

5.3 折叠式结构解决多管堆叠造成的偏置困难

由于采用了共源共栅架构以及上述的双管堆垛的高等效视入电阻尾电流源架构,运算放大器主体部分单条支路上多达6个晶体管,造成偏置困难、工作不稳定的问题。因此,必须采用折叠式输入设计,本团队对运算放大器主体部分做了下图改进。

5.4 Cascode补偿提高带宽

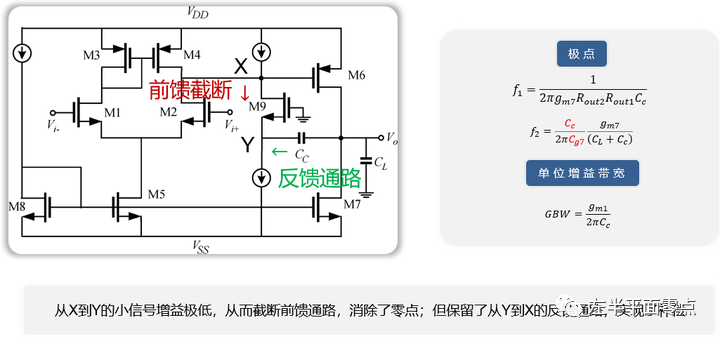

5.4.1 Cascode补偿介绍

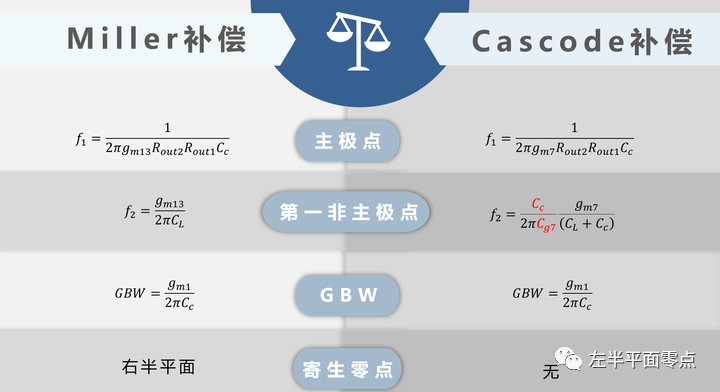

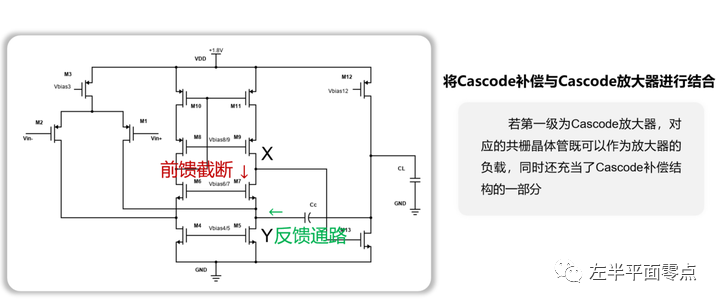

Cascode补偿基本结构如下图。与Miller补偿相比,M9截断了从结点X到结点Y的前馈通路,从而消除了零点。同时,与Miller补偿相比,次极点位置也移至更高频率,使得用更小的补偿电容,也具有相当的补偿效果,带宽从而得以提升。

5.4.2 Cascode补偿与共源共栅放大器的结合

若第一级为共源共栅放大器,Cascode补偿MOS管可以作以下结合:

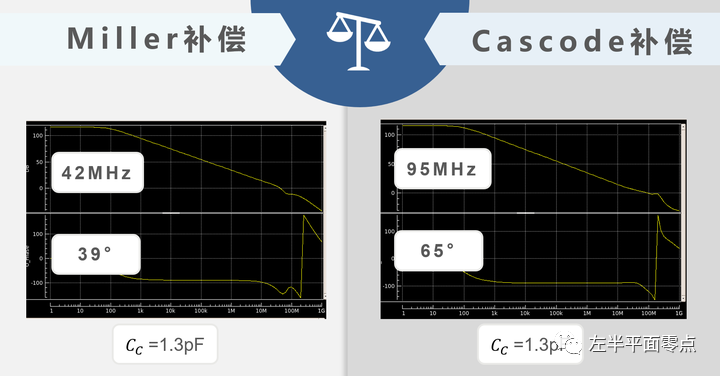

Miller补偿与Cascode补偿仿真对比如下:

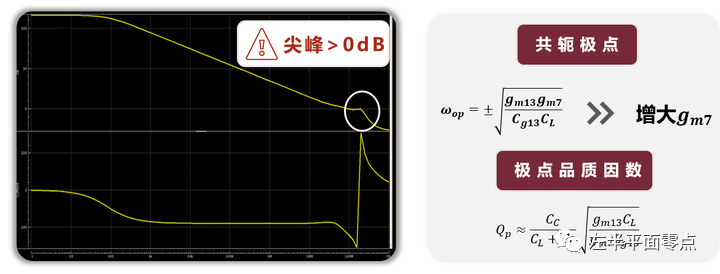

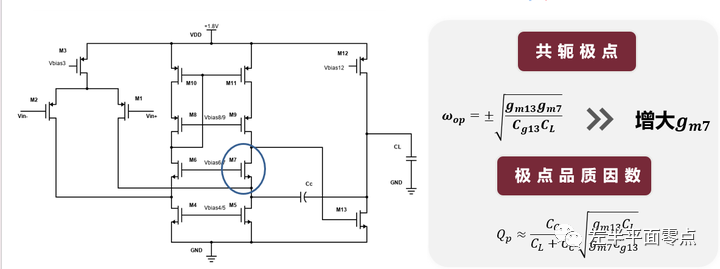

5.4.3 尖峰问题

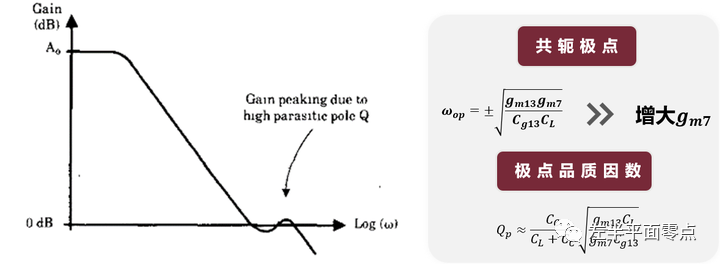

仿真结果显示,Cascode补偿在单位增益带宽外较近的位置产生了尖峰,主要原因是Cascode补偿MOS管M7等效视入电阻并不是无穷大。

由于共轭极点十分靠近单位增益频率,产生的尖峰对系统稳定性影响十分严重,因此需要减小共轭极点产生的尖峰,这需要减小共轭极点的品质因数

-

请问运算放大器的双电源电压不对称对运放的输出电压有影响吗?2018-10-22 3419

-

一款满足WCDMA基站性能要求的不对称Doberty功率放大器设计2019-07-03 2702

-

满足WCDMA基站性能要求的不对称Doberty功率放大器设计2019-07-04 2374

-

请问能将信号电源放大器与不对称电源一起使用吗?2021-04-09 944

-

求一种低压低功耗CMOS电流反馈运算放大器设计方案2021-04-25 1836

-

求一种陶瓷扬声器系统的放大器设计方案2021-06-04 2128

-

【2023集创赛】国家集创中心杯三等奖:不对称轻失配运算放大器2023-09-01 1517

-

采用不对称RC双T反馈电路的选频放大器分析与设计2010-08-29 1194

-

一种高性能运算放大器的设计2017-03-05 700

-

不对称Doherty功率放大器ADS仿真2017-11-23 1153

-

不对称Doherty功率放大器ADS仿真与工作原理2019-03-15 3644

-

基于ADS平台不对称Doherty功率放大器的仿真设计[图]2018-01-18 1042

-

如何使用ADS平台设计不对称的Doherty功率放大器2020-09-08 1462

-

如何使用ADS仿真不对称Doherty功率放大器2020-08-27 1368

-

DN43-LT1056改进型JFET运算放大器宏模型不对称开关2021-04-19 874

全部0条评论

快来发表一下你的评论吧 !