基于FPGA的USB3.0回环传输测试方案

描述

本文开源一个FPGA项目: USB3.0 LoopBack 。基于FPGA的USB3.0通信方案有很多,其中非常好用的一款USB3.0芯片是 FT600/601Q 。

下面介绍一下这款FT600/601Q芯片的技术参数,控制信号、数据读写时序等,并利用官方提供的上位机软件进行数据回环测试。

FT600/601Q芯片

芯片技术参数

- FT600&601Q芯片是FT最新推出的USB3.0 to FIFO interface IC,实现USB3.0与16/32bit并行IO接口之间的数据传输;

- USB通信协议全部由芯片驱动自行完成,开发者无须考虑USB底层固件的编程;

- 支持USB3.0(5Gbps),向下兼容USB2.0(480Mbps and 12Mbps)传输;

- 支持2种FIFO传输协议,最大传输可达400MB/s;

- 高达8个可配置Endpoint;

- 芯片内部有16K字节的缓冲区,可以进行数据的大吞吐量操作;

- 支持远程唤醒功能;

- 芯片支持多种IO电压:1.8V,2.5V,3.3V,

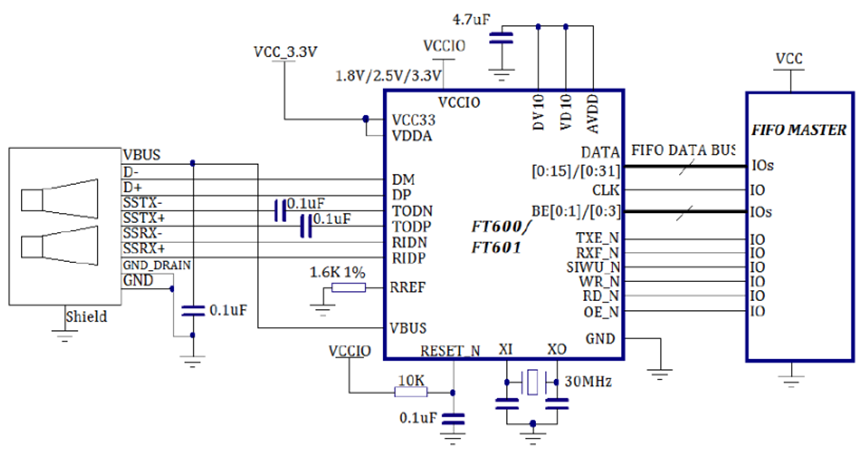

- 通过16bit或32bit并行数据线和读写状态、控制线RXF、TXE、RD、WR,加上时钟CLK,使能OE信号线就可实现与CPU、FPGA的数据传输;

- 工业级芯片,工作温度范围-40~85℃。

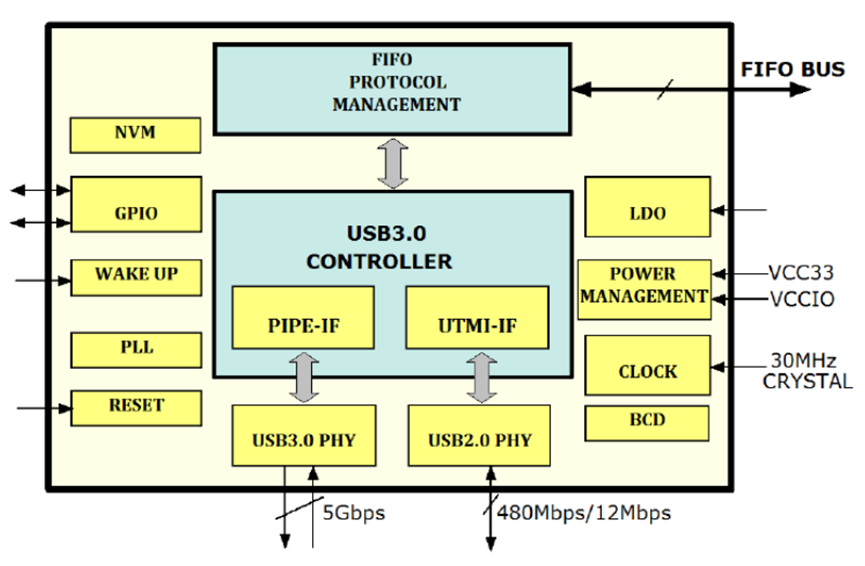

芯片内部架构

极简外围电路设计

读写模式&时序

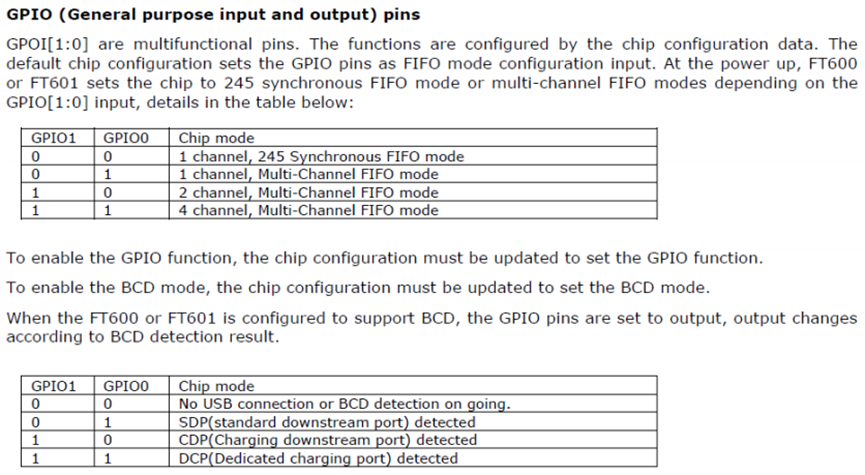

FT600/601Q常用读写模式为245 Synchronous FIFO模式和Multi Channel FIFO模式,本工程以芯片默认的245 Synchronous FIFO模式为例。

FT600/601Q读写模式是通过GPIO0和GPIO1进行配置,具体配置方法如下图所示:

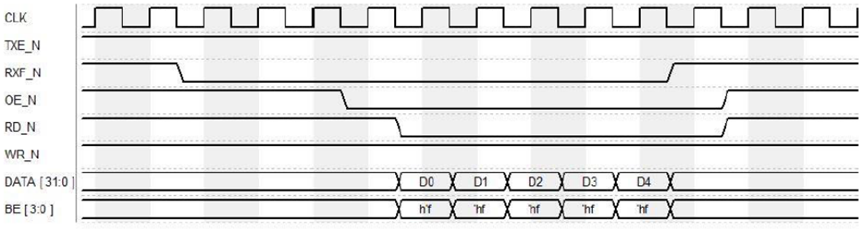

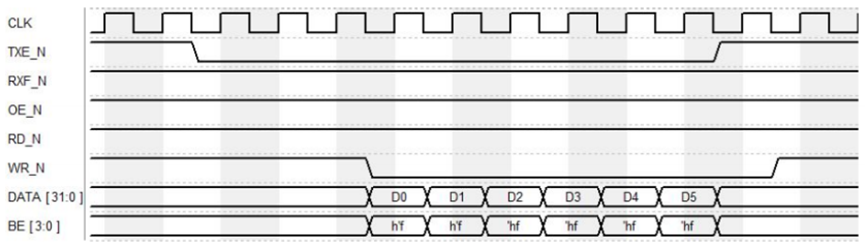

245 Synchronous FIFO模式读写时序也非常简单,当RXF_N信号拉低时, 通知FPGA开始读任务,当TXE_N信号拉低时,通知FPGA开始写任务:

- 245 Synchronous FIFO模式读时序

- 245 Synchronous FIFO模式写时序

回环传输测试

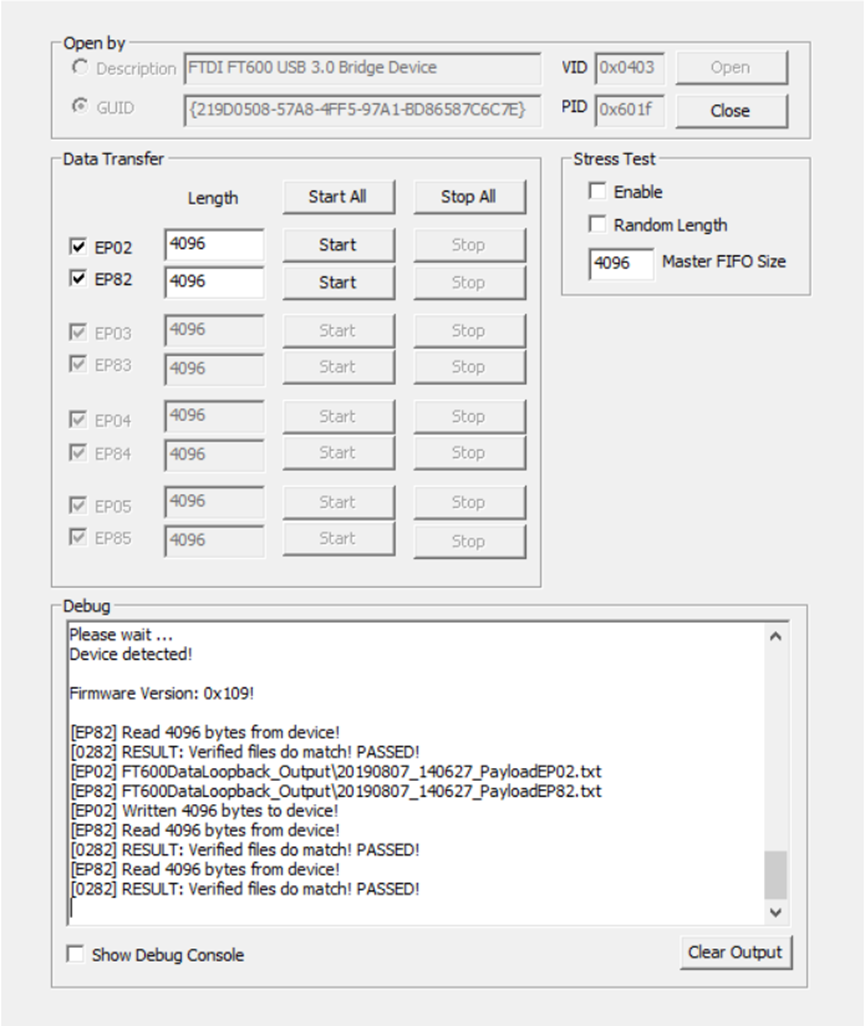

采用官方提供的FT600 Data Loopback Demo App上位机软件进行 数据回环测试 ,每次读写4096字节数据,结果如下图所示:

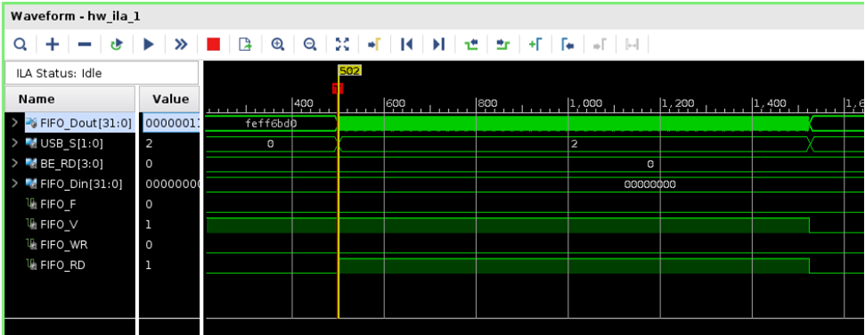

在Vivado工程中通过添加在线逻辑分析仪模块查看相关信号:

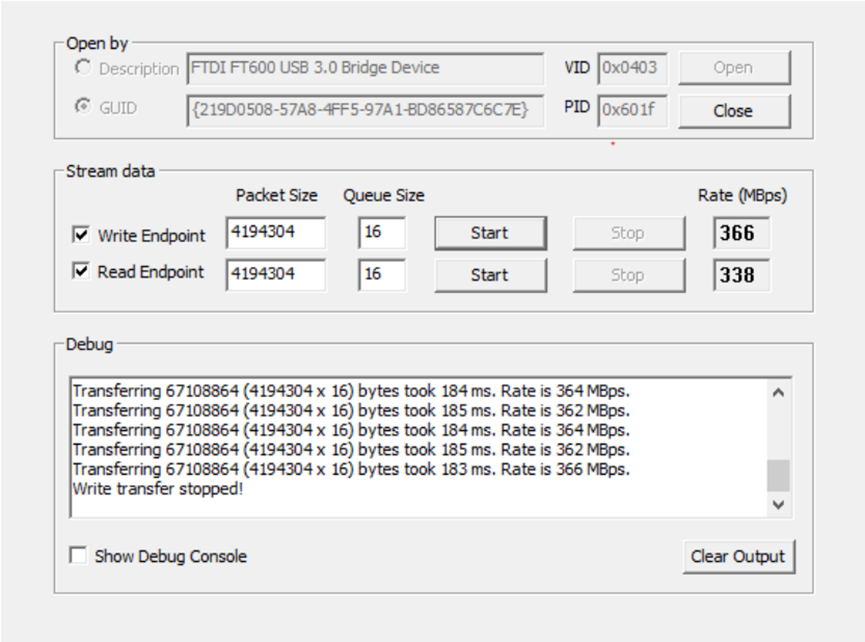

另外,还可以采用官方提供的FT600 Data Streamer Demo App上位机软件进行Stream数据流传输测试,速度可以达到360MB/S左右:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

使用CYUSB3014作为USB3.0数据传输方案,USB3.0无法识别是什么原因?2025-05-29 2081

-

什么是USB3.0?usb3.0与usb2.0有什么区别?2023-10-27 12612

-

FPGA和USB3.0通信-USB3.0 PHY介绍2021-12-20 2073

-

USB3.0接口的传输速率是多少?2021-11-23 12497

-

FPGA和USB3.0通信-USB3.0 PHY简介2021-11-09 10910

-

USB3.0物理层测试中的一致性模式和环回模式介绍2021-05-12 3839

-

关于迪赛康USB3.0的产品测试与设计结果2021-03-19 9889

-

USB 3.0高速传输模块XILINX版 USB3.0开发板 USB3.0模块2019-01-15 1102

-

USB 3.0高速传输模块XILINX版 USB3.0模块 USB3.0开发板2019-01-08 1956

-

USB 3.0高速传输模块XILINX版 USB开发板 USB3.0开发板2018-09-20 1919

-

基于FPGA+USB3.0接口的高速数据传输系统设计2018-08-09 15239

-

USB3.0接口的新电路保护方案2012-10-24 3288

-

USB3.0芯片速度测试比较2011-01-01 8317

-

USB3.0的物理层发送端测试方案2009-10-29 1488

全部0条评论

快来发表一下你的评论吧 !