AMBA总线概述

接口/总线/驱动

描述

01AMBA总线概述

AMBA(Advanced Micro-Controller Bus Architecture,高级微控制器总线架构)是由ARM公司开发的片上总线标准。主要包括APB(Advanced Peripheral Bus)、AHB(Advanced High-performance Bus)、AXI(Advanced eXtensible Interface)、ACE(AXI Coherency Extensions,AXI一致扩展总线)等。

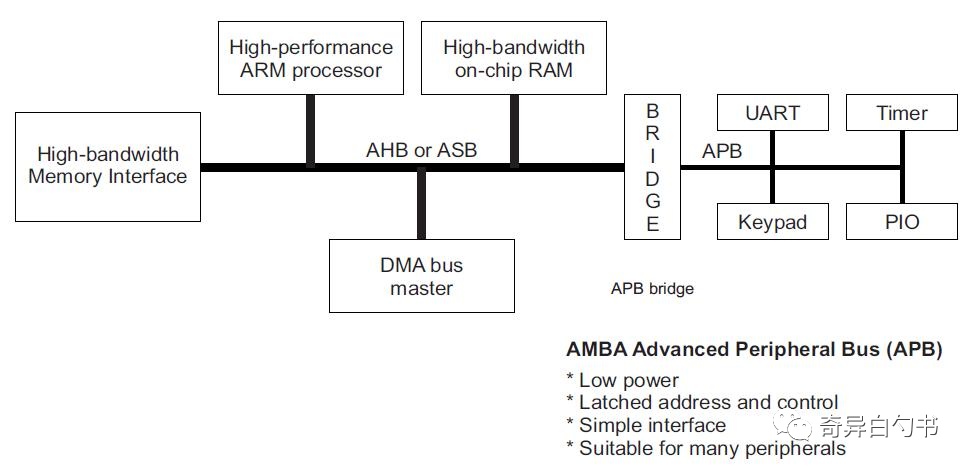

顾名思义,APB总线连接的是低速的外围设备,如UART接口、USB接口、键盘接口、时钟模块等。而AHB总线连接的是高性能的系统模块,如:处理器、DMA控制器、片内存储、外存接口等。二者之间通过AHB2APB Bridge连接。

典型的AHB-APB架构如图。

APB为了支持外围设备,在低功耗和低复杂性方面进行了特定的优化。读写操作共享同一组信号,不支持burst数据传输。它用作外围设备的低成本接口,不需要大量数据,低延时的传输,因此不需要高性能的流水线总线接口。APB总线的任何传输至少需要2个周期(Address Phase 和 Data Phase)。AHB支持仲裁(Arbiter)、突发传输(Burst)、分离传输(Split)、流水操作、多主从设备等复杂事务。主要是针对高性能、高时钟频率及快速系统模块所设计的总线,它充当高性能系统主干总线并支持高带宽操作。

(AHB-lite:是AHB的一个简化版本。简化后只支持一个Master,通过简化设计,提高了传输性能)

02全能选手-AXI

虽然AHB总线的协议在理论上可以让用户不断地增加总线位宽来提升传输带宽,但在节省功耗的前提下,用户希望通过极小的总线宽度、极低的总线频率来实现很高的数据吞吐量,也就是对协议传输效率追求极致。顺应这种趋势,ARM在2004年推出了AXI协议。

AXI协议是一种多通道传输总线,将地址、读数据、写数据、握手信号在不同的通道中发送,不同访问之间的顺序可以打乱(通过BUS_ID来表示每次访问的归属)。Master在没有得到返回数据的情况下可以发出多个读写操作。读回的数据顺序可以被打乱,同时还支持非对齐的数据访问。

由于各个传输之间仅依靠传输的ID来互相识别,因此没有时序上的依赖关系,因此也可以被插入寄存器片来打断限制频率的关键路径。

AXI不仅继承了AHB便于集成、便于实现和扩展的特点,还在设计上引入了指令乱序写入、结果乱序写回等重大改进,使得总线带宽得到最大程度的利用,可以进一步满足高性能系统的大数据量存取需求。

(AXI-lite是AXI的简化版本,简化后不支持突发数据传输。)

(AXI-stream协议是AXI协议的另一种风格,它只支持数据流从master 流到slave。与完整的AXI或AXI-lite不同,AXI-stream 协议中没有单独的读/写通道,因为其目的是只在一个方向上流。)

-

AMBA总线协议的基本原理和应用场景2024-08-05 4512

-

AMBA总线—apb简介2023-06-05 3902

-

AMBA总线知识之AHB(上)2023-05-04 3591

-

AMBA总线协议概述2023-04-12 2344

-

AMBA AHB总线与APB总线资料合集2022-04-07 5259

-

介绍AMBA2.0总线2021-09-06 4130

-

基于AMBA总线介绍2021-05-19 2922

-

ARM体系的特点与ARM的技术的简介及AMBA总线的分析2019-11-20 1466

-

AMBA总线概述(二)2018-10-02 1669

-

总线概述之AMBA总线2017-11-16 39612

-

AMBA AXI总线学习笔记2015-11-11 1329

-

AMBA_AXI总线详解2014-04-18 1861

-

AMBA总线IP核的设计2011-07-25 1322

-

基于AMBA片上总线的片上系统2010-09-01 2438

全部0条评论

快来发表一下你的评论吧 !