打通系统到后端,芯华章发布首款自研数字全流程等价性验证工具

描述

新品发布

GalaxEC

2023年9月18日,在首届IDAS设计自动化产业峰会(IntelligentDesign Automation Summit)上,面向数千名到场的EDA产业上下游企业及相关专业人士,业内领先的系统级验证EDA解决方案提供商芯华章,隆重发布首款自主研发的数字全流程等价性验证系统穹鹏GalaxEC。

随着GalaxEC的发布,芯华章自主EDA工具完成了对数字验证全流程的完整覆盖,进一步完善了自身丰富的系统级验证产品组合,可以为芯片设计及系统级用户提供更全面的敏捷验证服务。

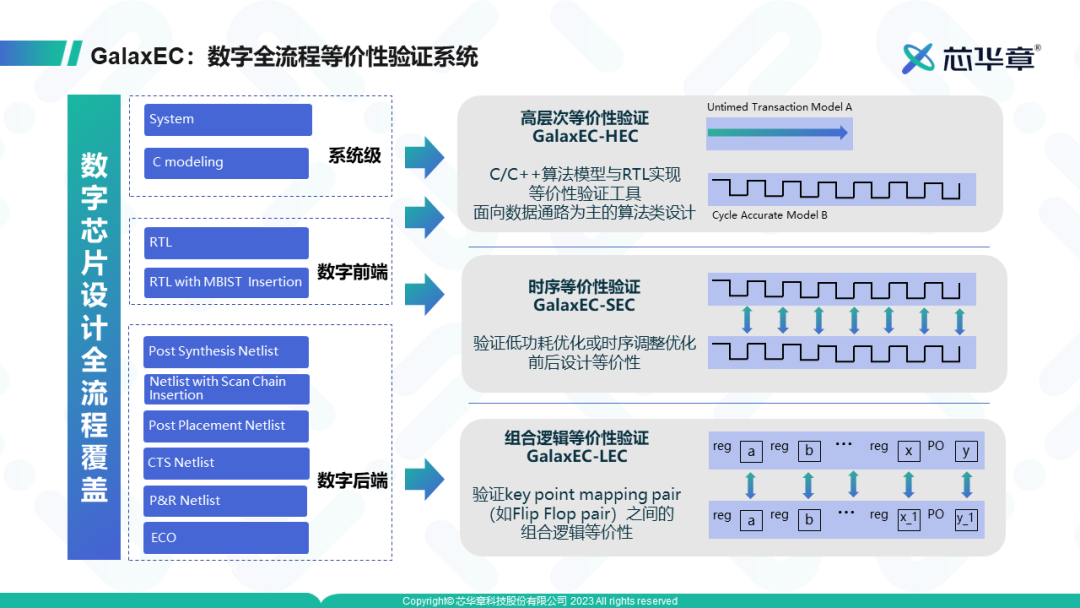

GalaxEC已具备当下各类主流等价性验证工具的所有核心功能,服务场景贯穿于数字芯片设计从系统级到前后端设计的各个阶段,可一站式满足用户全流程等价性验证需求,避免多工具切换成本,帮助工程师确保不同层次设计之间的一致性,支持遍历式验证,发现深层次的临界设计错误,确保设计的正确性并实现正式签核。

面向下一代EDA 2.0目标,GalaxEC运用新一代形式化求解算法和并行计算技术打造高性能求解引擎,可支持原生云部署,提供了丰富完备的用户开放接口,可以更好地满足敏捷验证与设计需要。

在完整的芯片设计流程中,等价性验证工具被广泛应用到设计流程中的各个不同阶段。

当一个设计经过变换之后,诸如系统C模型级对RTL级、RTL级对RTL级、RTL级对门级以及门级实现之间,工程师需要检验变换前后的功能一致性,证明设计的变换或优化没有产生功能的变化。

这在设计前端的时序优化,后端单元放置优化、网表级检查、ECO修改等中都是必不可少的环节。

CPU/GPU/AI等图像处理以及加密算法设计,往往以算法设计为中心并且数据通路繁重,经常使用C/C++等高级语言对它们的行为进行建模,这就需要保障RTL设计与高阶算法C/C++描述完全等价,确保功能正确

寄存器时序调整或插入用于功耗优化的门控时钟后,需要针对不同设计输出逐时钟周期(Cycle-by-Cycle)精确等价验证,如动态功耗优化(PowerOptimization)、门控时钟(Clock Gating)、时序调整(Retiming)等

关键节点(如Flip Flop pair)组合逻辑改动前后的等价性验证,保证在逻辑综合过程中没有改变原先HDL描述的电路功能,完备验证从RTL编码到最终LVS(Layout Versus Schematic)阶段设计的功能一致性

为了更好满足越来越多的大规模设计验证需求,GalaxEC支持大容量数据的快速处理,能够直接读入和验证SoC级大设计,自动化完成大规模验证建模,可实现对大容量SoC级的门级网表等价性验证。

基于对等价性验证系统原理的深刻理解,芯华章GalaxEC自主研发了高效形式验证求解引擎库XSolver,求解引擎采用新一代求解算法和并行计算技术,相对于传统形式验证求解引擎,在某GPU算子用例实验结果中,表现出百倍以上性能提升,帮助用户高效、敏捷地完成复杂系统级项目开发。

具体以Nyuzi GPGPU设计为例,GalaxEC仅仅用时9分钟就完成时钟树综合前后的网表等价性验证,60分钟内完成Placement布局前后的网表等价性验证,45分钟完成Routing布线前后的网表等价性验证。

作为国内领先的无线通信芯片方案提供商,矽昌通信长期专注产业空白的Wi-Fi AP芯片研发,发布了大陆首款无线路由芯片。

矽昌通信CEO王胜表示:

“无线通信芯片往往需要具备高度的可靠性、稳定性和极低的功耗,以确保在各种复杂部署条件下的正确运行。 芯华章GalaxEC提供的时序与组合逻辑等价性验证工具,基于自主研发的XSolver引擎库和多线程技术,可以高效、敏捷地验证数字设计全流程各阶段设计的等价性,特别是在综合与布线完成后,即使对设计做细微优化,也可直接快速验证优化前后设计等价性,避免了使用传统动态仿真工具对网表进行重复测试,保证了网表变更回归验证的完备性,帮助我们更快实现新产品的开发和上市。”

芯华章董事长兼CEO王礼宾表示:

“GalaxEC的发布,不仅是芯华章研发团队全情投入的成果,也离不开各领域产业用户的信赖和打磨。越来越多的大规模复杂IC设计需要专门的等价性验证工具来实现更快、更完备的验证收敛。

我们结合用户使用场景,打造了这款全流程等价性验证系统,可以一站式满足用户主要需求,无论是系统级还是前端或者后端,从而避免碎片化、兼容性带来的验证效率瓶颈和成本。

未来,我们将继续与业界伙伴保持深度合作,通过在数字验证全流程领域的持续创新,不断推出更符合用户定制化需求的敏捷验证方案,助力数字化创新效率提升。”

除了带来最新的产品研发成果,芯华章秉承开放、共赢的合作精神,深度参与本次IDAS峰会的各个环节,与国内外知名学者、高校专家、企业领袖同台论道,为促进EDA产学研生态深度融合建言献策。

本次IDAS峰会由EDA开放合作创新组织EDA²主办。作为EDA²验证专委相关分委会重要成员,芯华章一直保持同组织单位的密切交流,贡献了大量技术标准及解决方案,率先提交完整的调试系统波形接口标准文件,并参与形式验证指引格式FVG标准制定,为国产EDA早日建立统一的行业标准作出了重要贡献。

对本产品感兴趣的朋友们,也欢迎点击文末阅读原文链接,获取更多信息。

关于芯华章科技

芯华章科技成立于2020年3月,聚焦EDA数字验证领域,打造从芯片到系统的验证解决方案,以智能调试、智能编译、智能验证座舱、智能云原生为四大技术底座,已发布多款基于平台化、智能化、云化底层构架的系统级验证产品,可提供完整的全流程数字验证EDA工具,并已全面投入市场,交付多家头部用户使用。同时,芯华章致力于面向未来的EDA 2.0 智能化电子设计平台的研究与开发,以技术革新加速系统创新效率,让芯片设计更简单、更普惠。

关于矽昌通信

矽昌通信成立于2014年,专注于产业空白的Wi-Fi AP芯片研发。公司曾于2018年推出本土首款Wi-Fi AP芯片。历经8年艰苦研发,矽昌团队已积累出色的链路设计能力、关键IP自研能力、自有算法、软件、方案解决能力,拥有多颗大规模SoC设计开发量产经验。公司产品已广泛应用于头部网通产品厂商,出货量达数百万颗,是国内屈指可数的Wi-Fi AP芯片提供商。矽昌通信已于2019年获得高新技术企业认证,并于2022年成功通过ISO9001质量体系认证。关于EDA²

EDA²是在实现中国集成电路电子设计自动化长期竞争力的共同愿景下,由从事集成电路电子设计自动化的研究、设计、验证、测试、应用和服务的企事业单位、大学和科研院所、专业机构等单位自愿组成,专注于推动中国集成电路电子设计自动化产业发展的合作机制。

- 相关推荐

- 热点推荐

- 芯华章

-

芯华章发布FPGA验证系统新品HuaProP32024-12-13 1435

-

珠海南方集成电路设计服务中心引进芯华章全流程验证工具2024-03-13 1501

-

打通系统到后端,芯华章发布首款自研数字全流程等价性验证工具2023-09-19 713

-

赋能数字设计全流程 芯华章敏捷验证工具亮相IDAS2023-08-29 1755

-

补齐重要版图,国产EDA厂商实现全流程数字芯片前端验证!芯华章发布硬件仿真器,EDA2.0战略更进一步2023-06-26 3574

-

芯华章发布国内首台超百亿门大容量硬件仿真系统 完备数字验证全流程工具平台2023-06-16 979

-

首场爆满!芯华章验证技术研讨会都讲了什么?2022-10-20 754

-

芯华章发布数字验证调试系统—昭晓Fusion Debug™2022-05-30 2964

-

芯华章推出数字验证调试系统昭晓Fusion DebugTM2022-05-11 1640

-

芯华章发布智V验证平台有效地解决产业正面临的兼容性挑战2021-12-31 5008

-

芯华章推出四款验证EDA工具获业界高度认可2021-12-22 3415

-

数字IC后端设计介绍,写给哪些想转IC后端的人!2020-12-29 4387

全部0条评论

快来发表一下你的评论吧 !