混频相位噪声的恶化问题解析

描述

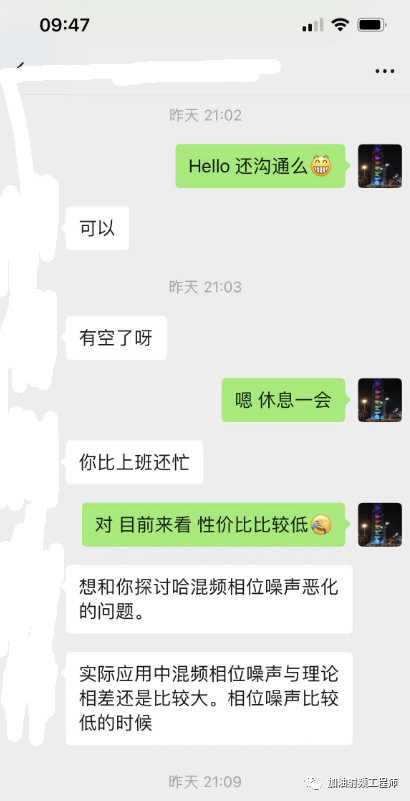

号友发过来想要沟通的内容,“实际应用中混频相位噪声与理论相差还是比较大。相位噪声比较低的时候。”

我当时看到这的时候,其实我心里是这样想的,实测和理论差2dB还好吧,一般这种差别,都能被留的裕量给覆盖掉。

一般性能的PLL,谁会没有这2dB的裕量啊!

但是,号友做的产品不是一般的产品,对相噪要求太高了。图上的指标,都是在10KHz左右的相噪。而且,因为产品本身相噪指标要求高,再结合器件本身能达到的性能指标,能给的裕量基本就没有了。

要是器件能到个-174dBm/Hz,估计也不会去扣这个细节。

不过,用号友的话说,现在射频也是越来越卷了,无论使用场景上用不用的到这么高的性能,反正指标一定要往高里提,然后价格还要保持不变。

所以,即使器件能到-174dBm/Hz,甲方提的指标,估计也嗖的一下,跟上来了。

言归正传,我总结一下号友的问题:

他有两个源,都是内部晶振源倍频分频产生的信号,分别作为混频器的输入和本振。

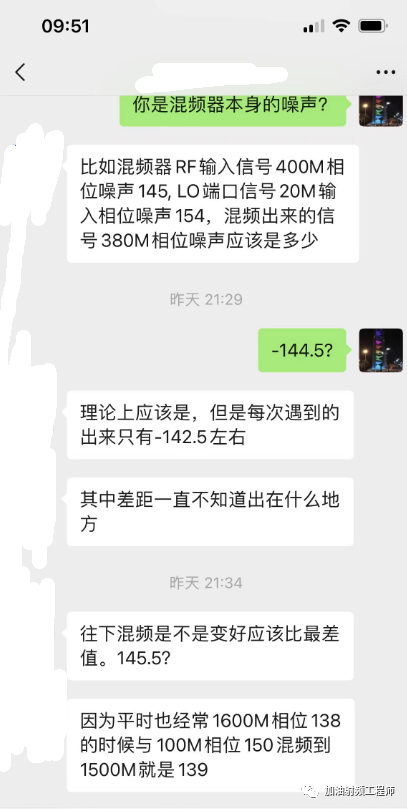

疑惑一:假设RF=400MHz,-145dBc/Hz@10KHz;fLO=20MHz,-154dBc/Hz@10KHz;当fIF=fRF-fLO=380MHz时,混频出来的相噪是-142.5dBc/Hz@10KHz。

疑惑二:假设fRF=1600MHz,-138dBc/Hz@10KHz; fLO=100MHz,-150dBc/Hz@10KHz;当fIF=fRF-fLO=1500MHz时,混频出来的相噪是是-139dBc/Hz@10KHz;当fIF=fRF+fLO=1700MHz时,混频出来的相噪是-137dBc/Hz@10KHz。

也就是说,这两个疑问包含两个问题,一个是,理论值和实测值,差了1~2dB;一个是,这个实测值,在理论值上下波动,一会好一会坏。

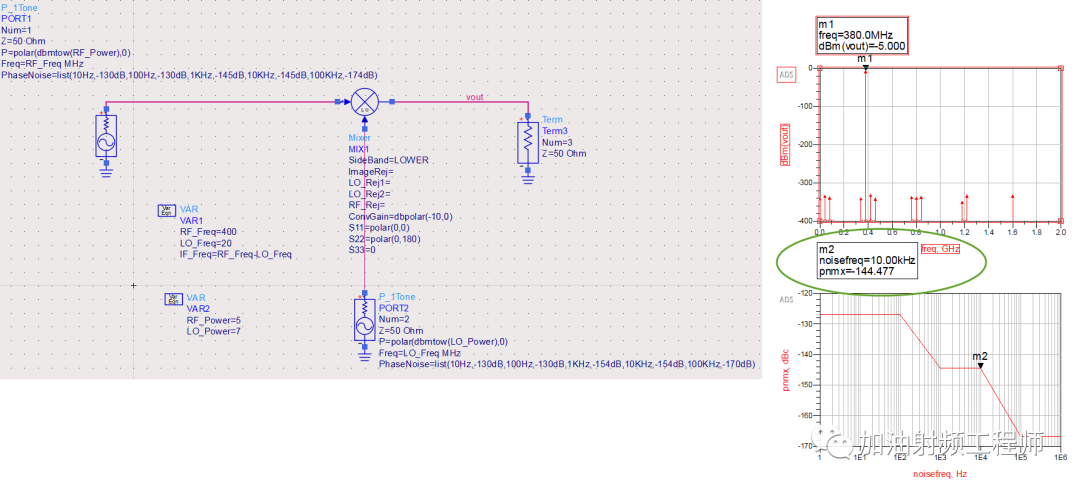

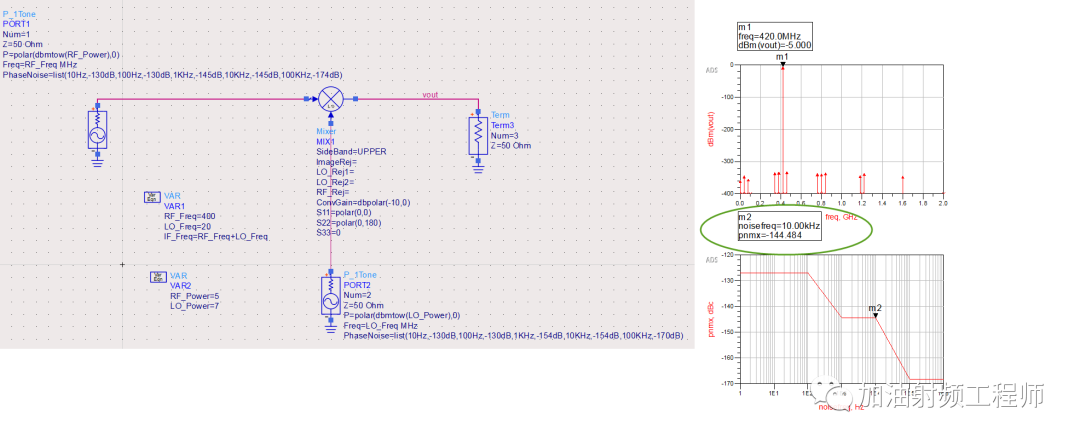

我用两个余弦函数分别代表RF信号和对应相噪,用另外的两个余弦函数分别代表LO信号和对应相噪,对疑惑一中的情况,算出来的理论值约为-144.5dBc/Hz。

然后又用ADS仿真了一下,结果如下图所示,不管是上变频还是下变频,仿真值,都是在-144.47dBc/Hz左右。

我俩也讨论,是不是闪烁噪声引起的,会不会和同源有啥关系?

所以,看到推送的你们,有没有什么高见呢?

审核编辑:刘清

-

相位噪声恶化2011-08-11 7700

-

混频器相位测量2016-12-22 6488

-

相位噪声2017-10-09 3729

-

频谱分析仪的相位噪声2017-10-16 5449

-

利用谐波混频的微波低相噪锁相设计介绍2019-06-20 1810

-

相位噪声恶化怎么计算2023-03-23 2934

-

相位噪声测量技术2010-10-08 794

-

利用相位噪声发生器辅助系统测试2008-08-19 1088

-

镜频抑制混频器通过ADS相位优化分析2017-11-07 1305

-

改进的DAC相位噪声测量2018-03-07 1010

-

关于脉冲调制信号相位噪声的测试方法的分析和应用2019-10-14 9171

-

如何才能准确测的试相位噪声2020-11-17 1036

-

相位噪声定义 相位噪声来源 相位噪声对信号的影响2024-01-29 2591

-

什么是相位噪声 产生相位噪声的原因 相位噪声的表示方法及影响2024-01-31 5408

-

如何快速准确地测量相位噪声2024-07-03 2650

全部0条评论

快来发表一下你的评论吧 !