FPC高速信号的应用实例解析

PCB设计

描述

FPC简介

柔性线路板(FPC)以其重量轻、配线密度高、厚度薄、易弯折等特点,被广泛应用于电子产品中。

FPC表面有一层树酯薄膜,起到线路保护和阻焊等作用,是FPC 产品的重要组成部分。

因其主要成分为聚酰亚氨(Polyimide,PI),故在该领域又被称之为 PI 覆盖膜,它是一种分子主链上含有酰亚胺环状结构的耐高温聚合物,在高温下具有突出的介电性能、机械性能、耐辐射性能和耐磨性能等,被广泛应用于航空、电子、电器等精密电子领域。

根据需求的不同,柔性电路板使用的板材也不一样。可以从应用的场合及成本等方面加以综合考虑。基材Substrate 在材料上区分为PI (Polymide ) (聚酰亚胺) 及PET (Polyester) (聚酯)两种,PI价格较高但其耐燃性较佳,PET价格较低但不耐热。因此若有焊接需求时大部分均选用PI。

聚酰亚胺(简称PI)是柔性电路加工中最常用的热固化绝缘材料。材料的厚度范围一般是12.5μm(0.5mil) 和125μm(5mil) 。分为有胶和无胶,有胶的介电常数是3.5(大概),无胶的介电常数是3.3(大概)。部分厂家可以提供7 mil厚度的,常用的规格是25μm(1mil) 和12.5μm(0.5mil) 。

Polyester 是由polyethylene terephthalate(简写PET,聚对苯二甲酸乙二醇酯)来制成的。它应用于柔性板的厚度范围一般是25μm(1mil)~125μm(5mil)。它和Polyimide 一样具有极好的柔软性和电气性能。它的介电常数是3.4(大概)。

覆盖膜由基材+胶组合而成,如上面所说,其基材亦区分为PI 与PET 两种。视铜箔基材之材质选用搭配之覆盖膜,覆盖膜之胶亦与铜箔基材之胶相同,厚度则由0.5~1.4mil。

胶Adhesive 一般有Acrylic 胶及Expoxy 胶两种,最常使用Expoxy 胶厚度上由0.4~1mil 均有,一般使用1mil 胶厚。

以下通过一个实例说明。

叠层设计

按照刚性区4层板,柔性区2层设计。

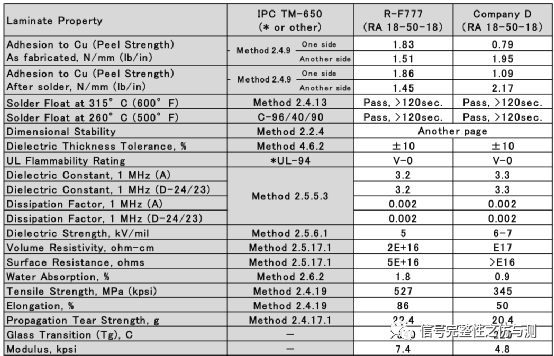

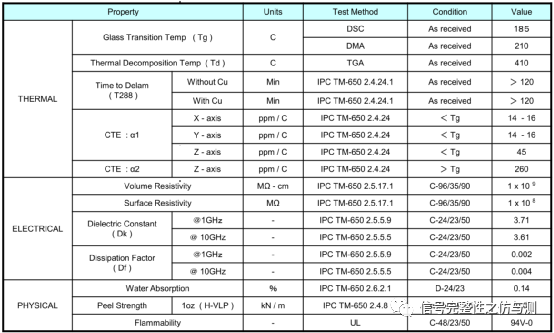

查看PI材料的规格书,只有1MHz的DK、Df数值,没有10GHz数值。不过DK、Df值都很低,参考M6板材1GHz与10GHz时的差异,预计这款材料高频下损耗也不会太大。

阻抗计算

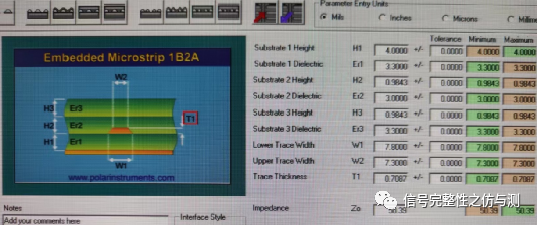

通常PCB板厂计算阻抗都是使用Polar SI9000,那么柔性板除一面正常GND参考,还有一面是有两层覆盖膜的,如何计算阻抗呢?不清楚的可以咨询一下对应板厂。依然是Polar软件,只是不同板厂计算方式不同罢了。比如A厂,计算时会先忽略了覆盖膜,然后根据工厂经验统一减去一个固定数值。就是使用正常的1B模型,单端减去4欧,差分减去10欧。我代入试算了一下,的确很吻合。这里我想说的是,如果你事先不了解板厂的计算方式,或者你事先不清楚要投哪家板厂,总得自己要去评估一下设计阻抗吧,要不然怎么仿真?所以介绍另一个模型1B2A,用这个模型计算也可以。

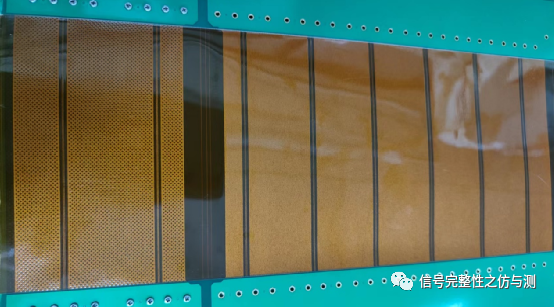

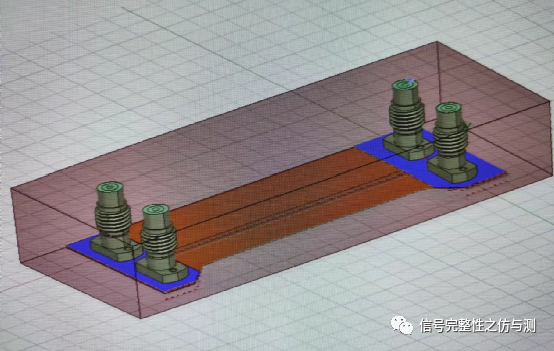

测试板设计

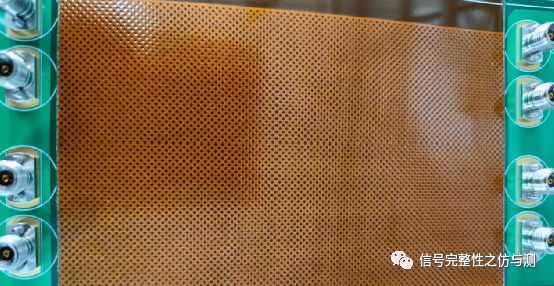

没什么好说的,就是正常lay上你想走的线,单端50的,差分85的、95的、100的等等,加工……就是加工周期有点长,比普通板要多个十天八天的。一定要评估好项目周期,柔性版最好先投。话不多说,上图。

测试板测试

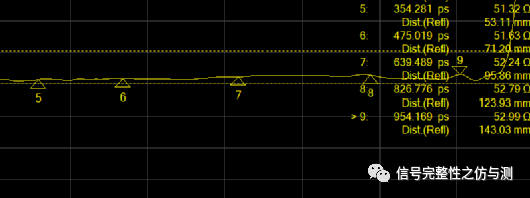

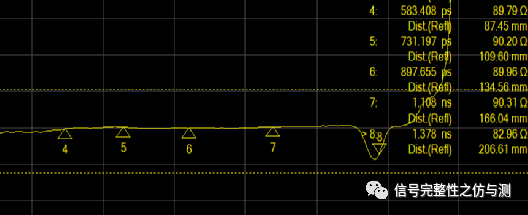

1.阻抗 单端50和差分85。差分部分柔性阻抗偏高了5欧,刚性部分又偏低了3欧。这种刚柔板结合对板厂阻抗控制能力要求较高。

顺便提一下网格铜设计,由于参考平面不完整,阻抗会偏高更多,设计的时候需要注意阻抗控制。再就是跟板厂确认计算模型,很有可能板厂计算时是不会考虑网格铜的。

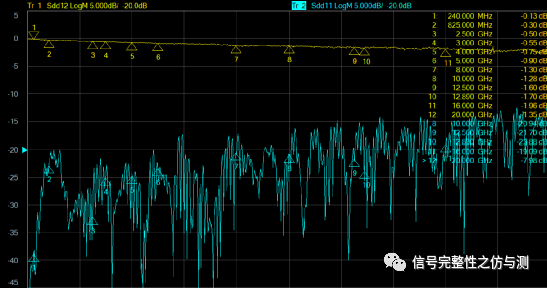

2.损耗 采用AFR去嵌,最终得到刚柔板中间2inch长度纯柔性部分的损耗。

换算成dB/inch自行除以2即可,有没有发现,跟M6板材损耗差不多吧。

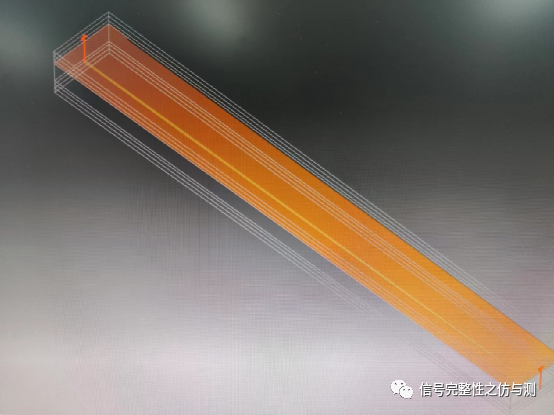

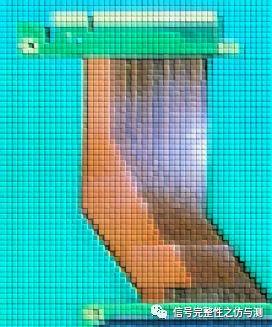

FPC仿真

大家都知道仿真非常重要的一步就是设置叠层,那么DK、Df值怎么填?

这还不简单吗,比如找板厂要M6材料的参数,@10GHz DK 3.61,Df 0.004,填上不就行了吗?

还真不是!导体损耗、介质损耗、铜箔粗糙度、趋肤效应,看似很多东西要考虑。填原始数据,那么忽略的东西太多,结果必然不准,比实际情况要理想很多。很有可能你仿真有很大余量,实际加工出来就gg了。那么,又有人问了,仿真时候铜箔粗糙度怎么设?不知道你仿真对象是有多高速,也不知道是不是搞学术研究,这里不做研究。只想说25Gbps以下的速率,就别折腾了。

单说做项目,不就是一个目的吗?

仿真跟实测能对得起来不就行了么。嗨……

怎么让仿真跟实测对得起来,这就是仿测拟合,拟合出等效介质常数和介质损耗值。这样不管你仿真哪条Trace,必然都跟测试结果是一致的。结果都一致了,谁还有空去纠结铜箔粗糙度这玩意儿。

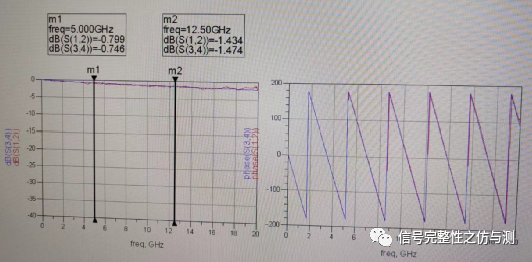

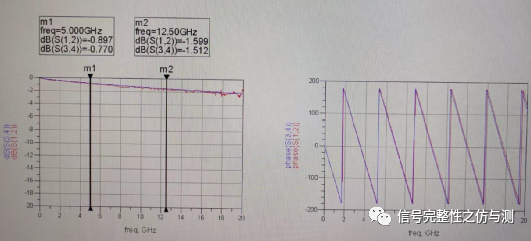

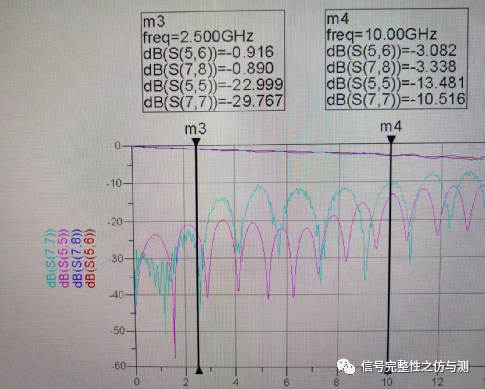

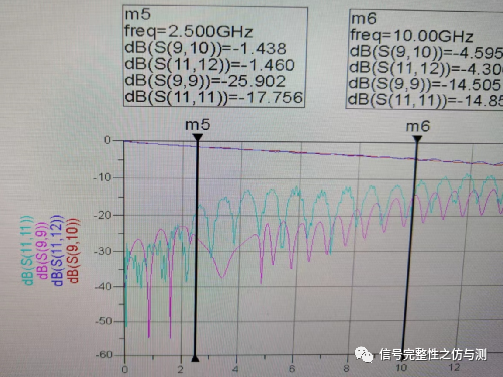

用同一套参数分别拟合了单端和差分,跟测试结果对比,无论损耗还是相位都一致。

单端

差分

得到的Df值是0.009,而手册给的值是0.004,两倍还多。如果按照原始数据仿真,那结果是不是太理想了,很有可能仿真结果就是一个错误的导向,失去了仿真的价值。

仿真验证

这就完了吗?No,按照工程师的严谨态度,只有正向逆向都经得起考验,才算bug被彻底消除,要不然那些调试阶段看似问题已经解了,一量产就呼呼出问题的案例就不会层出不穷了。所以要得出一条结论,必须是要经得起反复推敲的。我们把拟合数据再代回设计数据中。

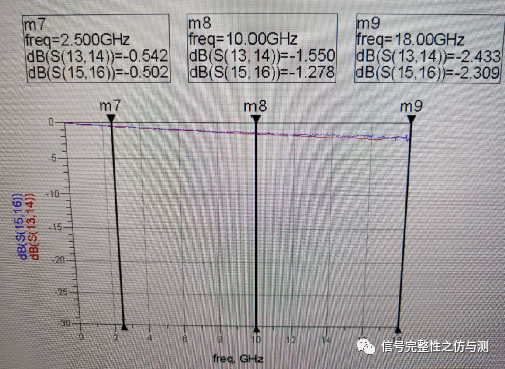

THRU线仿真与测试对比

DUT线仿真与测试对比

将仿真得到的两个S参数再进行去嵌,与测试板测试去嵌的结果进行二次对比,

各个频段均能吻合。

至此,从测试→去嵌→拟合→仿真→去嵌→拟合,整个链路闭环。拟合的参数准确有效,往后只要是此种材料的项目,仿真的结果就是测试的结果,这才是仿真的意义!

FPC应用

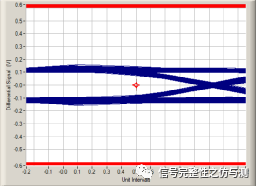

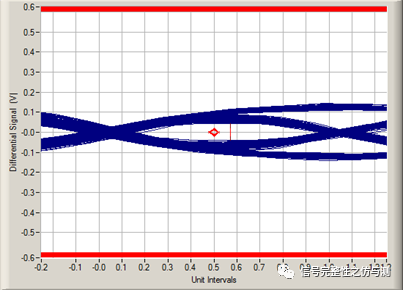

从以上仿真与测试结果可以看到,FPC用对了材料,本身损耗是没有问题的,跟M6差不多等级。别说10Gbps信号,25Gbps的信号也不在话下。前提是选好连接器,设计好刚柔结合处的阻抗,以及管控好板厂加工阻抗。举一个栗子,一款PCIe3.0的转接板。柔性区域线长约6-7INCH。

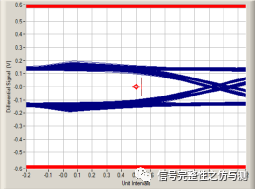

主板原始信号波形

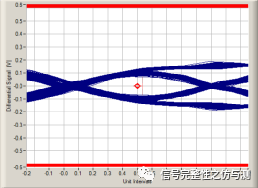

接上PCIe转接卡后波形

符合预期,使用正常。

编辑:黄飞

-

FPC401四端口控制器:高速网络时代的端口控制利器2025-12-19 599

-

FPC402四端口控制器:高速数据传输与管理的理想之选2025-12-18 405

-

FPC如何重塑现代蓝牙耳机设计与性能2025-07-04 3545

-

深度解析高速串行信号的误码测试|线上讲堂2024-06-17 1472

-

什么是FPC软板YS YYDS 2023-06-03

-

《工业电器的节能设计与应用实例解析》pdf2022-02-08 731

-

PLC工程应用实例解析2021-04-21 1193

-

FPC连接器原理2021-03-25 4321

-

红外波形显示设计与制作实例解析2018-06-26 1129

-

888光立方设计与制作实例解析2018-06-25 2942

-

开关电源设计入门与实例解析2017-09-09 2239

-

解析柔性PCB:单层FPC/双面FPC/多层FPC的区别2017-03-09 4707

-

高速电路绘制实例集合2016-01-20 602

-

电机实例解析2012-08-19 3709

全部0条评论

快来发表一下你的评论吧 !