硬件电路如何设计调整内核供电

描述

DVFS 即动态电压频率调整,针对 SOC主频的不同,需要动态调整 SOC 的 Core Power。通过调整内核供电电压,实现SOC主频的调整。

例如:

SSD210在Core Power=0.9V时,主频为800MHz。

在Core Power=1.0V时,主频为1GHz

但是无论主频软件设置 800MHz/1GHz,都需要 Core Power=1.0V 启动(SSD210)。

那么硬件电路如何设计调整内核供电呢?

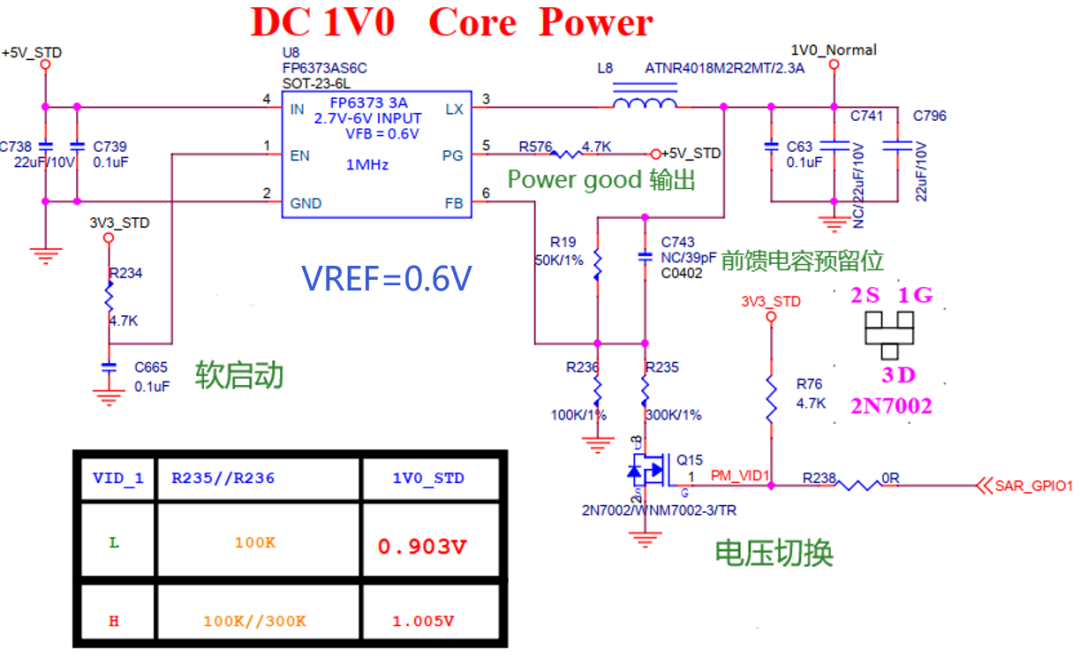

电路图如下,采用Q15控制反馈电阻,上电时,Q15导通,此时反馈电压等于输出电压在50KΩ和75KΩ( 100K并联300K )分压值,此时电路输出1V即提供内核启动电压。

当系统工作后,比如系统想要 降低功耗 ,或者在 高温情况下,需要动态调压,降低芯片主频以减少发热。只需要通过使用IO输出低电平,使Q15截止;那么,反馈电压等于输出电压在50KΩ与100KΩ分压值,便可调整Core的供电电压为0.9V,从而将SOC的主频降低为0.8MHz。

其中C665为缓启动电容。PG管脚为Power_good管脚(管脚为开漏输出,所以需要加上拉电阻),芯片正常输出电压后输出高电平,上图的PG管脚未连接到SOC的IO做检测。C743为前馈电容(NC是不贴装的意思),目的是为了 调整芯片输出响应速度 ,预留出来 方便后续调试 。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

请问对C6678内核供电,不采用支持SmartReflex技术类型的供电,比如只是简单的进行1V内核电压供电,会产生什么后果?2018-06-19 3054

-

为联网专用集成电路供电的高功率6+1稳压器参考设计2018-09-28 1848

-

有什么方法可以改远程开机设备的硬件ESP8266模块增加供电电路吗2022-03-01 1570

-

便携式CPU内核的供电问题2009-04-30 495

-

负反馈与音质调整电路2008-12-15 2072

-

调整电路图2009-05-11 905

-

补偿调整电路实例电路图2009-07-16 974

-

压阻加速计的信号调整电路2011-07-10 2074

-

Cortex-m3内核STM32芯片的硬件库程序2015-12-29 859

-

基于硬件虚拟化的安全的内核监控模型2018-01-17 835

-

米尔科技改内核调整GPIO在内核启动阶段方案2019-11-26 3681

-

AD9510:1.2 GHz时钟分配IC,PLL内核,分频器,延迟调整,8路输出2021-03-21 1000

-

嵌入式LINUX系统内核和内核模块调试2021-07-30 1966

-

工程师指南:如何动态调整合适的输出电压2023-06-15 2066

-

buck电路如何调整占空比?2023-09-12 8585

全部0条评论

快来发表一下你的评论吧 !