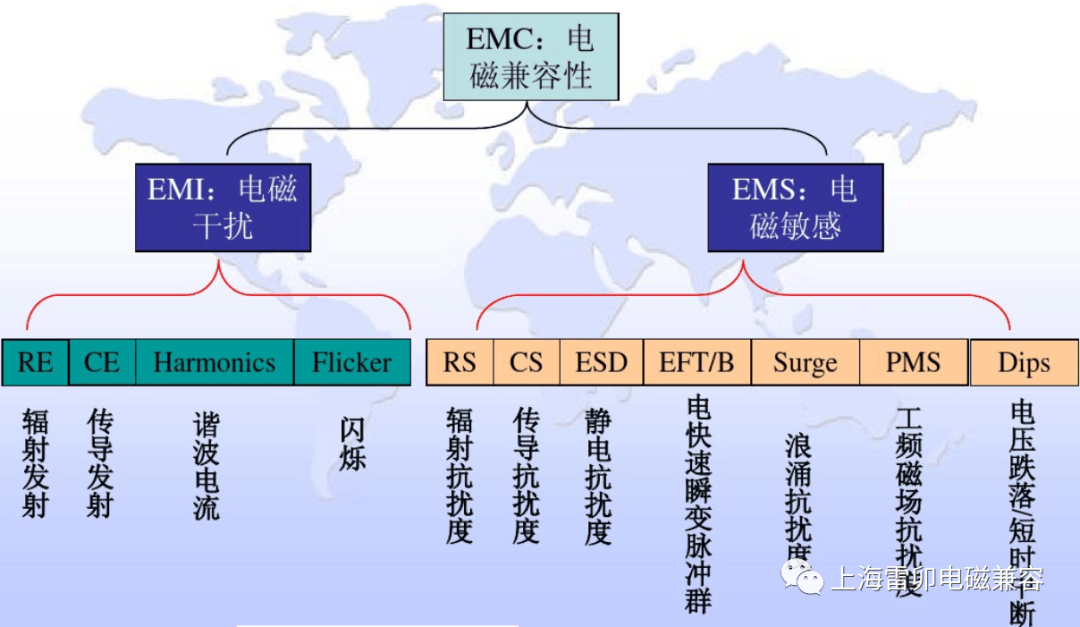

降低开关电源各种形式EMI的最佳方法

电源/新能源

描述

开关电源EMI(电磁干扰)不通过可能会带来以下几个坏处:

1. 电子设备受到干扰:开关电源产生的高频噪音和谐波可能会对周围的电子设备产生干扰。这些干扰信号可能导致其他设备的故障、降低性能或产生电磁兼容性问题。

2. 增加电磁辐射:开关电源在正常工作时会产生高频辐射,如果没有通过EMI测试,可能会超出国家和地区的电磁辐射标准限制。这种辐射可能会对人体健康产生潜在风险,特别是长期接触高强度辐射可能导致身体不适或健康问题。

3. 影响通信和无线设备:开关电源未经EMI测试可能会干扰通信信号和无线设备。这些干扰信号可能对无线电频段的正常通信产生负面影响,导致通信质量下降、数据传输错误或通信中断。

4. 不符合法规要求:一些国家和地区有严格的EMI标准和法规,要求电子设备必须通过EMI测试以确保其不会对其他设备或人体健康造成干扰。开关电源未经过EMI测试无法符合这些法规要求,可能会导致产品无法上市销售或面临法律责任。

EMI是评估电力电子开关电源性能上的一种关键参数,它可以通过多种方式加以降低,添加一个EMI过滤器似乎是最明显的选择,但可能还有更好的方法。今天EMC小哥带您了解更多降低EMI方法

l传导和辐射电磁干扰的降低方法。

l调整开关电压调节器的频率,以降低EMI.

l应用EMI过滤器

现代电子电力系统架构正变得越来越密集,并存在大量的互通互联关系,降低此类系统中的EMI变得越来越具有挑战性。

EMI的主要问题来源之一是开关电源(SMPS)。SMPS可以放在系统设计或印刷电路板 (PCB) 的外部,也可以是 PCB 上设计的一部分。

无论哪种方式,都必须降低EMI干扰,以便通过标准测试以及不会造成周围的电路错误操作。

本文上海雷卯EMC小哥将为电路设计人员提供一些在设计中控制EMI的最佳方法。

THE SMPS

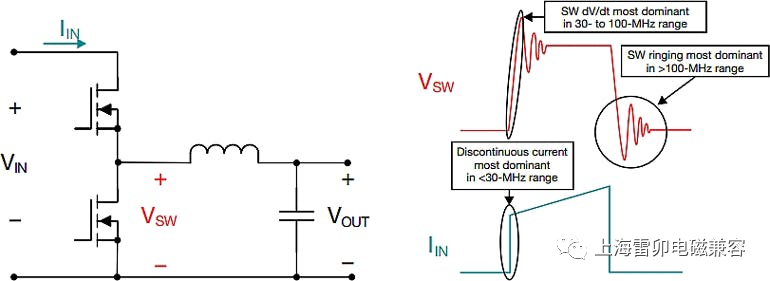

由于SMPS的效率比线性稳压器效率显著提高,已成为许多系统设计中的关键组件。功率硅MOSFET或GaN功率器件的开关导致不连续电流,是影响可靠系统运行的主要因素(图1)。下面接着将概述一些降低各种形式 EMI 的最佳方法。

本原理图显示了SMPS中的EMI源。

传导EMI降低方法

传导噪声比辐射噪声更容易分析;设计人员可以采用标准的电路分析方法。但是,EMI分析中的许多组件都是寄生的,不会出现在原理图上。

当电源开关设备打开和关闭时,它们会产生较大的不连续电流。这些电流将出现在降压转换器的输入端、升压转换器的输出端以及反激式和降压-升压型转换器设计的输入和输出端。

不连续电流会产生电压纹波,这些纹波可能通过导体相互接触传导到系统架构的其他部分。转换器输入端的此类电流应通过 输入滤波器进行滤波,以减轻电压干扰。功率转换器的输出也可能需要滤波器来帮助通过EMI标准 。

共模噪声通常更难分析,因为它通常是由寄生电容的充电/放电引起的,寄生电容在散热器或变压器绕组间电容最高。

辐射EMI降低方法

辐射噪声可以通过两种方式进行评估:

l用几米外的天线测量的电磁噪声。

l用靠近磁性元件的“嗅探器探头”测量的磁噪声。

电磁场的起因通常是电路中包含高频谐波的电流,这些谐波在回路中流动。减小环路面积、di/dt或电流峰值幅度将有助于降低辐射噪声。

开关调压器中的抖动

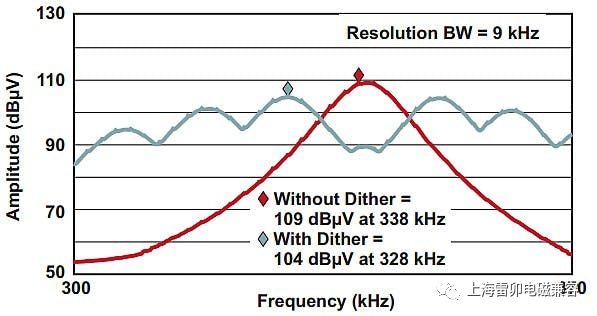

通过使用扩频调频(SSFM)技术,对开关调压器开关频率进行抖动,将降低EMI,并帮助设计人员当在滤波和优化布局无法满足EMI标准限制时通过一致性测试。

抖动略微调制开关稳压器中的基波开关频率。下面是它的工作原理。 开关电源的电磁辐射通过方波脉冲分布在许多频率上,其中最大的能量在基频处。

稍微改变基频(使用3%左右的典型调制)将调制峰值开关噪声能量,该能量将在多个基频之间共享。总电磁能量将保持不变,但窄带能量已降低,因此EMI有效降低。

在图1所示的示例中,5 dB峰值降噪可以在获得标准批准的情况下快速上市,还是将噪声峰值降低到标准限值以下(图2)。

2. 此图显示了在 330 kHz 附近有和没有抖动的准峰值测量值,显示抖动导致 5 dB 降低。

使用封装和引脚排列来降低 EMI

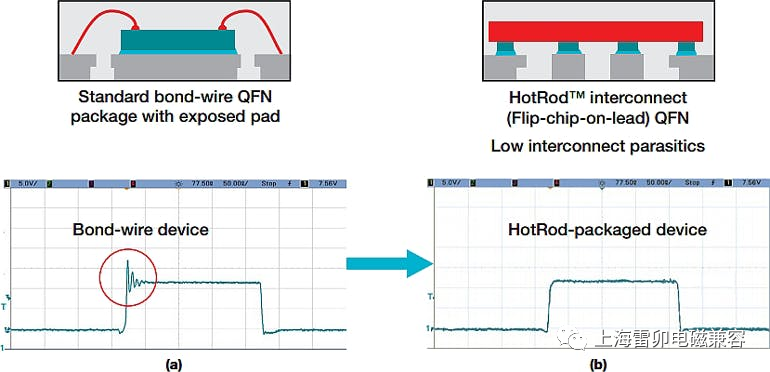

许多设计人员可能没有考虑到,选择有助于降低EMI的IC封装类型的好处。一个很好的例子是在SMPS中封装功率MOSFET。

这些类型的电源转换器使用快速开关电压转换速率 (dv/dt) 以及高电流速率 (di/dt),这将增加系统中的 EMI。

设计人员可以添加EMI滤波器作为解决方案。但是,在这样做并增加设计尺寸(从而降低功率密度)之前,请先了解也有助于降低EMI的封装技术。

以下是如何利用功率MOSFET封装设计改善EMI的一些示例。 排列电源引脚和GND引脚相邻,这样可以平行放置滤波电容,尽可能的减小环路,改进高频EMI。

此外,两个相等和并联电感的等效寄生环路电感减半。

因此设计时的优化布置引脚位置可以降低高频EMI. QFN封装中的键合线有时可以通过使用铜柱和引线框架与芯片之间的倒装芯片互连来消除(图3)。

3. 这种典型的 QFN 封装使用键合线将芯片连接到裸露焊盘,电源开关在该焊盘中表现出明显的振铃 (a)。

改进的封装采用铜柱和从芯片到引线框架的倒装芯片互连,从而消除了电源开关中的振铃 (b)。

循环输入电流将产生相反的磁场,导致H场抵消并减少辐射发射。

因此,通过创建高di/dt输入环路的对称布局,产生的(相反方向的)磁场可以相互抵消。

降低封装EMI的另一种方法是在另一个PCB层(如顶层电源电路正下方的第2层)的两个电感环路下方放置一个连续接地层,用于返回电流。

电磁干扰滤波器

EMI滤波器可以是分立式的,也可以是模块化的。电源设计人员将不得不在时间、尺寸和成本方面选择最有利于其设计需求的电源。

高功率密度电源架构中的EMI滤波器

在高功率密度电源中,最大限度地减小EMI滤波器的尺寸至关重要。没有磁性元件的滤波器设计更紧凑,从而达到良好的功率密度。

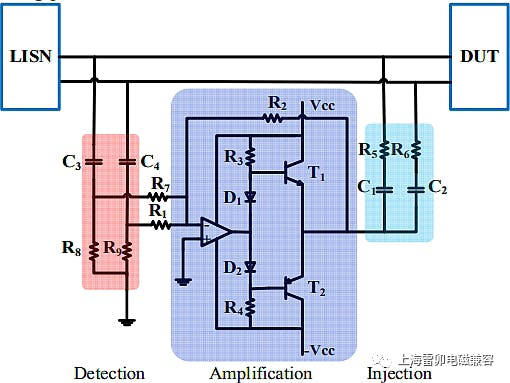

例如,图4中的滤波器设计使用电压检测和无磁性元件的电流注入拓扑。

为了增强滤波器的输出电流和功率以及改善插入损耗(IL),在放大器输出后面使用推挽式功率放大器电路,以使输出电流足够大。

这种滤波器设计足够稳定,可以取代无源EMI滤波器。

4. 这种高性能滤波器设计,没有磁性元件,可以支持60 A量级的高输出电流。

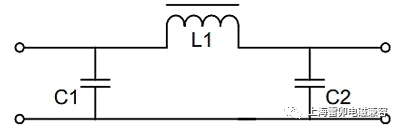

屏蔽EMI滤波器是控制传导EMI的最后努力 差模(DM)EMI滤波器(图5)可能会在电源系统中产生传导EMI干扰。

图为π型EMI滤波器

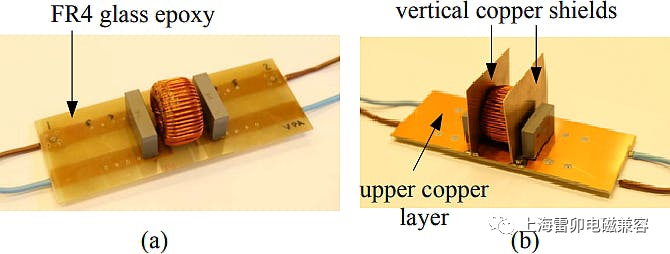

5.在DM滤波器下方放置铜屏蔽可能会有所帮助(图6a)。当所有其他方法都失败时,在PCB的顶部和底部添加铜层,并在滤波器的两侧添加两个垂直铜屏蔽(图6b)。

6. DM EMI滤波器有两种不同的配置:在(a)中,滤波器位于单铜层PCB的顶部,每个滤波器元件之间的距离为3.5毫米。在(b)中,滤波器位于双铜层(顶部和底部)PCB和两个垂直铜屏蔽层上,每个滤波器组件之间有3.5 mm。

总结

设计人员需要了解以及工具,以最大程度地减少电路板设计之间的传导和辐射EMI干扰。

本文***上海雷卯EMC小哥***重点介绍SMPS,它比线性电源大大提高了效率,但为了最大限度地降低EMI干扰,也可能需要非常耗时。

本文介绍的技术和工具提供了改进SMPS设计的方法,以帮助设备通过EMI标准测试,同时最大限度地缩短设计时间。

审核编辑:刘清

-

有哪些方法能够降低开关电源EMI的影响呢?2023-11-07 1864

-

开关电源传导EMI预测方法2023-09-22 845

-

降低开关电源的EMI的方法2023-09-21 2412

-

开关电源的EMI2021-09-15 1656

-

如何降低开关电源中产生的EMI辐射2020-02-13 6570

-

开关电源中EMI的来源及降低EMI的方法2019-06-03 5697

-

浅谈开关电源中EMI来源 电源模块如何降低EMI2018-10-17 9098

-

工业及汽车系统:如何有效的降低开关电源EMI干扰?2018-08-22 4481

-

开关电源中传导差模EMI的抑制方法2017-09-11 1076

-

【EMC家园】开关电源传导EMI预测方法研究2016-04-20 5554

-

开关电源传导EMI预测方法研究2011-11-01 5235

-

开关电源电磁干扰(EMI)机理及新的抑制方法2009-07-15 2147

-

开关电源emi设计2008-07-13 5866

全部0条评论

快来发表一下你的评论吧 !