IC设计:接口X态隔离设计

EDA/IC设计

1078人已加入

描述

虽然真实芯片中,寄存器初始状态值只会为1或者为0。但是在RTL级仿真过程中X态的传播经常会给咱们造成很多麻烦,例如部分信号期望为0,但是仿真结果显示为X态。

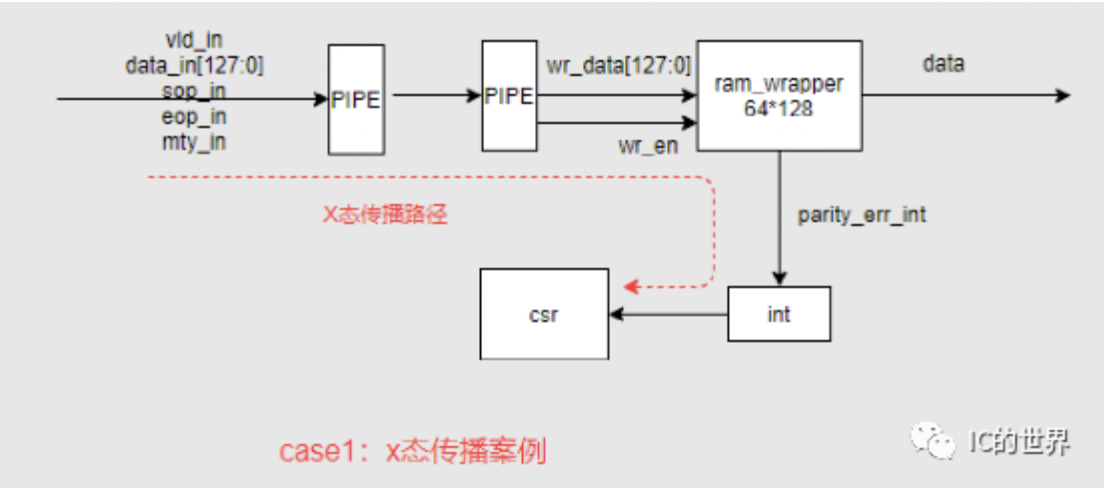

1、X态传播案例

如下案例中:

入口数据mty_in[3:0]表示data_in[127:0]中无效的字节数,例如当数据最后一拍mty_in[3:0]为4’d2 表示data_in[127:0]中[15:0]是无效数据,由于入口数据是其他模块送给咱们的,有可能data_in[15:0]是X态,此时data_in[127:0]一路打拍写入了ram_wrapper,ram_wrapper存在parity_err_int计算逻辑,此逻辑的输入是wr_data[127:0],即源头是data_in的128bit,只要data_in[127:0]存在1bit X态,则计算得到的parity_err_int就是x态,最终会经过中断模块(int)传播到寄存器配置模块(csr)。NOTE: 真实的芯片中,不存在此bug。

这只是其中一个微不足道的小案例,类似的场景还有很多,X态传播给RTL仿真带了了很多麻烦。那有什么解决方案呢?这里有个小技巧:对输入数据进行X态隔离,让模块内部的信号都是稳定的状态。

2、X态隔离代码实现

隔离效果如下:输入数据data_in在mty_in不为0时,存在值为x态的无效字节,而经过简单的处理后,模块内部的data_in_d1中所以bit均为稳定值,其无效字节被赋值成了0。

核心处理逻辑:data_exit_invld_bits为1时表示数据的最后一拍,且data_in存在无效字节,此时将data_in_d1_nxt赋值给data_in_d1。

module 以及简陋的testbench 代码:

`timescale 1ns/1ps

module x_state_handle_top ( ) ;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

EiceDRIVER™ 2EDR8259H等双路隔离栅极驱动器IC深度解析2025-12-21 1050

-

EiceDRIVER™ 2EDR8259H等双通道隔离栅极驱动器IC:设计与应用详解2025-12-20 1560

-

比较不同类型的隔离接口IC:光耦合器与数字隔离器2023-08-15 2089

-

IC封装隔离放大器/隔离电源/变送器产品外接保护电路方案2021-11-24 1517

-

什么是电流隔离LVDS接口2021-03-02 1950

-

ADI新推出的隔离接口的性能分析2017-09-15 801

-

射频IC应用编程接口设计2017-01-14 875

-

CAN总线接口信号隔离收发IC2016-11-18 1417

-

LED驱动IC在隔离方案和非隔离方案上的应用2012-11-29 2620

-

总线接口中隔离的应用2010-03-17 3687

-

物理安全隔离常用接口有哪些?2010-01-08 740

全部0条评论

快来发表一下你的评论吧 !