TTL电平学习笔记

描述

- TTL电路基本原理

要实现输出电平在0/1之间变换,需要三极管的数量最少只需要一个,而TTL电路使用了4个三极管,用较多的器件去实现相同的功能,必定要有性能上的提升,否则这种电路设计就是一种浪费。对于TTL电路而言,使用成倍的器件需要换来的性能包括以下几点:

a. 提高开关速率

b. 提高带载能力

c. 提高抗干扰性

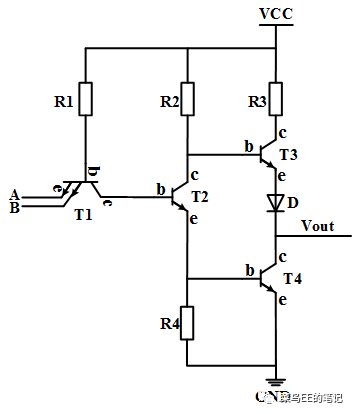

图1

TTL电路如图1所示,当输入A/B有一个为低电平时(假设为0V),T1管的基极被钳位到0.7V,不足以使得T2、T4管导通,所以T2的集电极电位为高,T3导通,Vout输出为高。当A/B输入都是高电平时(假设为3.6V),则T1的基极电压为4.3V,该电压可以使T2、T4饱和导通,从而T1的基极电位被钳位在2.1V(三个PN结的压降),T4导通后,T4的基极电位为0.7V,T2此时为饱和导通,导致T3的基极电位大概为1V左右,这个电压不足以使得T3和二极管D同时导通,故Vout输出为低电平。

在TTL电路中,使用推挽输出目的是为了增强带载能力;二极管D可以砸T4导通时,防止T3导通导致T3、T4直通;T2的设置主要是为了给T3、T4提供驱动。在Vout由低变高时,T2的基极电荷在T1的作用下被迅速抽走,关断比较快,T2关断,T3即打通。但是T4的基极电荷只能通过R4放电,导致T4关断得比较慢,如此以来,就有一小段T3、T4直通的时间,因此需要增加电阻R3限制短路电流。

- 为什么T2、T4为饱和导通

首先看T4,T4导通时,其基极电压为0.7V,输出端与后级电路匹配时,Vout通过下一级的R1、T1的发射结上拉到VCC,这个集电极电阻足以使其饱和导通(不行就设置好R1的阻值)。T2是必须要饱和导通的,因为T2工作在放大区会使Vout的输出具有不确定性(影响T3的基极电位),T2的饱和导通是由其基极电流保证的。如前述,T2导通时,T1的发射结反偏,集电结正偏,三极管T1工作在倒置态。此时T2基极电流与T1基极电流相当,设置R1即可保证使2饱和。

- 如何理解三极管T1的倒置工作状态

随便翻开一本教材或者TTL的资料,都会写三极管T1在输入为高电平的时候,处于倒置放大的工作状态,这种感觉好像是电路设计者精心这么设计的,故意使用三极管的倒置放大来实现什么目的,但对为什么这么用又没有下文。实际上,这只是对三极管工作状态的一种客观描述。我建议教材不要单独把这个状态单独强调一下,没有什么用还容易误导人,除非把龚总原理给讲清楚。得出以上结论的理由如下:

首先,三极管各个级之间是有寄生电容的,当三极管由导通变为截止时,先要把基极的电荷给放掉,这个放电过程需要时间,直接影响三极管的开关速度,这是前提。

采用TTL电路的解法时,当输入为高电平时,T1倒置放大,T2的饱和由R1保证;当输入由高变低时,T1的基极被钳位到0.7V,由于T2、T4关断需要时间,T1的集电极电位仍保持在1.4V,因此,T1处于放大状态,可以迅速地抽取T2基极的电荷,使T2迅速关断。如果换一种接法,让T1的集电极作为输入,如图2所示:

图2

当T1的输入为高时,T1的基极电位为2.1V,集电结反偏,发射结正偏,该电流可以使得T2饱和导通。当T1的输入由高变低时,T1的基极电位为0.7V,发射极电位为1.4V,T1处于倒置放大状态,此时T2的基极电流显然要小于T1处于放大区的电流,因此T2需要更长的时间关断,影响了其开关速度。

通过以上说明可以发现,T1是否工作在倒置放大无需额外说明,哪种接法能提供更快的开关速度才是关键。

- 电平门限计算

TTL电平门限也是没有标准的,因厂家而异,但也需要满足一定的范围,以图1电路为例,计算如下。

输出高电平:

如果输入电平由高逐渐降低时,降到0.7V,T4会先关闭,T2仍然导通,此时假设R4的电压为临界值0.7V,则,T3的基极电压为:

因此,有:

输出低电平视饱和程度,取最大不超过0.4V。

输入低电平:

输入为低时,输出应为高,前面已经分析,要使输出为高,临界条件为T4刚关闭时,此时输入不应超过1.4V。假如以不以T2导通为标准,则输入低电平最大不应超过0.7V。

输入高电平:

按前述分析,输入高电平最低不应低于1.4V。

-

TTL电平的应用场景和实例2025-01-16 3706

-

cmos电平与ttl电平如何转换 怎么判断ttl电路高低电平2024-02-22 5513

-

TTL电平与RS232电平的区别2023-02-07 6823

-

ESP8266学习笔记相关资料下载2021-12-13 2001

-

什么是TTL电平,什么是CMOS电平,他们的区别2021-11-30 2959

-

ttl电平与cmos电平的区别2019-08-19 31022

-

TTL电平与CMOS电平的区别,TTL & CMOS2018-09-20 9394

-

详解TTL和CMOS电平2017-11-15 2486

-

ECL电平、LVDS电平、TTL电平_简单的比较2016-08-29 2090

-

TTL和CMOS电平基础知识2009-11-28 1456

-

TTL电平 CMOS电平推挽输出2007-12-05 3316

-

TTL电平与CMOS电平的区别2007-10-10 8904

全部0条评论

快来发表一下你的评论吧 !