ECL/PECL/LVPECL电平学习笔记

描述

LVPECL电平是常用的一种逻辑电平,大部分资料对该电平的描述为:由ECL电平发展而来,但是对其逻辑电平门限的确定、为什么要加一个偏置电平以及LVPECL电平与ECL电平在电路结构上的差异鲜有论述。因此,对在学习该电平中遇到的困惑整理如下:

1.ECL电路的基本原理

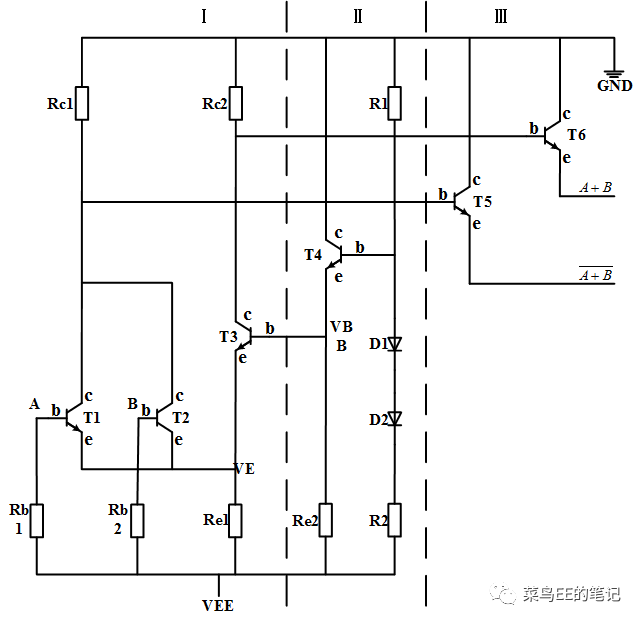

图1 ECL电路

ECL电路如图1所示,其分为输入级、中间级和输出级三部分。输入级由T1、T2、T3三管构成,当A、B有一个为1时,T1和T2至少有一个管开通,VE电位将被抬高,导致T3截止;当A、B都为0时,T3则会开通。输出级由T5、T6组成的射随器构成,当T1、T2至少有一个开通时,T5的截止,输出为0,而此时T6导通输出为1。即T5输出 ~(A+B),而T6输出A+B。中间级的作用为给T3提供合适的偏置电压VBB,Re2有抑制温漂的作用。

2.ECL电路为什么不直接输出,需要经过射随器输出?

考虑直接输出的情况,输出高电平为:

输出低电平为:

当ECL电平直接耦合时,设VOH直接接到T1管,则T1管的基极电位为0(逻辑1),集电极电位电位小于0(因为有Rc1的压降),集电结正偏,T1管将进入饱和区。ECL为获得较高的开关速度,设计时需要保证三极管不饱和,因此需要经过射随器输出,降低其输出高电平,同时,经过射随器输出,其输出阻抗变小,驱动能力也会变强。

3.逻辑电平门限的确定

ECL电平的逻辑电平门限是没有标准来限定的,其门限的大小需要满足各厂家提供数据手册。但是,根据电路结构分析,各电平门限以及摆幅大小也有一定的限制的条件,分析如下:

由电路结构可知:

由于三极管不能进入饱和区,因此需要满足:

因此,摆幅满足:

对逻辑高电平:

为保证T1、T2导通时,T3截止,有:

对逻辑低电平,为保证T1、T2截止时,T3导通,有:

由摆幅要求:

4.PECL与ECL电路的差异

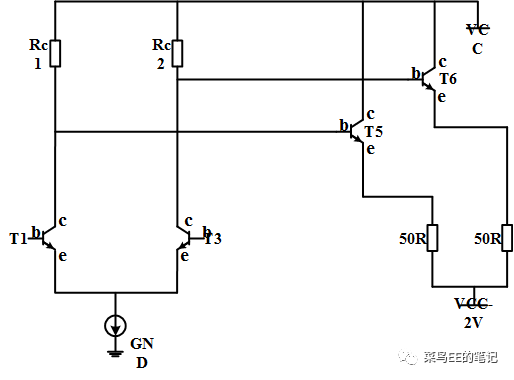

图2 PECL电路

大多数资料对PECL电路的描述为:把ECL电路的高电平变成正电平,即得到PECL电路。但是,其给出的电路图与ECL电路却大相径庭。中间级去哪了?为什么直接使用差分输入?输出为什么要接到到VCC-2V,一概没有交代,看得人一头雾水,现整理如下。

首先PECL为差分输入,ECL虽然也有两个输入,但其输入其实相当于取或,和单端输入单端效果是一样的。在有关资料里,描述为“原理与单端输入,双端输出的差分放大电路类似”。因此输入端的差异我个人判断是ECL/PECL的应用场景不同导致的,ECL用于单端转差分或者需要同时获得其输出的反信号的场合,PECL则为差分输入、差分输出的场景(未做具体考证)。由于输入级的差异,PECL自然不需要中间级提供偏置电压了。

5.为什么PECL的输出需要通过50R电阻接到VCC-2V?

PECL的输出高电平为VOH=2.4V,输出低电平VOL=1.6V,为达到这个电平门限要求,需要给输出电平提供一个2V(VCC-1.3)作用的共模电压(输出高低电平的中间,使得获得的动态电平范围最大)。为满足此要求,一般在输入端会加一个VCC-1.3V的直流偏置,提供共模电压,以图2电路为例,当T1端输入为高,为使得T1不进入饱和区,则T1的集电极电压最小为VCC-1.3V,如此,为了使输出的三极管不进入截止区,则其偏置电压不应大于VCC-2V,同时为了避免功耗过大,终端的偏置电压不应取太小,故取VCC-2V。50R的电阻则是用于阻抗匹配,避免产生反射。

-

深入解析SN65EL11:5V PECL/ECL 1:2扇出缓冲器2025-12-25 1114

-

LVPECL 与 LVDS 及 PECL 与 LVDS 的互连技术解析2025-08-08 1713

-

LVDS、PECL和CML输出/入结构介绍2025-06-07 1670

-

ecl差分接入的0.8v摆幅是否可以驱动ad10242,lvpecl电平是否可以满足标准?2023-12-18 626

-

详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML资料下载2021-04-09 6630

-

ADCMP551/ADCMP552/ADCMP553:单电源、高速PECL/LVPECL比较器2021-03-20 1347

-

FPGA的常用电平标准2021-01-07 4797

-

信号逻辑电平标准的详细说明2021-01-05 1926

-

ECL PECL LVPECL信号都是什么?它们的优缺点和电路图详细剖析2017-04-26 25294

-

ECL电平、LVDS电平、TTL电平_简单的比较2016-08-29 2180

-

常用电平标准及解析2013-09-18 8613

-

各种电平标准总结2011-05-11 5169

-

常用的电平标准2010-06-01 927

-

电平标准2008-07-21 3233

全部0条评论

快来发表一下你的评论吧 !