ZYNQ设计的基本流程

描述

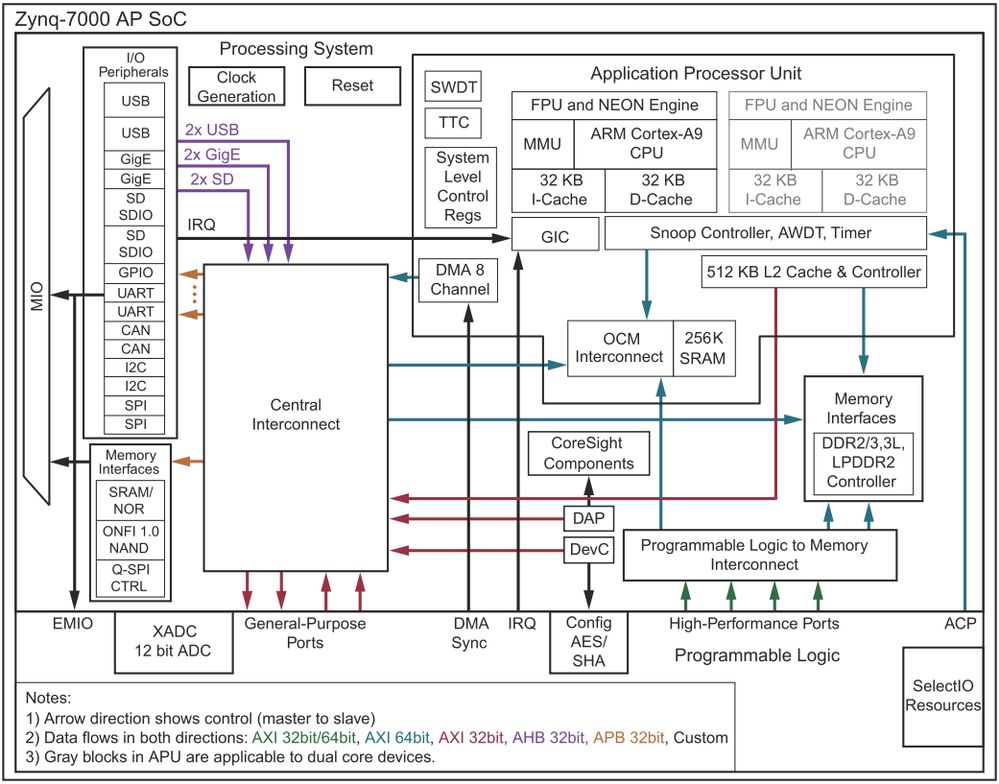

ZYNQ内部包含PS和PL两部分,PS中包含以下4个主要功能模块:

Application processor unit (APU)

Memory interfaces

I/O peripherals (IOP)

Interconnect

ZYNQ内部的总体框架如所示,PS中包含2个ARM Cortex-9的内核,一些基本的外设扩展口以及Memory接口。PS和PL的相互通信通过两个通路完成,分别是GP(General Purpose)Ports和HP(High Performance)Ports。

GP Ports包含2个Master接口和2个Slave接口,符合标准的AXI协议数据位宽是32bit。HP Ports包含4个接口,全部是PL作为Master;有两个专用的连接到DDR Controller的接口和一个连接到OCM的接口。HP与GP相比,最大的特点在于有额外的FIFO作为Buffer,可以提高传输效率和数据吞吐量。

所以从功能角度,GP Ports主要用于寄存器的读写以及小数据量的传输;HP Ports用于大量数据的传输,主要是Memory数据的读写。

ZYNQ中最常用的设计思路是将主程序放在PS中完成,在PL中设计相应的逻辑功能作为PS的外设使用,将逻辑设计封装成IP,且每个IP都包含一个标准的AXI-Lite接口。PS对于逻辑设计的控制是通过控制逻辑设计的功能寄存器,进而控制逻辑设计进行相应的操作,同时将工作情况通过状态寄存器返回给PS端。如果逻辑设计与PS端需要进行大量数据的交互,则会在逻辑设计中增加AXI-Full接口,与PS的HP Port相连。

综上,ZYNQ设计的基本流程包含以下步骤:

Vivado中搭建ZYNQ平台,完成基本外设控制。

创建逻辑设计,并封装成IP。

ZYNQ设计中调用封装的IP。

对设计的IP进行仿真。

ZYBO开发板简介

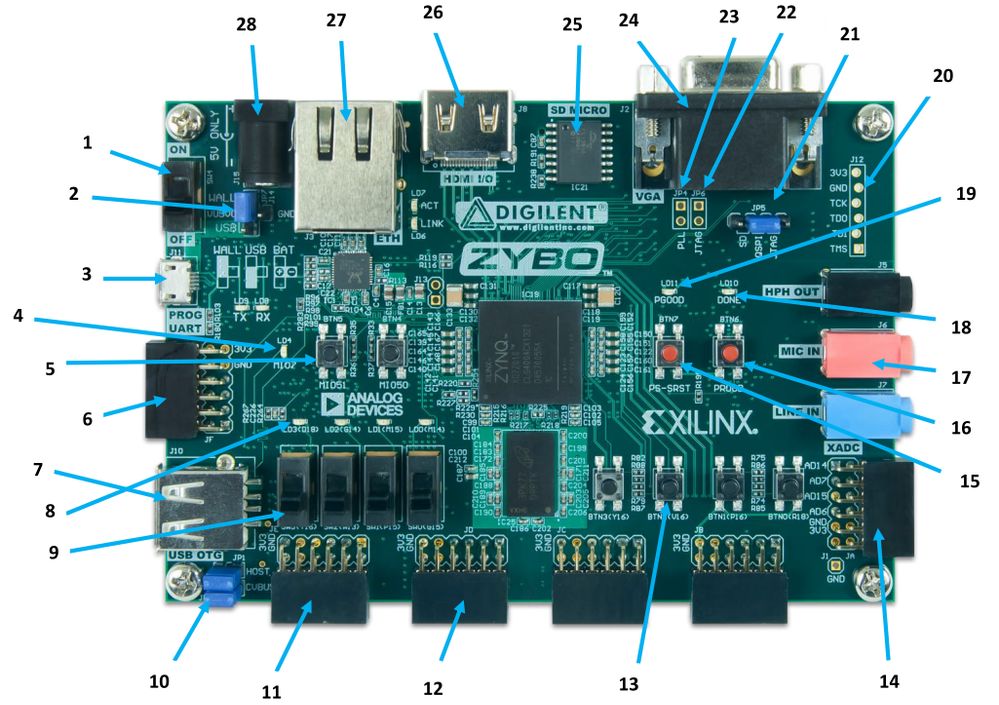

ZYBO是Digilent开发的以XC7Z010-1CLG400C为核心处理器的开发板,其主要功能包括有:

1片32bit位宽,512MB容量的 DDR3

1个 HDMI port

1个VGA source port

1个(1Gbit/100Mbit/10Mbit) Ethernet PHY 与RJ45接口

1个MicroSD slot

1个OTG USB 2.0 PHY

1个外部 EEPROM

1个耳机输出接口和1个麦克风输入接口

1片128Mb QSPI Flash作为加载Flash

1个JTAG接口和1个USB-Converter下载接口

GPIO: 6 pushbuttons, 4 slide switches, 5 LEDs

6个 Pmod ports

其板上器件分布情况如图 2和图 3所示。

图2

图3

Vivado中进行ZYNQ硬件部分设计

Step1: Viavdo中选择XC7Z010-1CLG400器件,建立工程。

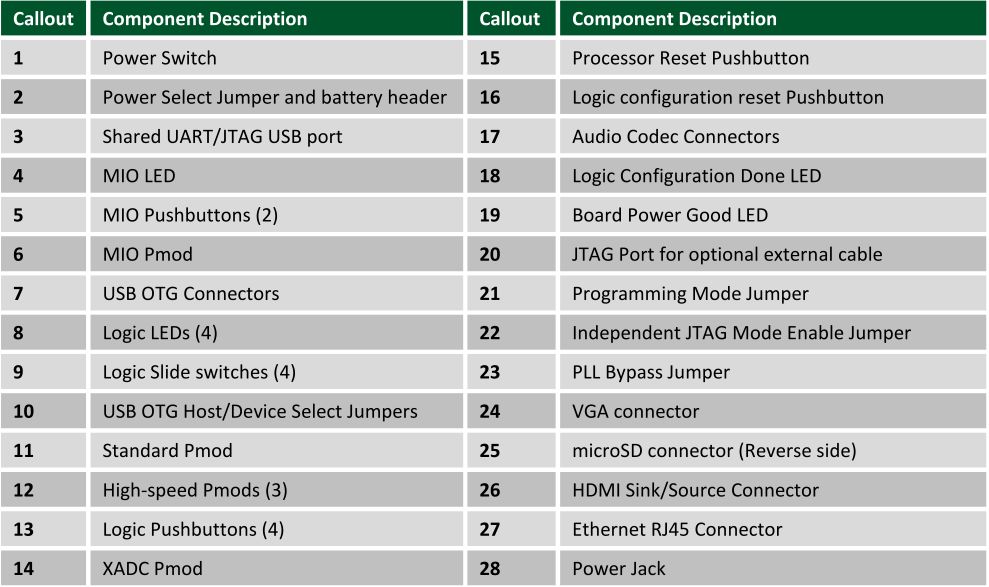

Step2: 建立Block Design。

图 4

Step3: 加入ZYNQ7 Processing System和其他所需要的外设IP。

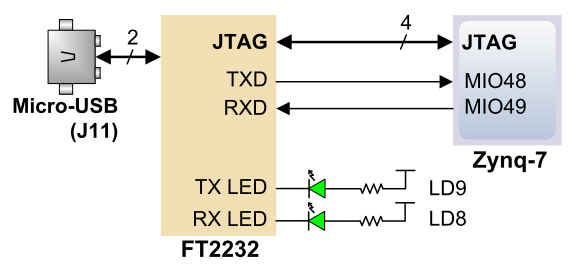

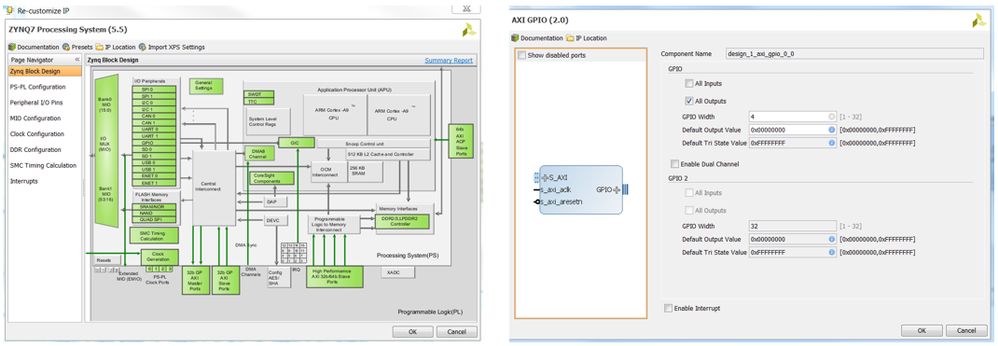

点击“Add IP”,加入ZYNQ7 Processing System和AXI GPIO,双击IP可以对其进行配置。该实验中ZYNQ7配置使能UART,引脚为MIO48和49,其ZYBO相关电路图如图 5所示。(注:如果需要在Step11中选择Hello World工程,则需要使能UART)。AXI GPIO的位宽设置为4,其余为默认配置。

图 5

图 6

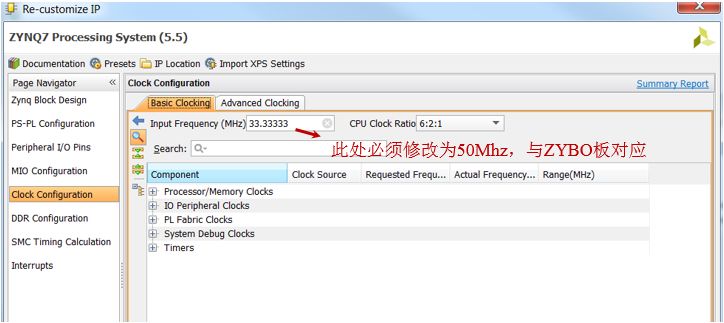

注意:这里有个地方非常容易出错。在Vivado建立工程选择器件的过程中没有选择ZYBO开发板的配置,而是直接选择的XC7Z010-1CLG400C器件的配置。系统默认的ZYNQ7 Processing System配置中Input Clock Frequency是33.3333MHz,而ZYBO板上为50MHz。此处必须修改过来,否则后面的系统时钟会完全错乱,导致软件工程无法运行。

图 7

Step4: 点击“Run Block Automation”,其作用是完成ZYNQ7 Processing System专用引脚的连接,包括FIXED_IO和DDR引脚的连接。

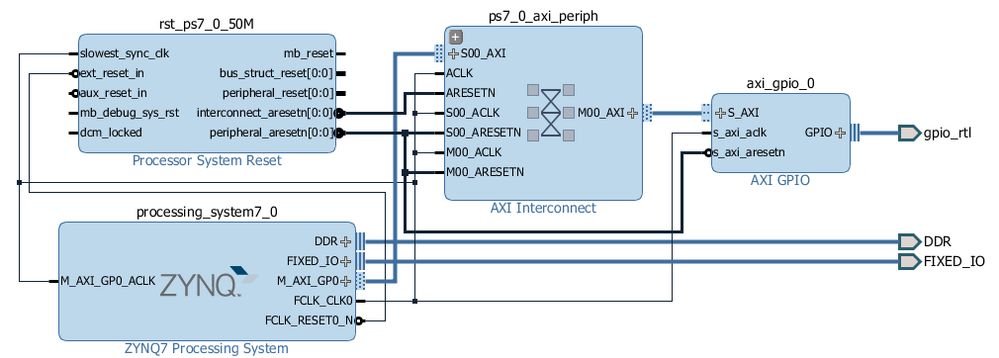

图 8

Step5: 点击“Run Connection Automation”,其作用是自动完成ZYNQ与外设的连接,连接是按照工具对于用户所设计系统的理解,如果需要进行修改,可以手动更改Block中的连线。该操作工具会默认增加:

AXI interconnect

Processor System Reset

自动完成了外设IP的AXI-Lite端口与ZYNQ7 Processing System的连接,默认接法是ZYNQ的FCLK_CLK0作为外设AXI时钟,Processor System Reset产生外设复位信号连接到所有外设的复位端口。

将AXI GPIO的引脚引出。

可以使用“Regenerate Layout”,重新布局Block Design。

图 9

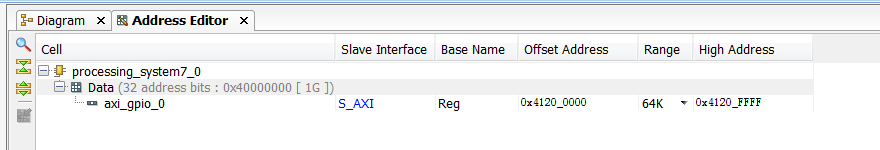

Step6: 在“Address Editor”中查看、修改外设在总线上的地址。

图 10

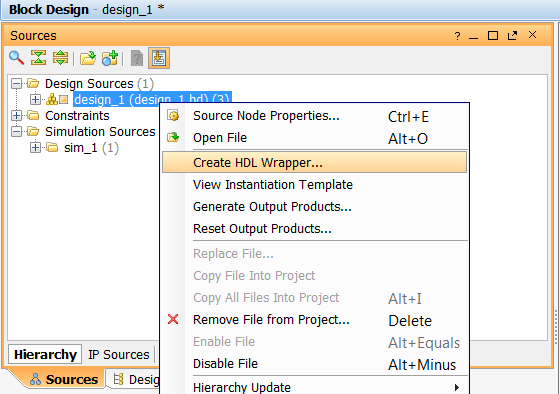

Step7: 首先在Block design界面右击弹出的菜单中点击Validate Design,以验证Block Design的设计和连接是否有错误。至此Block Design完成了,但是还需要根据Block Design的配置生成相应的源代码。右击.bd设计,并选择“Create HDL Wrapper”。随后即生成了相应的HDL代码。

图 11

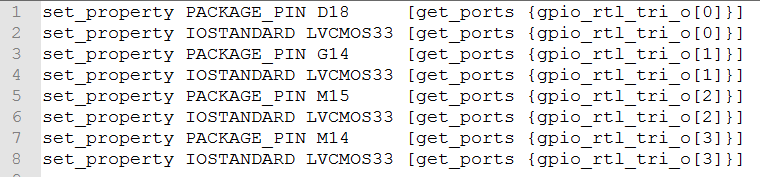

Step8: 对于PL端的外接引脚,需要设置相应的Constraints。

图 12

图 12

Step9: 与普通FPGA设计一样,完成Synthesis、Implementation和Generate Bitstream。

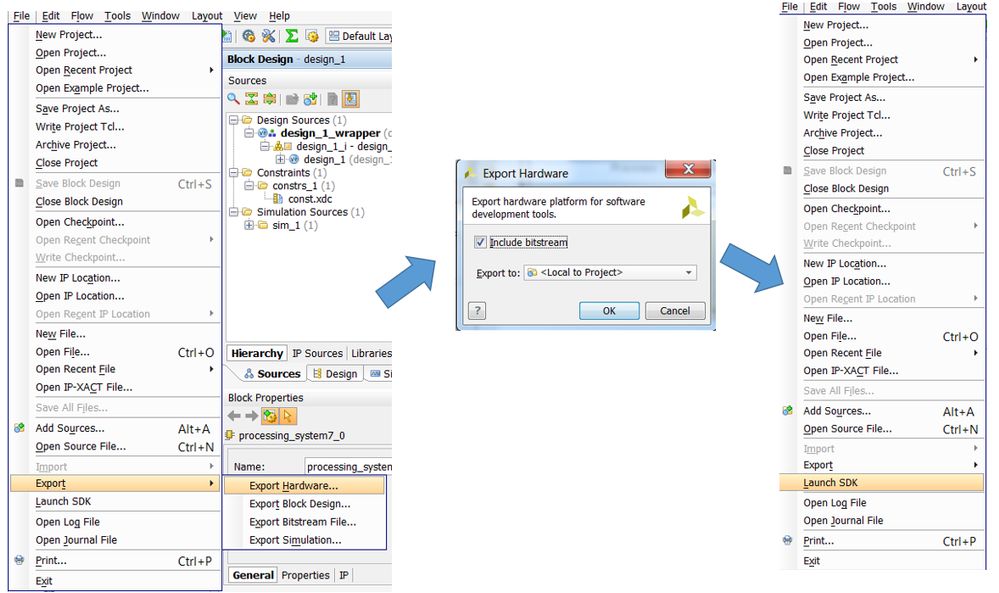

Step10: 将Step9中完成的硬件设计导入到SDK开发平台下。

图 13

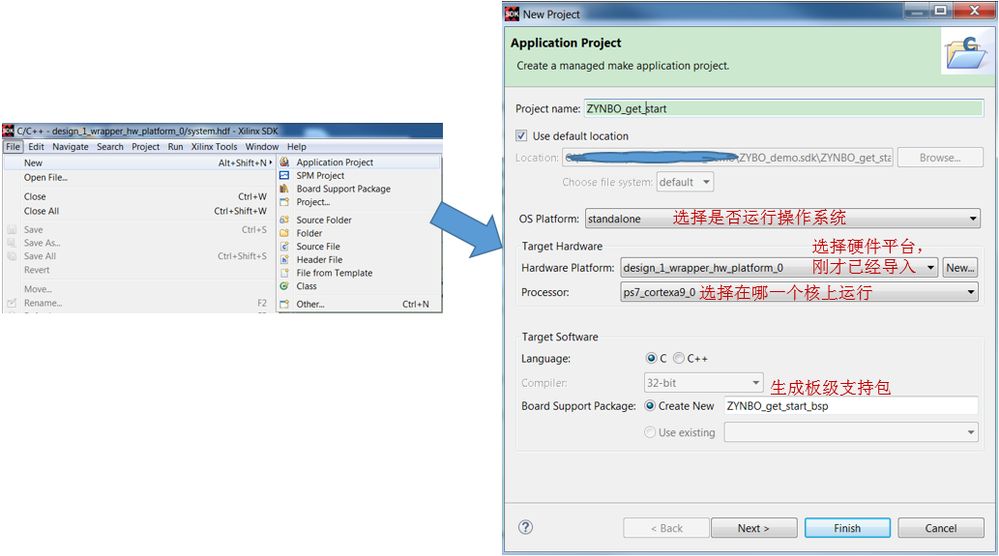

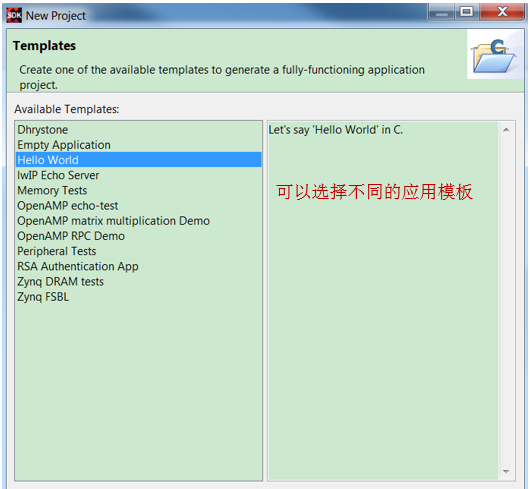

Step11: 从这一步开始,开发平台转移到SDK平台。此时硬件平台已经确定,接下来是软件的开发。首先在SDK中建立软件工程。

图 14

图 15

Step12: 在新建工程中完成C代码的设计。

#include

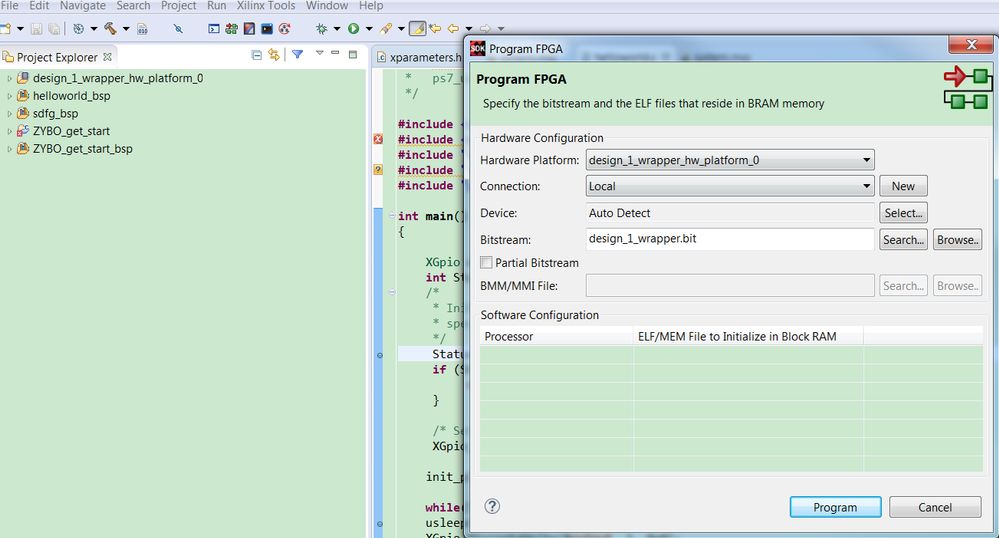

Step13: 首先点击“Program FPGA”,将硬件平台下载到ZYNQ中。

图 16

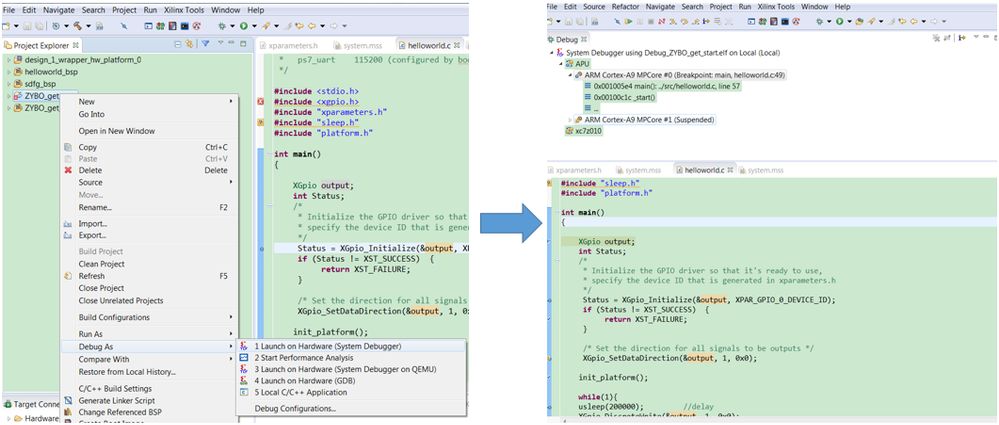

Step14: 运行软件工程进行调试。

图 17

在ZYBO板上也能看到LED灯闪烁,至此完成了ZYNQ的一个基本设计的所有开发流程。

DK中进行ZYNQ软件部分设计

首先对“Vivado中进行ZYNQ硬件部分设计”中让LED闪烁的C代码做详细的注释。

int main()

{

/*定义外设对于的类型指针,用于绑定外设,便于后面程序调用时选择

* 外设

*/

XGpio output;

int Status;

/* XGpio_Initialize()函数是xgpio.c中的函数,在BSP Documentation可以

* 查到该函数的描述。

* int XGpio_Initialize(XGpio * InstancePtr, u16 DeviceId)

* InstancePtr为GPIO类型的指针

* DeviceId是在板级配置中已经定义好的外设的ID,该定义包含在BSP的xparameters.h中

* 即在xparameters.h已经为该硬件设计中的每一种类型的多个外设设置了唯一的ID

* 例如设计中如果有2个GPIO外设,则ID分别为0和1.

* 该语句完成之后将ID对应的外设对象与该指针进行了绑定,后面可以通过调用该指针指

* 定到该外设

*/

Status = XGpio_Initialize(&output, XPAR_GPIO_0_DEVICE_ID);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

/* void XGpio_SetDataDirection (XGpio * InstancePtr,

* unsigned Channel,u32 DirectionMask )

* InstancePtr:外设指针,用于指定到对应的外设设备,已经与外设绑定

* Channel: 每个AXI_GPIO中可以有两个32bit的GPIO端口,该参数用来

* 选择是该外设中的哪一个端口

* DirectionMask:选择GPIO的方向,0为output,1为input

* 该函数的作用是设置GPIO的方向,如前所述,可以通过output指定到

* 该GPIO外设,

*/

XGpio_SetDataDirection(&output, 1, 0x0);

//初始化ARM内核

init_platform();

while(1){

usleep(200000); //delay

XGpio_DiscreteWrite(&output, 1, 0x0);

usleep(200000); //delay

XGpio_DiscreteWrite(&output, 1, 0xF);

};

cleanup_platform();

return 0;

}

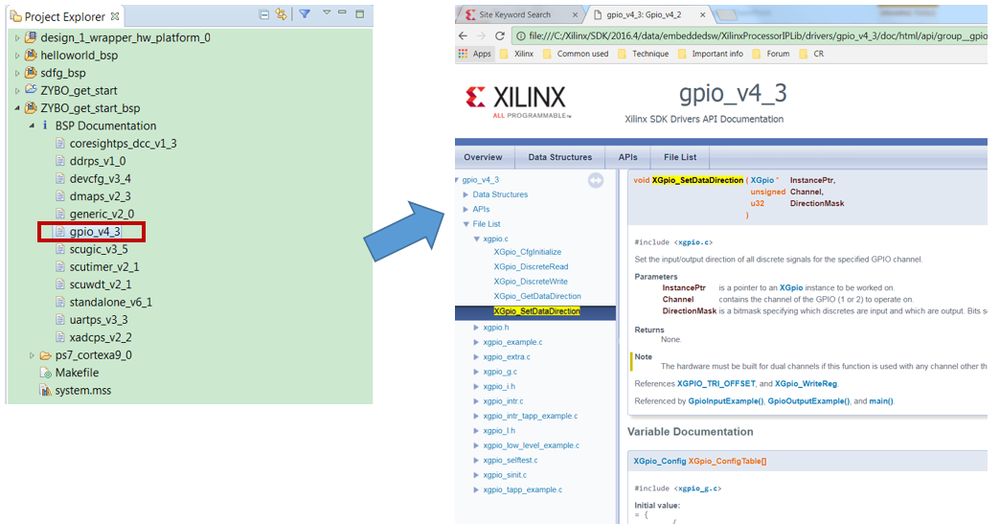

以上调用的这些函数,其定义及使用方法全部可以在BSP(Board Support Package)板级支持包中找到。当在Vivado平台中设计完成硬件,将其导入到SDK平台时,工具会根据硬件设计中使用到的外设,自动生成相应的板级支持包。在SDK的“Project Explorer”界面中可以查看,并且可以在其中打开相应的BSP说明文档,如图 18所示。

图 18

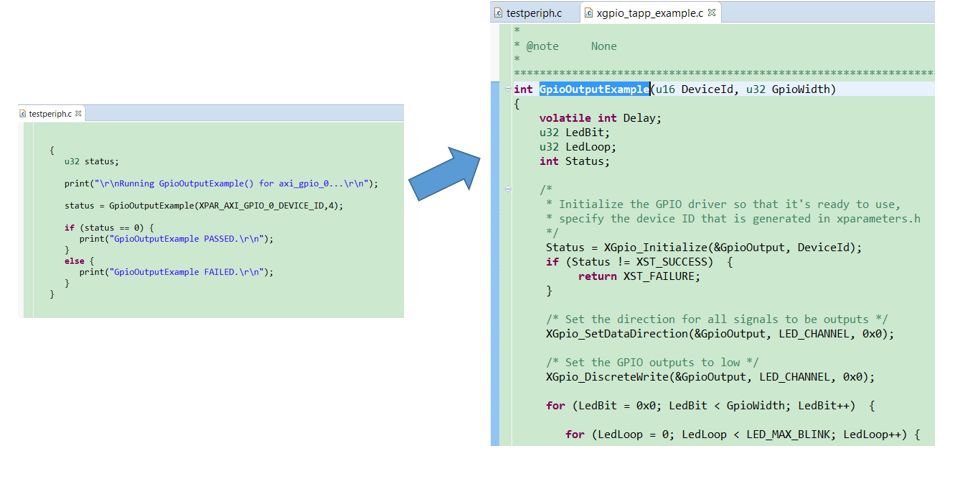

但是虽然BSP中提供了所有相关的API函数,但是对于初学者来说,想搭建一个可以实现基本功能的平台还是有些困难。于是另一个方法是利用SDK生成新的Application时提供的Peripheral Test模板。

图 19

该模板生成的代码中,在主函数中找到相应外设的测试函数,例如本例中GPIO的测试函数“GpioOutputExample()”,再通过追述该函数的具体实现,可以一定程度上作为最基本的范例代码。

图 20

如果再进一步深入到ARM编程的本质,其实与硬件的所有控制和通信都是依靠读写底层的寄存器来完成的。例如如果查看一下“XGpio_SetDataDirection()”函数的底层实现,可以发现逐级调用的分别是“XGpio_WriteReg()”函数和“XGpio_Out32()”函数,而“XGpio_Out32()”调用的是“Xil_Out32()”。其实“Xil_Out32()”和“Xil_In32()”这两个函数分别是写读底层硬件寄存器的两个函数,所有的上层与底层的寄存器级别的通信,也就是绝大多数的外设控制,都是依靠这两个函数完成的。

审核编辑:汤梓红

-

Xilinx Zynq小试FPGA开发流程2023-03-14 3729

-

ZYNQ7020的PS端的基本开发流程2022-07-24 13097

-

ZYNQ 的启动流程介绍2022-07-22 10552

-

ZYNQ的启动流程2022-05-07 8591

-

典型的ZYNQ开发流程2022-02-08 9004

-

ZYNQ嵌入式系统的开发流程2021-10-27 1536

-

基于Zynq的嵌入式开发流程2021-08-23 1999

-

ZYNQ芯片开发流程的简介2021-01-26 3943

-

Zynq在非JTAG模式下的启动配置流程2021-01-08 2211

-

Zynq UltraScale+ MPSoC的ZCU102开发套件的开发流程2018-11-27 5707

-

Zynq开发流程的捷径SDSoC2018-07-02 2336

-

linux下开发基于zynq的嵌入式操作系统流程2018-03-15 985

-

ZYNQ学习 —— 启动流程分析及各环节文件生成流程(ZedBo2016-05-11 1164

全部0条评论

快来发表一下你的评论吧 !