请问在Cadence中钻孔重叠如何检查呢?

电子说

描述

使用Cadence Allegro进行PCB设计时,经常用到Subdrawing功能进行走线和孔的复用,Subdrawing的孔和线避免不了与原用的线和孔进行重叠。

线重叠比较容易解决,但孔重叠就比较麻烦。

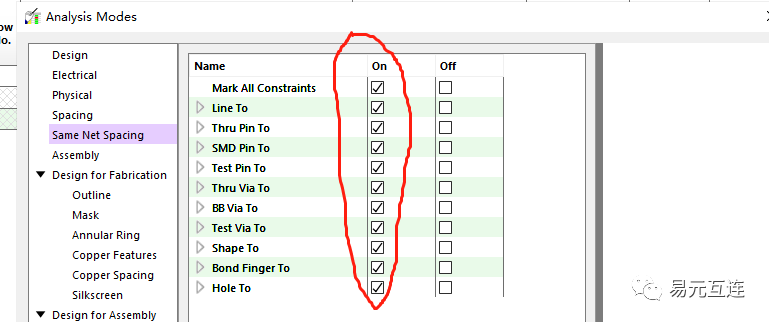

小易今天就碰到了这个麻烦,小易的规则是这样设置的,首先把Same Net Spacing的检查打开,如下图所示;

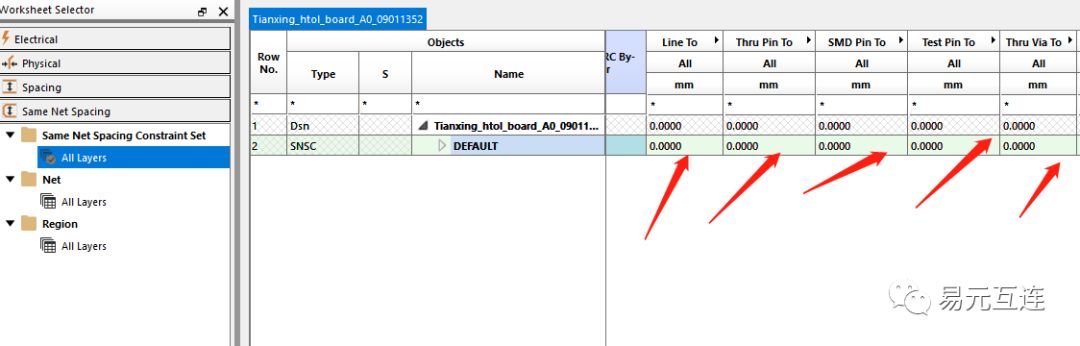

接着把Same Net Spacing的所有间距设置为0,如下图所示;

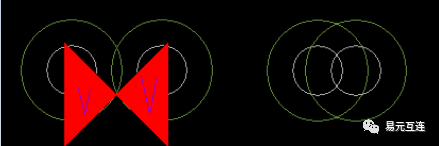

这样,同网络的VIA相交时,就会有DRC产生,如下左图所示;但如果两个VIA相交的更狠些,直到两个Hole相交后,如下右图所示,发现DRC就没有了,这个就很奇怪了。

究其原因,Allegro在15.2版本之前,没有做槽孔的功能,当时槽孔的做法就是把N个通孔通过Hole交叉叠加的方式来做出来的,如上右图,板厂会将两个Hole交叉的地方做成一个槽孔,这在Allegro的认知中,就认为这种做法是做成一个槽孔,所以就不会有DRC产生了。

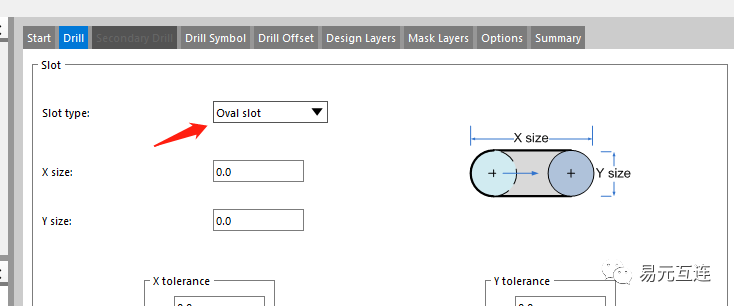

Cadencen Allegro发展到现在的2022版,已经不需要通过叠孔的方式来做槽孔了,如下图所示,专门有做槽孔的选项。钻孔重叠在PCB设计

中就不能允许存在了。但Cadence Allegro软件本身又无法查出这种Hole相交的叠孔,也不知道Cadence公司为什么不更新这个检测功能,有同仁知道的可以在文章后面帮忙发出来,在这里先谢了。

不过钻孔重叠对DFM来说,却是非常简单的一个事,下面就用华秋DFM软件来说明下检查的方法。

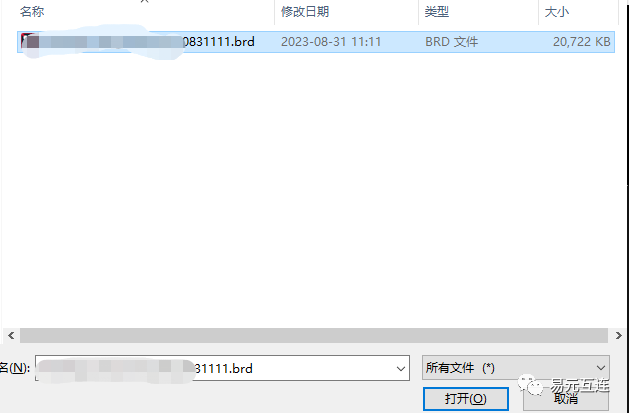

第一步,不用出GERBER资料,直接硬干,打开PCB文件,就是这么强大;华秋DFM可以直接打开PCB文件,不需要每次都要繁琐的反复出GERBER文件或ODB++文件;

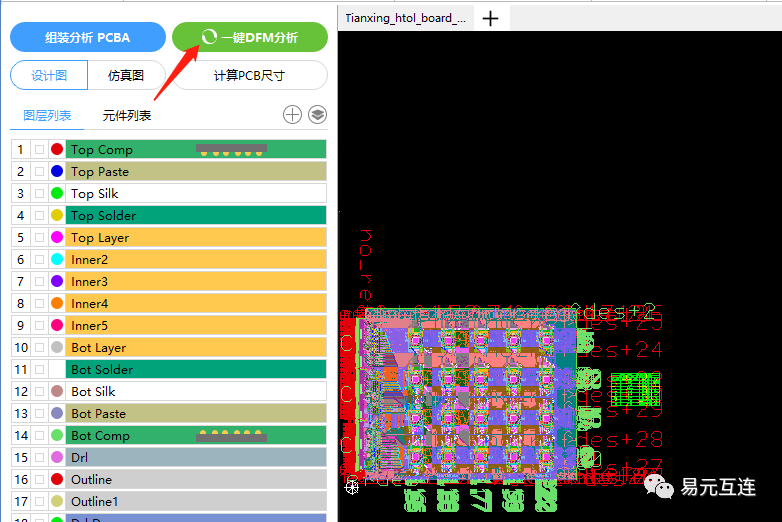

第二步,打开PCB文件后,直接点击“一键DFM分析”按钮,如下图所示;

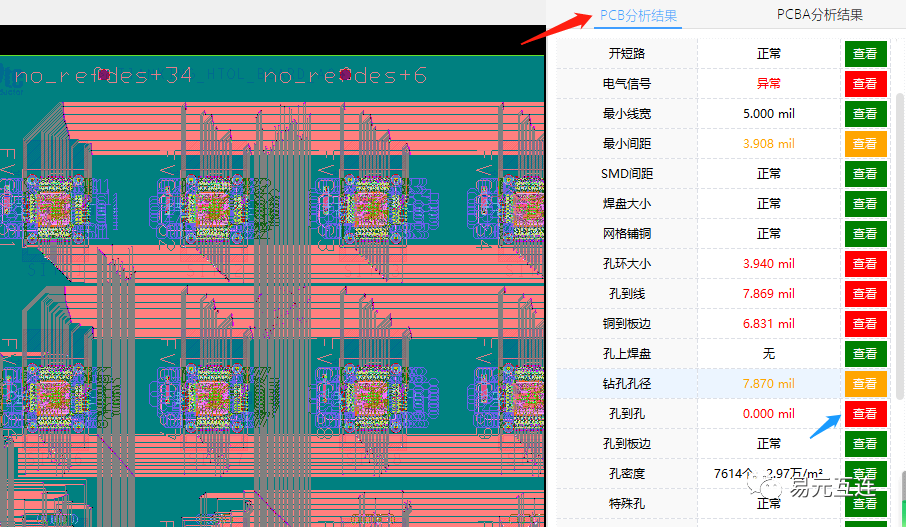

第三步,PCB的分析结果出现在右侧,如下图所示,孔到孔的间距出现红色,间距0mil;

第四步,点击右侧红色“查看”按钮,就出现了一个检查孔到孔的对话,点击右侧分析结果,会自动跳到相应的孔重叠的地方,如下图所示;

第五步,根据检查的结果,在PCB里进行更改,删除多余的重叠孔。

-

请问,在LAYOUT中可以钻孔,但是转到ROUTER之后,却不能钻孔2012-11-22 3159

-

在板钻孔怎么还是显示底层呢2014-12-26 3430

-

cadence 原理图检查工具2015-02-09 3656

-

allegro钻孔表数据重叠怎么办??2015-12-22 12543

-

cadence Orcad软件怎么去检查单端网络呢?2018-11-13 18427

-

CAD软件中如何删除重叠线?2019-07-07 1844

-

请问怎么在Altium中则呢么输出钻孔符号?2019-07-09 3657

-

如何在Altium中设置让软便不检查丝印和焊盘重叠?2019-09-10 4115

-

为什么安装ASSURA却无法在Cadence的菜单中显示?2021-06-22 2591

-

请问在Cadence中如何测量MOS电容的伏容特性曲线?2021-06-24 3847

-

在玻璃上钻孔的技巧2009-09-10 2703

-

cadence allegro自动生成钻孔2018-04-14 3145

-

基于Cadence软件DRACULA工具的LVS检查2021-09-18 1474

-

基于Cadence软件DRACULA工具的DRC检查2021-09-27 1601

-

如何在Cadence Allegro软件中制作槽孔焊盘2023-10-21 4618

全部0条评论

快来发表一下你的评论吧 !