NOR Flash的技术体系和结构特点

存储技术

描述

本文分析了NOR Flash的技术体系,结构特点,并对实现数据存储的基本原理以及发展趋势进行介绍。

目前,NOR Flash有两大技术体系:

ETOX,即Floating Gate(浮栅)技术

基于SONOS结构的MirrorBit技术

01两大技术体系的差异比较

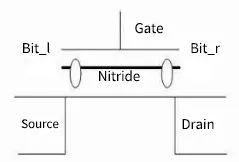

SONOS结构简图

结构特点

SONOS就是将浮栅用氮化物取代,形成氧化物-氮化物-氧化物(Oxide-Nitride-Oxide)结构,其利用氮化物的特性将电荷固定在注入点附件,它不像浮栅那样随机分布在多晶上,因此可以在两端分别聚集电荷,使一个单元可以实现2比特的存储。

主流的NOR Flash目前多采用Floating Gate,相对熟悉,结构不再详述。

Floating Gate

MirrorBit

排列方式

因其结构的差异,两者存储单元排列方式也不一样。

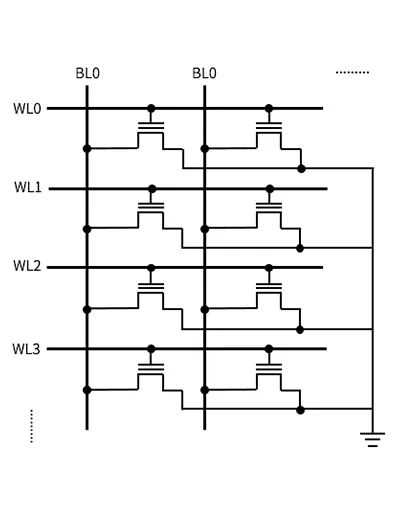

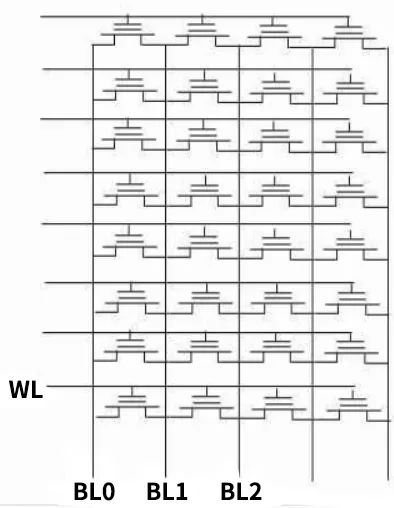

Floating Gate将存储单元进行并联,word line连到一行存储单元的control gate上,源端和漏端分别连到bit line和GND。

SONOS结构的连接其是将同一word line上的各存储单元源端和漏端首尾相连,不同word line,同一bit line上的存储单元的源端和漏端分别连在一起。

基本原理以Floating Gate的为例简图

基本原理

两种技术的数据存储及读取的基本原理大致相同。

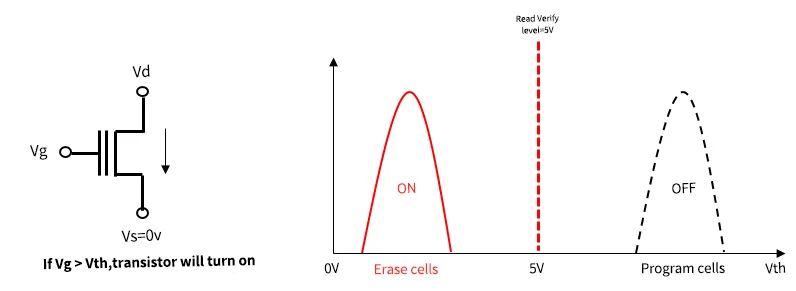

读取时在control gate端加上一定的电压Vread,通过判断bit line上的电流大小来决定存储的信息。电流大小取决于Vread与所读取存储比特Vth的比较,所以擦与写操作就是在不同级上加不同的电压,利用FN隧穿效应或热电子注入等引起自由电子的数量变化,从而改变Vth值。

发展趋势

基于SONOS的MirrorBit技术实现一个单元2比特的存储,在提高存储单元密度的同时,也会带来一些副作用,比如在访问时,两个比特会相互干扰;更多的源/漏端的bit line连接,引起更多的读干扰。所以如何做到更多的cycling及更长的data retention,是一个难点。

由于SONOS的电荷捕获方式更不容易产生缺陷产品,对制造工艺要求相对简单,比较有成本优势,还可演进MirrorBit技术使每个单元存储4比特,进一步提高单元密度。对抗干扰或耐久性方面,可研发一些新的设计,比如在两个存储位中间再加一个控制极,将存储位严格地区分开,使读写操作更为精确,但这也可能会带来负载较大等副作用需要克服。

Floating Gate技术的发展,主要通过工艺制程更新来降低成本,但先进的工艺也会加大数据访问时的各种干扰,这对产品稳定性以及耐久性也提出了挑战,所以高可靠性是其发展的一个方向。

此外,随着新应用场景的涌现,对产品有着不同新需求,比如穿戴设备对低功耗,快速启动设备对高速率等,因此产品的多样化发展也是其趋势。

02东芯半导体NOR Flash 产品系列

| 产品规格 | |

| 电压/Voltage | 1.8V/3.3V |

| 温度/Temperature | -40℃-85℃/105℃/125℃ |

| 容量/Density |

64Mb/128Mb/256Mb/ 512Mb/1Gb |

| 封装/Package |

SOP,WSON,USON, VSOP,WLCSP |

| 速度/Speed | 104MHz/133MHz |

| 线宽/Bus Width | x1/x2/x4 |

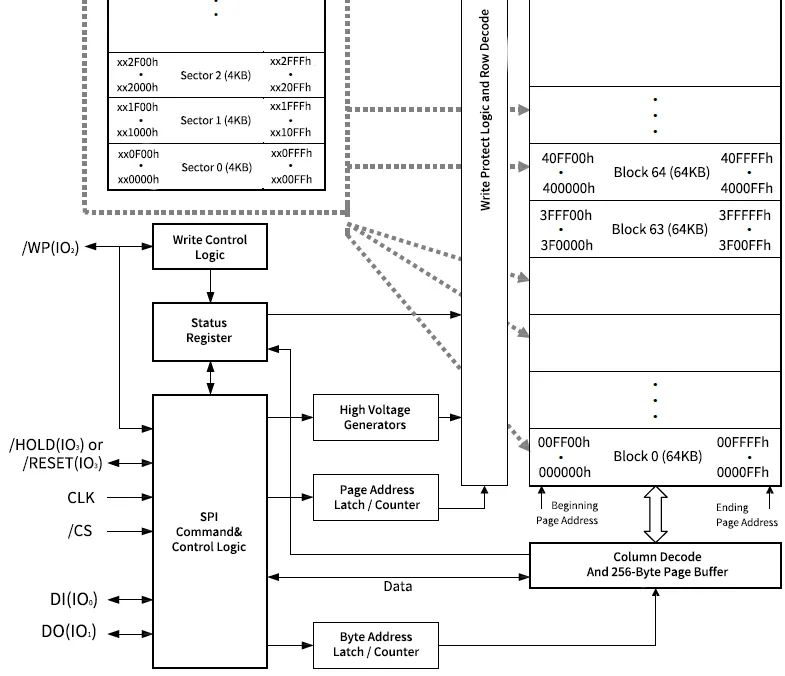

东芯的SPI NOR Flash产品系列基于Floating Gate技术

从65nm开始,到55nm,48nm不断演进,

支持Single/Dual/Quad SPI和QPI四种指令模式、

DTR传输模式和多种封装方式。

聚焦高附加值产品,已有产品通过AEC-Q100测试。

广泛应用于网络通讯,安防监控,消费电子以及移动/

工业互联网中的各种电子产品。

Block框图

新品推出

近期我们将推出新一代1.8V 64Mb,3.3V 128Mb的SPI NOR Flash,在功耗,速率等方面上较上一代产品更具优势。

其主要是通过架构上对模块精确划分,区分了读数据模块,写数据模块以及其他控制模块,控制逻辑依照模式来开启或者关闭相对应的电路模块;对时钟和数据路径级数进行了优化,减少不必要的信号翻转;物理实现上采用人工布局布线,缩短了时钟以及数据路径的走线,都大大降低了系统功耗。

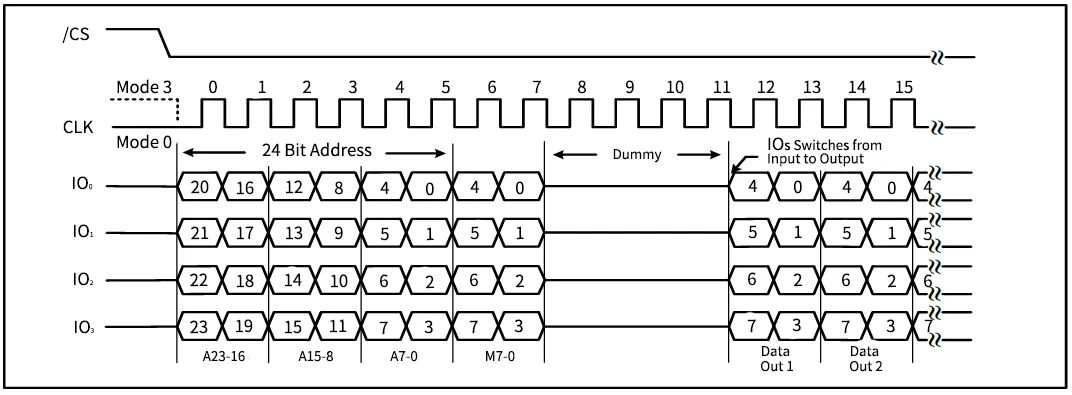

XIP功能消除了重复命令所用的8个周期,使用带有随机地址的同一命令执行连续操作。此功能启用后,当前读命令将在下一次操作中重复,如果当前操作是多I/O读命令,将保持多I/O读取模式,下一次读取操作只需提供新地址。此外,可调的读操作空指令周期为客户提供更灵活的配置,使达到系统效率最大化,提高了访问速度。

Fast Read Quad I/O Instruction

(Previous instruction set M5-4 = 10,

enable continuous read)

东芯,为日益发展的存储需求提供高效可靠的解决方案。

关于东芯

东芯半导体以卓越的MEMORY设计技术,专业的技术服务实力,通过国内外技术引进和合作,致力打造成为中国本土优秀的具有自主知识产权的存储芯片设计公司。

审核编辑:汤梓红

-

从NOR Flash 到 NAND Flash 和SD NAND,从底层结构到应用差异2026-03-05 375

-

NOR FLASH的结构和特性及原理图2024-02-19 8462

-

Nor Flash的基本概念 Nor Flash的内部结构解析2023-12-05 5527

-

为什么Nor Flash可以实现XIP,而Nand flash就不行呢?2023-10-29 2497

-

NAND FLASH与NOR FLASH的技术对比2023-10-01 3733

-

什么是串行Nor Flash?串行Nor Flash的结构和参数特性2023-09-05 6523

-

串行Nor Flash的结构和参数特性(1)2023-08-11 5113

-

NOR FLASH和NAND FLASH基本结构和特点介绍2023-06-29 4499

-

关于NOR Flash的几大应用领域浅析2021-03-23 16203

-

非易失性存储器-Nor Flash的特点都有哪些2020-12-07 4606

-

SPI FLASH与NOR FLASH的区别 详解SPI FLASH与NOR FLASH的不一样2018-09-18 56114

-

NOR FLASH的原理及应用2017-10-15 3506

-

旺宏串行NOR Flash简介2010-03-10 1163

全部0条评论

快来发表一下你的评论吧 !