UltraEM中NTN Layer和PGS对Q值影响的研究

描述

1 介绍

此仿真实例用UltraEM来研究接地屏蔽层(PGS)以及NTN层的改变对器件Q值造成的影响。

PGS和NTN对器件起到的作用都是提高Q值。PGS是接地屏蔽层,其上结构与电感线圈垂直,通过减少金属层与地板之间的耦合起到屏蔽作用;加NTN则会将工艺衬底的掺杂硅换成导电率更低的本征硅,减小了介质损耗角正切,从而降低了能量的损失,起到屏蔽的作用。

本次测试使用的三个实例分别是:

1. CMOS工艺的对称螺旋电感;

2. 在1的基础上添加一个接地屏蔽层;

3. 在1的基础上更改衬底材料为本征硅。

将三个实例放入UltraEM仿真并对比其Q值变化。

2 仿真操作流程

2.1建立仿真算例

2.1.1 新建工程

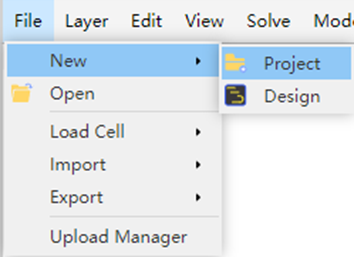

依次点击File > New > Project新建工程,如下图 2-1。

图2-1 新建工程 2.1.2 导入设计文件

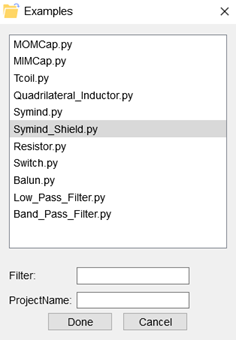

这里使用示例Examples中采用到接地屏蔽层的Symind_Shield.py工程。

图2‑2 导入设计文件

2.1.3 PGS测试算例

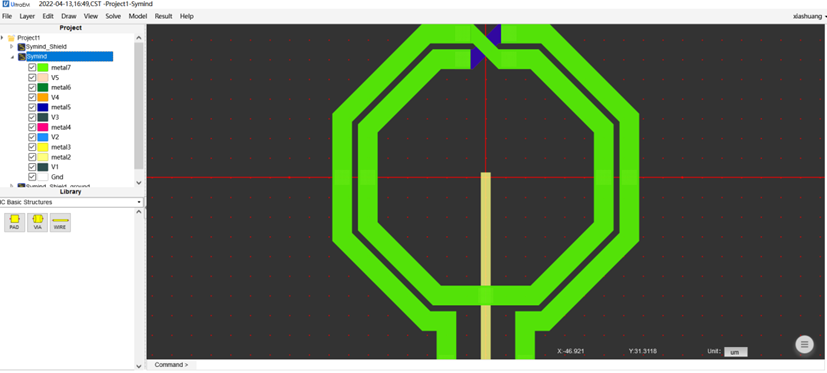

建立两个螺旋电感算例,一个不含PGS,一个含PGS,如图 2-3,图 2-4。

图2‑3 无屏蔽层

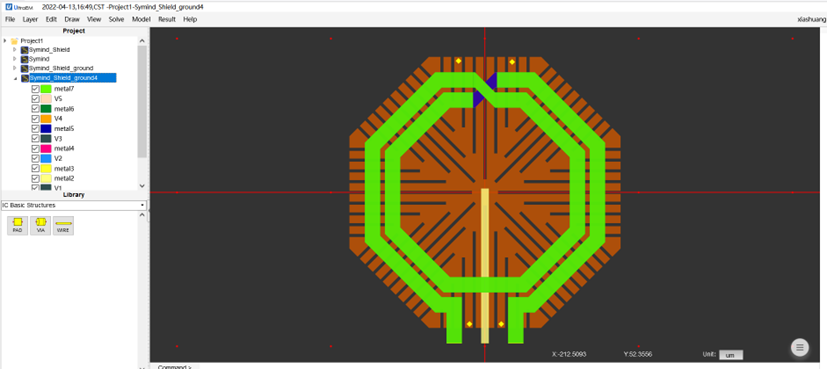

图2‑4 接地屏蔽层 2.1.4 NTN层测试算例

图2‑4 接地屏蔽层 2.1.4 NTN层测试算例

建立两个螺旋电感算例,一个使用掺杂硅衬底,一个使用本征硅衬底。

修改衬底材料参数可按如下方式操作:

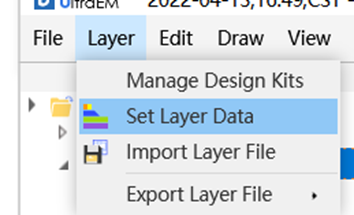

依次点击Layer > Set Layer Data打开器件的层数据,如下图2-5。

图2‑5 查看层数据

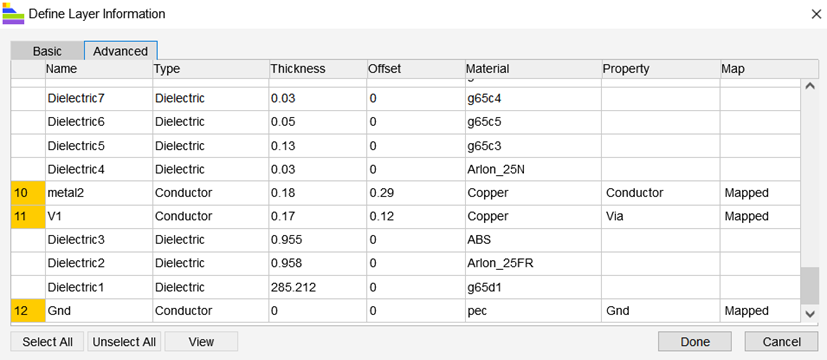

打开层数据之后,找到底部衬底层,如下图2-6。

图2‑6 查看衬底

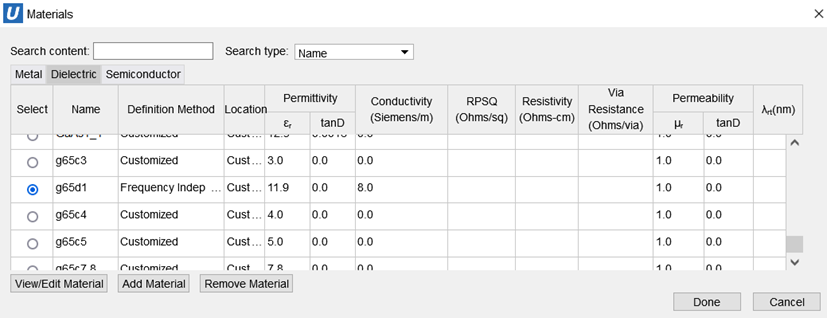

点击Dielectric1层所用材料g65d1,即可查看该材料的信息,如下图2-7。

图2‑7 衬底材料

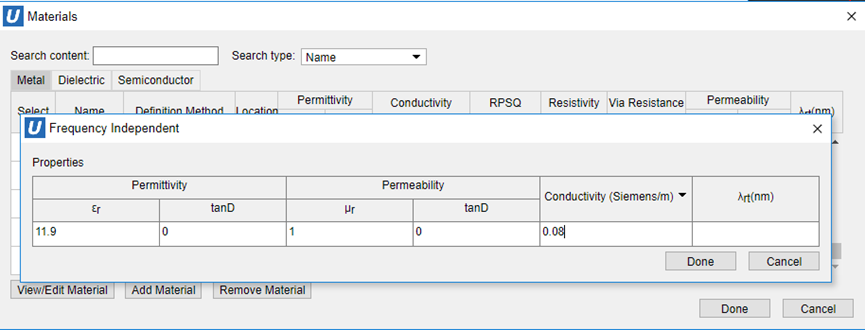

此处使用材料为掺杂硅,电导率为8.0 S/m。为对比NTN layer造成的影响,我们重新定义一个本征硅,电导率设置为0.08 S/m。点击Add Material新建材料,如下图2-8。  图2-8 新建材料

图2-8 新建材料

2.2 自定义参数

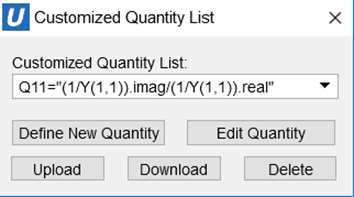

自定义参数Q值的查看需要预先定义公式,通过Result > Define Quantities建立一个新的公式,如下图2-9。

图2‑9 定义Q参数

通过Define New Quantity,设置参数名及计算公式。

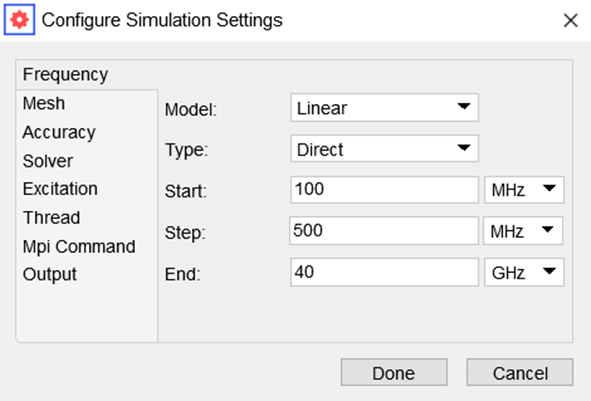

2.3 定义测试频率

通过Solve > Settings进入频率设置页面,在Frequency中设置仿真的起始频率、步长以及截止频率。

图2-10 设置仿真频率

图2-10 设置仿真频率

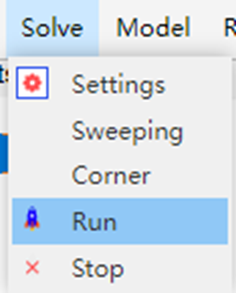

2.4 开始仿真

完成频率设置后,点击Solve > Run以运行仿真,如下图2-11。

图2-11 开始仿真

图2-11 开始仿真

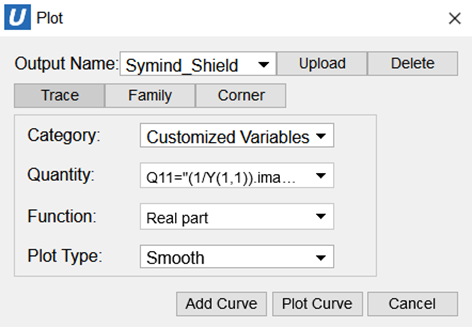

2.5 查看结果

以上三个算例仿真完成后,单击Result > Model Data,查看仿真结果。选择Q11计算公式,查看其Real part。

图2-12 绘图

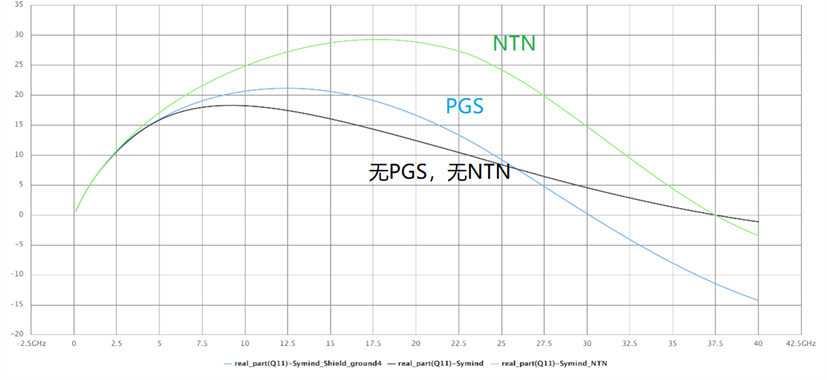

图2-13 Q 值对比

Q值曲线由高到低依次是:添加NTN层的电感、添加PGS的电感、无NTN无PGS的电感。

从仿真结果来看,在频率较低的频段,三者几乎重合,Q值区别很小,频率较高时,三者差异逐步增加。

明显可以发现有PGS的电感Q值要比没有的高许多,使用本征硅的电感也明显提高了Q。

此结果基本与理论相符,不论是接地屏蔽层还是减小衬底导电率,两者都是减小了器件的损耗进而提高了Q值。

法动科技:

成立于2017年。作为拥有硅谷及斯坦福创新基因的国际一流团队,我们专业提供射频微波电子设计自动化(EDA)软件,凭借自主研发的大容量、快速三维全波电磁仿真引擎和基于人工智能技术的高效系统级仿真引擎,能够在射频微波芯片、封装、高速PCB等领域为用户提供快速准确的电磁仿真、建模及优化设计方案。

同时,我们可以为包括移动通信、物联网、5G、雷达、卫星通信系统和高速数字设计在内的产品提供高水平设计开发服务。

审核编辑:汤梓红

-

如何在ADS Momentum中使用PGS模拟电感器2018-10-11 3560

-

layer是什么?解析ad9中的plane与layer2019-10-16 9722

-

UltraEM®的Corner Sweep仿真实例2023-06-19 2023

-

UltraEM和EMCompiler对变压器进行阻抗匹配的仿真实例2023-07-19 2429

-

基于NTN实现卫星语音通信的关键技术2024-04-29 1418

全部0条评论

快来发表一下你的评论吧 !