英特尔发布全球首款基于UCIe连接的Chiplet(小芯片)处理器

处理器/DSP

描述

英特尔CEO帕特·基辛格:英特尔正在开创人工智能电脑的新时代。

英特尔CEO帕特·基辛格(Pat Gelsinger)在Innovation 2023大会上展示了全球首款基于UCIe连接的Chiplet(小芯片)处理器,该芯片采用Intel 3工艺节点上制造的Intel UCIe IP芯片,与在台积电N3E节点上制造的Synopsys UCIe IP芯片配对。两个Chiplet通过英特尔的EMIB接口进行通信。

通用Chiplet Interconnect Express(UCIe)接口得到了众多行业巨头的支持,例如英特尔、AMD、Arm、英伟达、台积电和三星以及其他120家公司。该互连设计旨在通过开源设计标准化Chiplet之间的芯片间互连,从而降低成本并培育更广泛的经过验证的Chiplet生态系统。

当今的多Chiplet封装使用专有接口和协议相互通信,这使得广泛采用第三方Chiplet成为一项艰巨的任务。UCIe的目标是创建一个具有标准化接口的生态系统,以便有一天芯片制造商能够简单地从其他设计人员那里选择Chiplet,并以最少的设计和验证工作将它们融入到新设计中。

UCIe联盟于2022年成立,已经获得了芯片制造行业的广泛支持。联盟已经相继推出了UCIe 1.0、1.1规范。该联盟制定了非常激进的性能和面积目标,将目标市场分为两个广泛的范围,采用标准2D封装技术和更先进的2.5D技术(EMIB、CoWoS等)。先进的封装选项可提供更高的带宽和密度。

英特尔基于Chiplet的处理器,如Sapphire Rapids和新发布的Meteor Lake,目前使用专有接口和协议进行Chiplet之间的通信,但英特尔已宣布将在其下一代Arrow Lake消费级处理器之后使用UCIe接口。AMD和英伟达也在致力于自己的计划,但还没有展示可用的硅芯片。

作为一家长期领先的半导体企业,以CPU而闻名天下的厂商,英特尔在处理器方面的进展尤其值得关注。在本次大会上,英特尔也的确带来了全面的展示,英特尔的PC芯片从此也开始全面进入AI时代。

基辛格表示:“人工智能将从根本上改变、重塑和重构 PC 体验,通过云和 PC 协同工作的力量释放个人生产力和创造力。为此,英特尔正在开创人工智能电脑的新时代。”代号为Meteor Lake的Intel Core Ultra处理器,正是英特尔实现上述目标的一个重要倚仗。

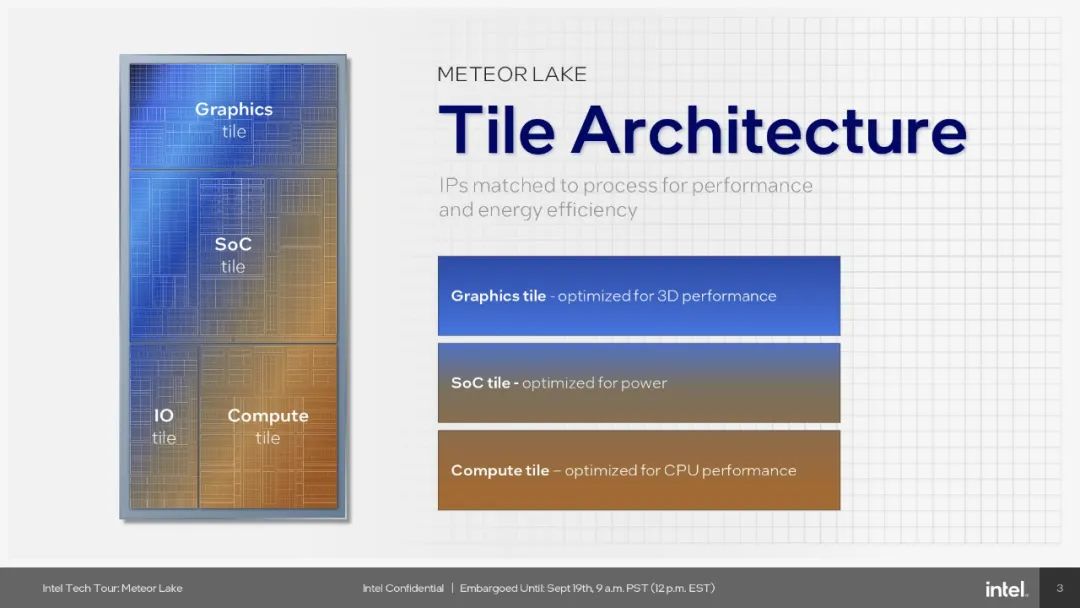

在英特尔看来,Core Ultra 代表了英特尔客户端处理器路线图的一个转折点,因为它是第一个由 Foveros 封装技术(英特尔的3D封装技术)支持的客户端Chiplet设计,还采用了 EUV 光刻技术。从设计上看,芯片内部包含了computing tile、graphics tile和SoC tile和I/O tile四个部分。其中,computing tile是基于Intel 4工艺打造,graphics tile是基于台积电的5nm打造,SoC tile则采用台积电的6nm打造,这正是Chiplet精神的体现。值得一提的是,这个芯片的Soc tile上还集成了英特尔首个NPU。

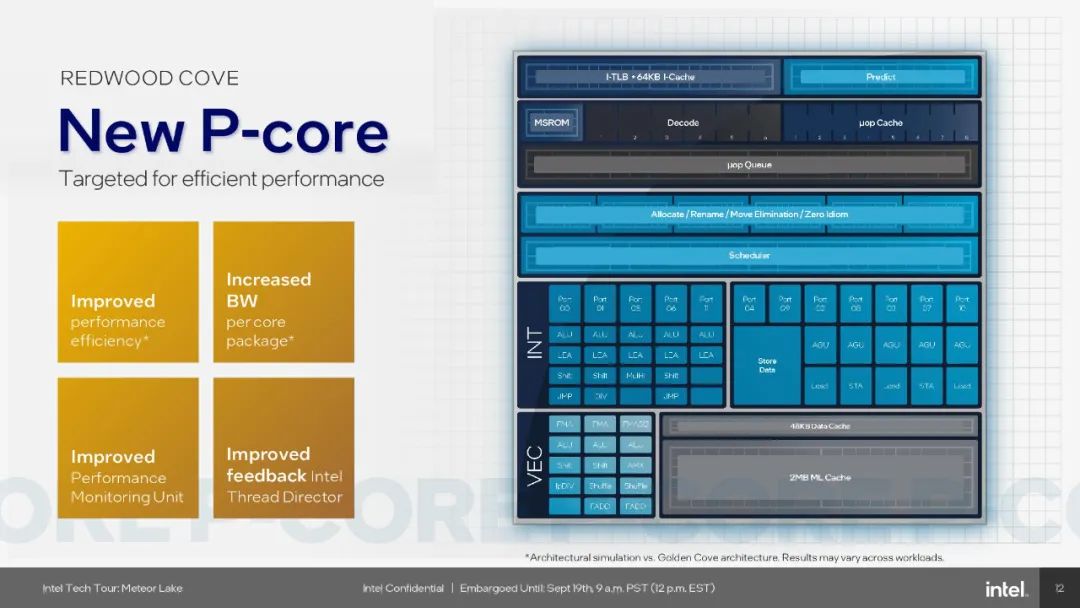

具体到芯片设计细节上。据透露,该芯片的couputing tile中有一对新的核心,一个名为 Redwood Cove 的 P 核心和一个名为 Crestmont 的新 E 核心。其中,新的 P 核心是英特尔第 12 代核心 (Raptor Lake) 处理器中之前的 Golden Cove 核心的直接继承者,通过新的 Redwood Cove 核心,英特尔在芯处理器上带来了不小的 IPC 提升。

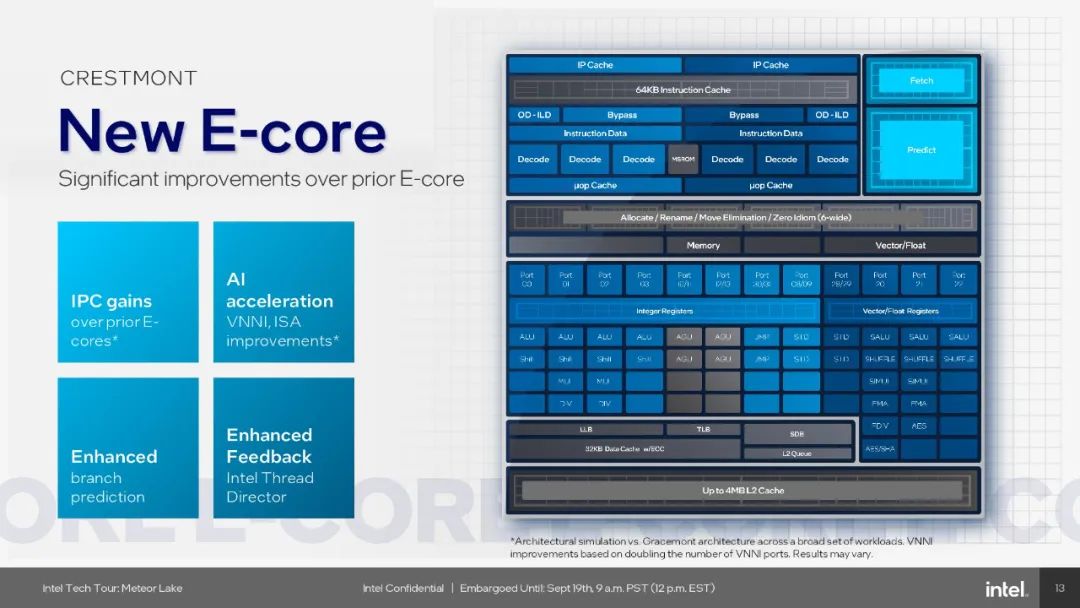

至于E核心,据报道,通过矢量神经网络指令 (VNNI) ,该核心保持基于 CPU 的 AI 加速。而与 P-Core 一样,E-Core 也受益于增强的 Thread Director 反馈,它提供了更好的粒度控制和优化。

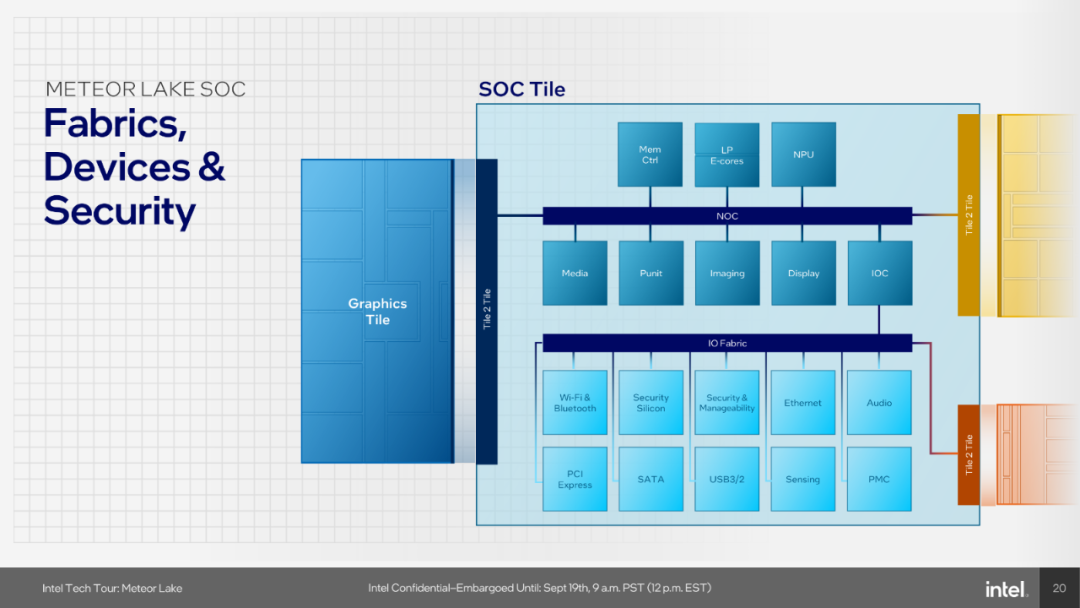

来到SoC tiles上,据介绍,通过在硅片上实施片上网络 (NOC),英特尔摆脱了网状路由的旧有限制。这不仅仅是为了让数据通道更快,而是旨在实现对内存的更智能、更节能的访问。在利用 EMIB 和 2D 缩放后,数据路径会短得多,从而减少功耗,但较短的电线也有助于减少总体延迟损失。

如前面所说,在这个SoC tile上,还有一个全功能神经处理单元 (NPU),这是英特尔面向客户端处理器的首个NPU,得益于这个模块,英特尔能够直接将 AI 功能引入到客户端芯片上,且因为其与 OpenVINO 等标准化程序接口兼容,这就使得在开发的时候能够给相关人员带来便利。据介绍,这个NPU由两个神经计算引擎组成,它们可以协作完成单个任务,也可以独立运行。而这些神经计算引擎的则主要包括了两个组件:推理pipeline和 SHAVE DSP。

编辑:黄飞

-

台积电、英特尔携手推出全球首款小芯片互联2023-09-22 1428

-

英特尔展示全球首款基于UCIe连接的Chiplet CPU2023-09-20 1891

-

凌华科技发布两款基于最新的英特尔® 酷睿™处理器的模块化电脑2023-02-15 969

-

苹果Mac弃用英特尔芯片的原因2020-06-23 5325

-

英特尔凌动处理器CE4100有什么优点?2019-09-03 3599

-

英特尔的十款嵌入式智能处理器2019-07-29 4070

-

英特尔16款全新45nm处理器2018-12-03 2644

-

英特尔处理器命名规则介绍_英特尔处理器种类_英特尔处理器排名2017-12-15 25058

-

摩托罗拉首款英特尔处理器手机MT788发布2012-11-20 2969

-

英特尔惠普联合发布新一代安腾处理器2012-11-09 2600

-

英特尔将在2014年推出14纳米处理器芯片2011-12-05 3732

-

英特尔发布基于凌动处理器的系统芯片计划2010-04-15 764

-

英特尔发布首款六核台式机处理器2010-03-12 956

全部0条评论

快来发表一下你的评论吧 !