求一种基于FPGA时间数字转换(TDC)设计方案

可编程逻辑

描述

一、TDC计时技术

时间数字转换(Time-to-Digital Converter,TDC)是一种用来测量时间的电路,它将连续的时间信号转换为数字信号,从而实现时间测量的数字化。精密时间间隔测量技术、测量精度通常为亚纳秒级,广泛应用于激光测距、成像、卫星导航、高能物理实验以及医学成像等领域。

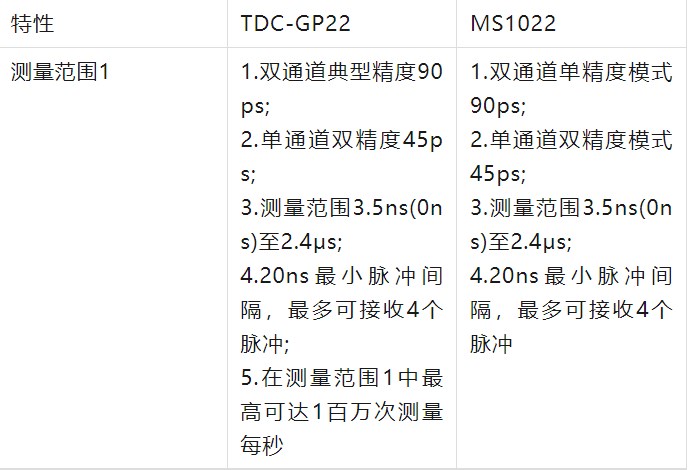

常用的TDC计时方法可以在专用集成电路(Application Specific Integrated Circuit,ASIC)中实现,比如德国ACAM公司推出的TDC-GPX系列,同时国内瑞盟科技也推出以其性能一样的TDC测量芯片MS1022。表1比较了TDC-GP22和MS1022的测量范围特性,可以看出基本一样,因此此两款芯片在低成本测量领域有着广泛的运用。

表1 TDC-GP22和MS1022特性

二、基于FPGA的时钟相移TDC计时原理

常见的基于FPGA开发TDC计时技术有直接计数法,多相位时钟采样法,抽头延迟线法等等。在本次讲解中,主要讲解基于多相位的时间数字转换技术,后期也会推出多种基于抽头延迟线法的开发例子。

采用多相位时钟采样法(MPCS),通过多相位时钟插值,虽然无法达到基于抽头延迟线法那种结构的皮秒级高精度,但也能设计出156ps左右的分辨率。这种实现方法更为稳定、资源占用更少,测量范围更大,适用于对精度要求不是特别高的测距、成像系统中。

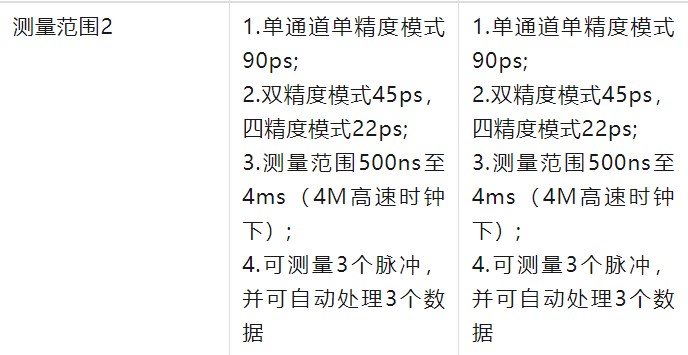

图1为多相位时钟采样结构示意图,其基本工作原理是把单个参考时钟的直接计数法转化为采用多路固定相移时钟对时间间隔进行量化测量。

图1 多相位时钟采样结构示意图

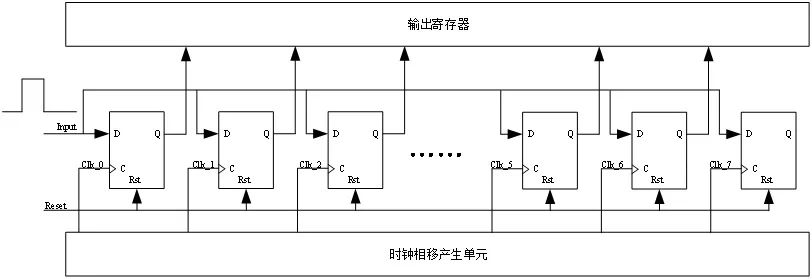

图2为基于8相位时钟采样示意图,时钟信号经过数字移相后输出8路频率相同,相位依次相差(这里n=8)的多路时钟信号,等效于将每一个Clock周期时钟n(这里n=8)次切片量化。

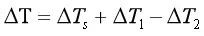

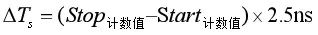

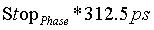

当选择的n值越大,即对每个Clock时钟周期划分的越精细,分辨率越高,在这里相当于将Clock频率提高了8倍。假设系统主时钟为400Mhz(2.5ns),其测量分辨率变为2.5ns/8=312.5ps。其计算公式如式1所示。

图2 基于8相位TDC计时设计

图2 基于8相位TDC计时设计

(1)

(1)

其中, ,

, 为Start信号与时钟Clk_0上升沿之间时间差=

为Start信号与时钟Clk_0上升沿之间时间差= ,

, 为Start信号与时钟Clk_0上升沿之间时间差=

为Start信号与时钟Clk_0上升沿之间时间差= 。

。

图3为8相位时钟采样时序等效图,可以计算出Start和Stop的相位差。在输入信号上升沿来之前输出都为“0”,但在相移时钟在到之间输入信号由“0”~“1”电平跳变,对应相移时钟采样输出为高电平“1”。

输出寄存器组每8位一组,可以看出依次为:00000000,00000111,11111111,只要找到“0”~“1”电平跳变点即可得到当前输入信号上升沿与最临近的Clock上升沿的时间间隔,就能计算Start和Stop信号的相位差,从而根据公式1算出时间差。

图3 8相位时钟采样时序等效原理图

在时间间隔测量过程中,外部异步输入时间间隔信号与板载基准时钟信号存在着不同时钟域问题,即存在亚稳态现象。在只有一路时钟信号对其进行测量时,待测时间间隔信号需要利用计数时钟信号进行同步处理。

而采用MPCS的TDC电路,待测时间间隔信号被多路相位时钟信号量化,不需要考虑输入信号与时钟之间的相位位置,多相位时钟存在一定的相位约束关系,其相位差值恒定不变,通过循环相移时钟即可精确量化输入时间间隔信号,但亚稳态产生概率更高,不可忽视。

-

TDC7200:高精度时间数字转换器的深度剖析与应用指南2026-02-25 392

-

聊聊FPGA中的TDC原理2025-09-02 2747

-

TDC7200 适用于激光雷达飞行时间、磁致伸缩和流量计应用的时间数字转换器数据表2024-08-13 802

-

求一种数字式温度测量电路的设计方案2021-05-17 2481

-

求一种基于FPGA的永磁同步电机控制器的设计方案2021-05-08 1850

-

求一种基于FPGA高精度时间数字转换电路的设计方法2021-05-07 2184

-

求一种嵌入式PLC微处理器的设计方案2021-05-06 1873

-

求一种基于FPGA的HDLC协议控制器设计方案2021-04-30 1983

-

求一种多路模拟数字采集与处理系统的设计方案2021-04-28 1832

-

时间数字转换器TDC的工作原理是什么?有哪些应用?2021-04-12 19901

-

一种使用增益校准技术的_时间数字转换器2017-01-07 779

-

基于FPGA的高精度时间数字转换方法研究2015-10-30 594

-

【FPGA干货分享五】基于FPGA的高精度时间数字转换电路2015-02-02 6566

全部0条评论

快来发表一下你的评论吧 !