CAN总线是如何完成信号同步的?

接口/总线/驱动

描述

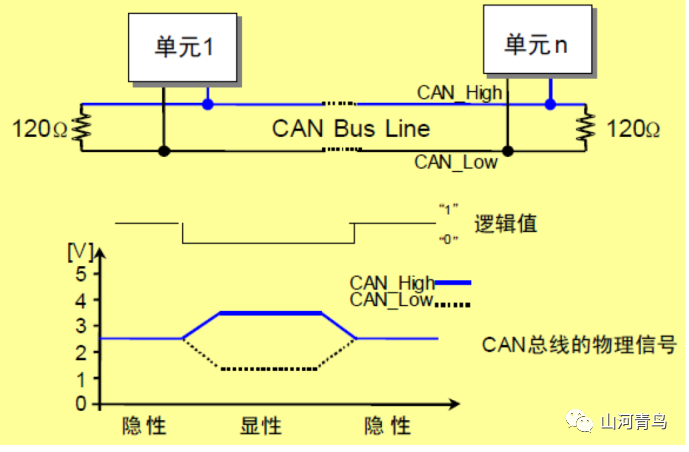

CAN 控制器根据两根线上的电位差来判断总线电平。总线电平分为显性电平和隐性电平,二者必居其一。发送方通过使总线电平发生变化,将消息发送给接收方。

显性电平对应逻辑 0,CAN_H 和 CAN_L 之差为 2.5V 左右。而隐性电平对应逻辑 1,CAN_H 和 CAN_L 之差为 0V。隐形电平具有包容的意味,只有所有的单元都输出隐性电平,总线上才为隐性电平(显性电平比隐性电平更强)。

CAN总线是采用NRZ(Non-Return to Zero)方法进行通讯的,这种通信有一种不好的地方,就是各个位的开头或者结尾都没有附加同步信号。CAN总线在长距离运输中,由于发送单元和接收单元存在的时钟频率误差及传输路径上的相位延迟等,都会引起同步偏差。这就导致信息传输不稳定,信号质量有问题。所以发送单元和接受单元都采用了一些通讯同步的方法来使二者电平传输能达到同步。

同步有两种方式,一种是硬件同步,一种是再同步。在解释同步之前,先介绍下位时序。

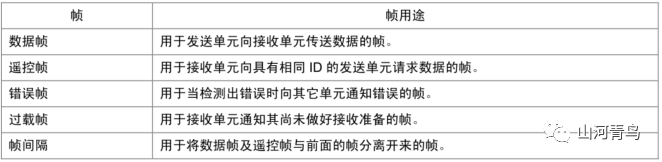

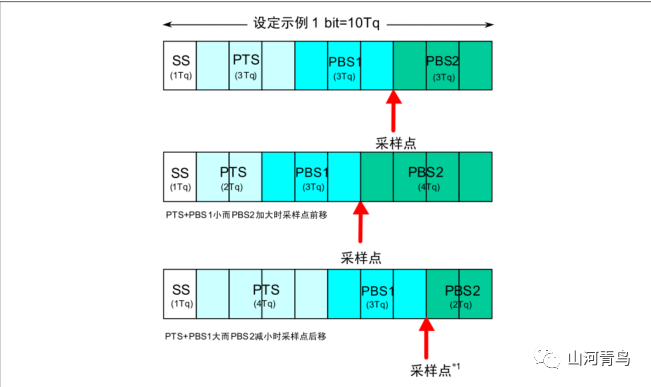

位时序--由发送单元在非同步的情况下发送的每秒钟的位数称为位速率。一个位可分为 4 段。

• 同步段(SS)

• 传播时间段(PTS)

• 相位缓冲段 1(PBS1)

• 相位缓冲段 2(PBS2)

这些段又由可称为 Time Quantum(以下称为 Tq)的最小时间单位构成。

1 位分为 4 个段,每个段又由若干个 Tq 构成,这称为位时序。

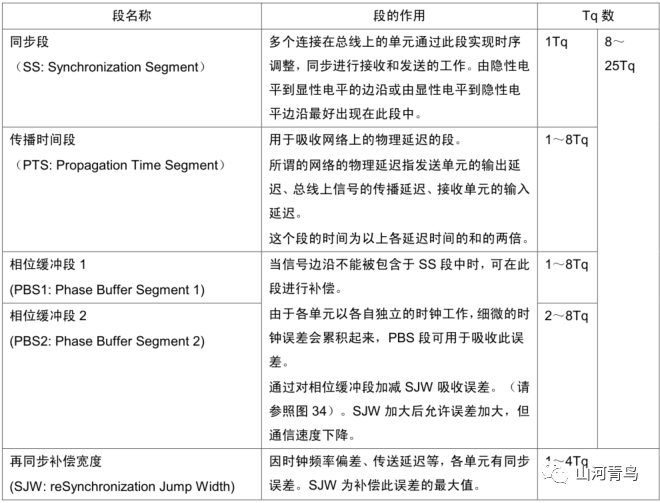

1 位由多少个 Tq 构成、每个段又由多少个 Tq 构成等,可以任意设定位时序。通过设定位时序,多个单元可同时采样,也可任意设定采样点。各段的作用和 Tq 数如下图:

一个位的构成如下:

看了上述位时序的介绍,我们再来看两种同步的方法。

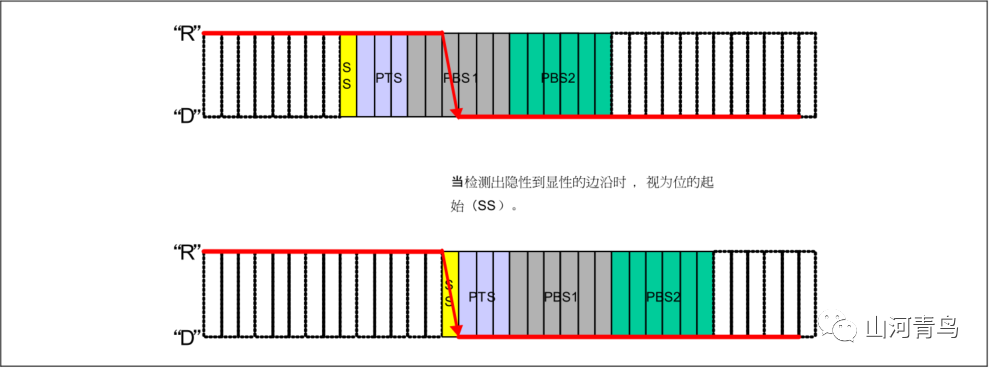

硬件同步

接收单元在总线空闲状态检测出帧起始时进行的同步调整,在检测出边沿的地方不考虑SJW的值而认为是SS段。硬件同步的过程如下图所示:

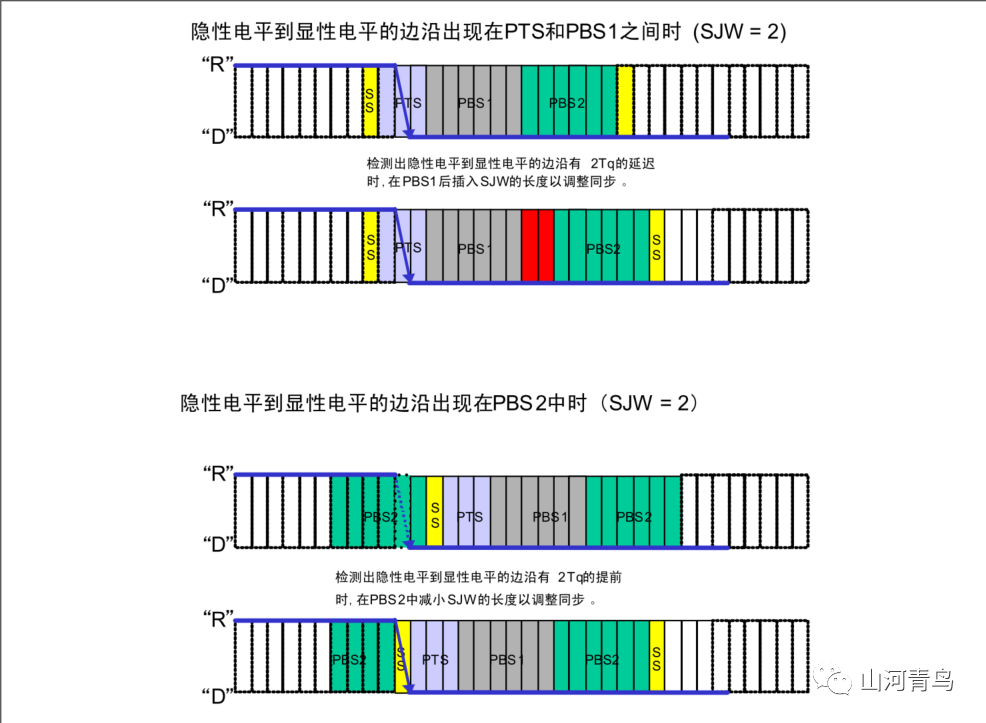

再同步

在接收过程中检测出总线上的电平变化时进行的同步调整。

每当检测出边沿时,根据 SJW 值通过加长 PBS1 段,或缩短 PBS2 段,以调整同步。但如果发生了超出 SJW值的误差时,最大调整量不能超过 SJW 值。

调整同步的规则

硬件同步和再同步遵从如下规则。

(1) 1 个位中只进行一次同步调整。

(2) 只有当上次采样点的总线值和边沿后的总线值不同时,该边沿才能用于调整同步。

(3) 在总线空闲且存在隐性电平到显性电平的边沿时,则一定要进行硬件同步。

(4) 在总线非空闲时检测到的隐性电平到显性电平的边沿如果满足条件

(1)和(2),将进行再同步。但还要满足下面条件。

(5) 发送单元观测到自身输出的显性电平有延迟时不进行再同步。

(6) 发送单元在帧起始到仲裁段有多个单元同时发送的情况下,对延迟边沿不进行再同步。

来源:山海青鸟

审核编辑:汤梓红

-

【CAN总线知识】CAN总线信号传输的位定时与位同步理论2024-07-17 2838

-

CAN总线的位定时与同步机制#汽车CAN总线北汇信息POLELINK 2023-07-17

-

CAN总线信号传输的位定时与位同步理论2016-08-15 2592

-

如何同步S32K118的can总线?2023-05-24 1344

-

详解CAN总线信号传输位定时与位同步2016-08-16 2457

-

什么是can总线?can总线是数字信号还是模拟信号2018-04-25 81563

-

CAN总线如何读取新能源汽车中的CAN信号2018-11-02 24351

-

基于CAN总线信号的波形解码和报文解码不一致的情况分析2019-11-11 3653

-

CAN总线信号传输位定时与位同步是如何实现的2020-03-21 3073

-

CAN总线的同步有何奥秘2020-12-26 2274

-

检验CAN总线信号2021-04-19 963

-

can总线干扰信号如何消除?2023-09-14 7259

-

怎么用示波器看can总线信号?2023-10-11 7024

-

基于ARM和CAN总线的电气信号采集节点的设计2023-10-13 449

-

车载时钟同步can_tsync实现原理2023-10-27 5029

全部0条评论

快来发表一下你的评论吧 !