运放参数解析:输入失调电压(Vos)

模拟技术

描述

今天继续给大家分享运放另一项指标——输入失调电压(Vos)。

(1)失调电压Vos定义

(2)各类运放失调电压范围

(3)失调电压产生原因

(3)运放失调电压修正方法

(4)失调电压补偿方法

在理想运放中Vos同样是不存在的,但实际应用中我们心里需要清楚真实运放与理想模型都存在哪些差异,这样才能设计出更优秀的电路。

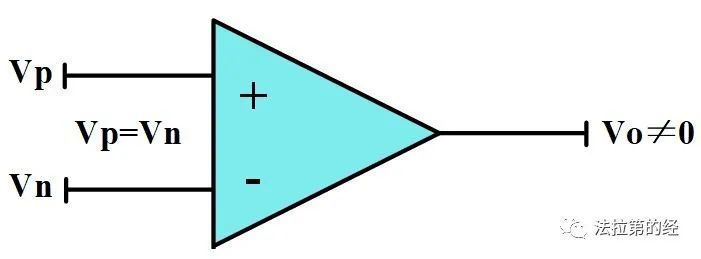

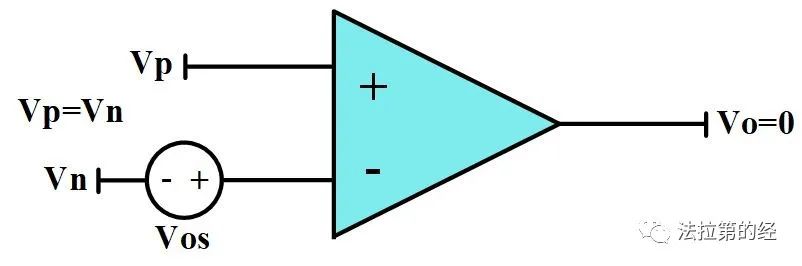

如下图1所示当运放处于开环状态时,若Vp=Vn时Vo应该等于0,这便是理想运放给我们结论,但是实际运放往往并非如此,Vos定义如下:如图2所示我们需要在反向端加入一个偏置电压源强制使Vo=0,当Vo=0时Vos的电压即为运放的输入失调电压,注意Vos可正可负。

图1 实际运放

图2 Vos定义

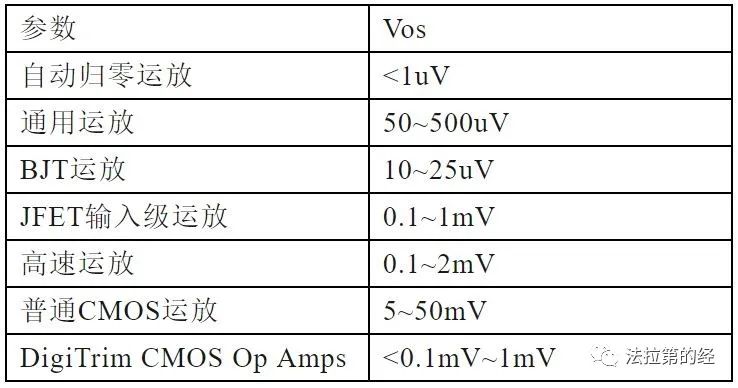

根据运放的类型Vos的范围跨越也比较大。自动归零运放的Vos通常小于1uV,通用运放Vos在50uV ~ 500uV,而高速运放和普通CMOS运放Vos分布范围达100uV ~ 50mV。具体见下表1所示。

表1 运放Vos对比

至此我们对Vos有了初步了解,那Vos存在的原因是什么呢?

原因主要归咎于运放的输入级电路。读过我那篇关于偏置电流文章的朋友都清楚运放的输入级采用差分结构,理想状态下当Vp=Vn时运放输出应该为0,但是在运放生产过程中不可能制作出性能参数绝对一致的差分对管,同时其它内部晶体管也存在生产误差,这些不可避免的因素造成理想的差分电路是不存在的,以上实际问题最终体现为Vp=Vn时Vo≠0,因此带来Vos这一参数。

那为什么BJT运放的Vos较普通CMOS运放的Vos小那么多?这是因为相对于CMOS的栅极一致性而言BJT的基极一致性要好很多,而一致性越好则Vos越小。

在精度要求较高的电路中,Vos引起的误差不容小视,针对这一问题解决方案可分为从运放内部校正Vos和从运放外部补偿Vos。首先介绍从运放内部改善Vos性能。

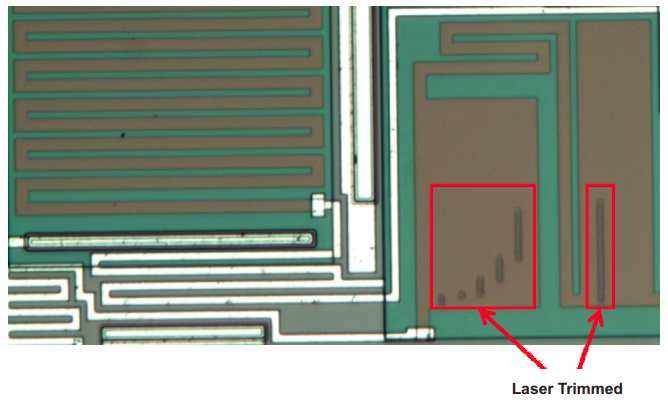

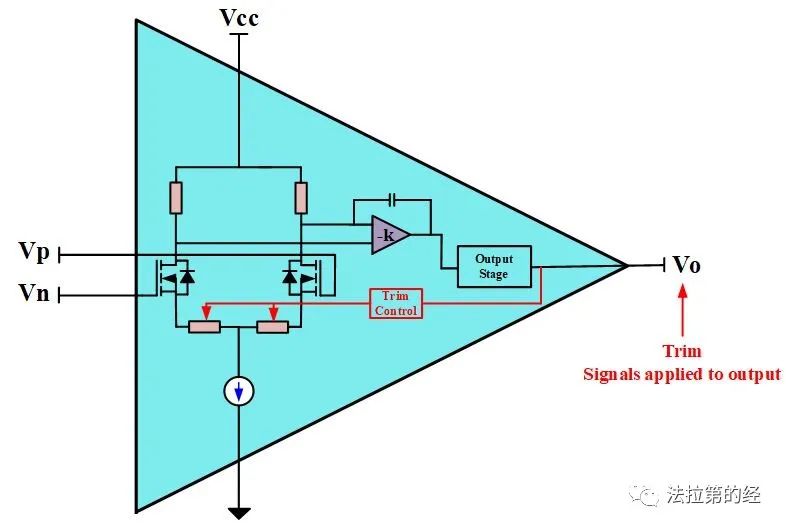

在运放生产过程中为了尽可能降低运放内部器件误差造成的失调电压,图3为TI公司采用激光对运放晶圆上的电阻进行微调从而达到Vos=0的目的,这一方法常常应用在BJT型运放的生产中。图4为另一种方法称为“e-Trim”,该方法是当运放处于封装阶段时对运放进行Vos校正,校正完成后内部的调整通路将被关闭以确保校正结果的可靠性。此外ADI针对CMOS运放也有相应的校正方法称为“DigiTrim”,当运放完成封装后通过数字控制方式对运放进行Vos校正,校正后的Vos不超过1mV。

图3 晶圆级校正Vos

图4 e-Trim校正

根据Vos定义,从运放外部补偿Vos非常容易理解。既然运放需要Vos那我们就给它提供这个Vos从而保证当Vp=Vn时Vo=0。

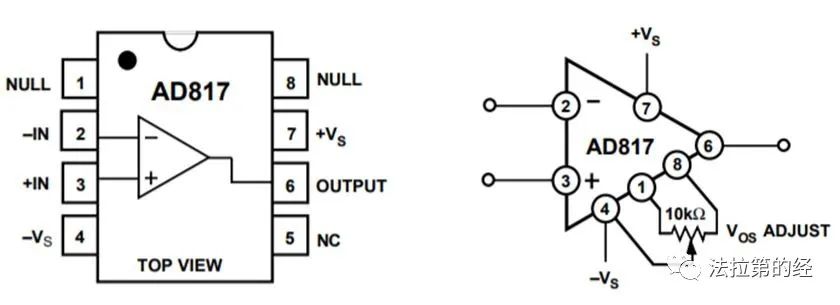

通常有些单集成运放自带Vos校正管脚,如AD817。我们可以通过在pin1和pin8之间接一个10k电位器,电位器滑头接至-Vs,通过这种方式可以获得±15mV的Vos补偿范围。

图5 AD817补偿Vos

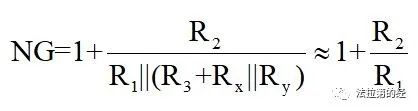

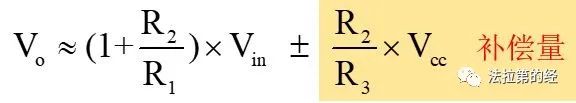

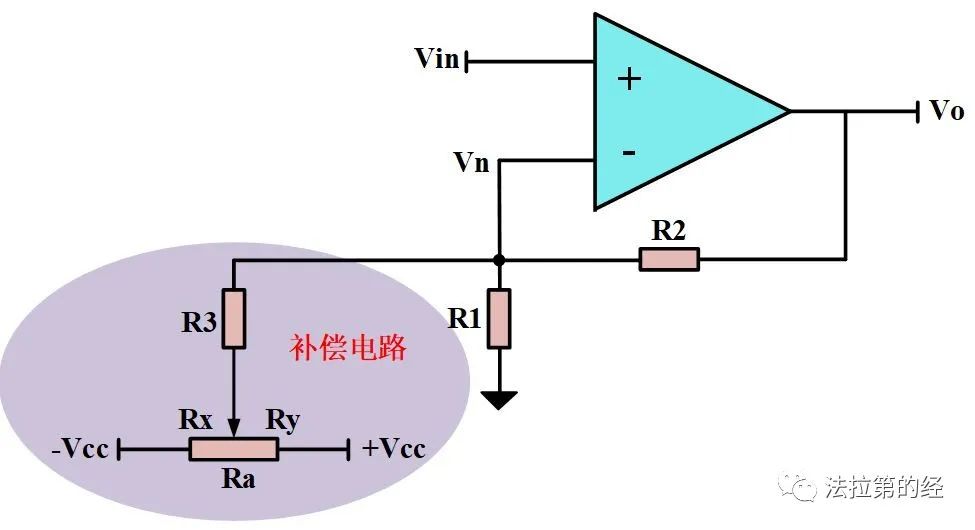

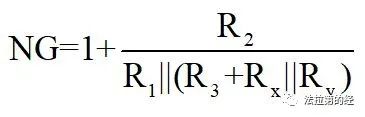

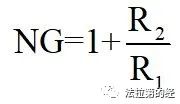

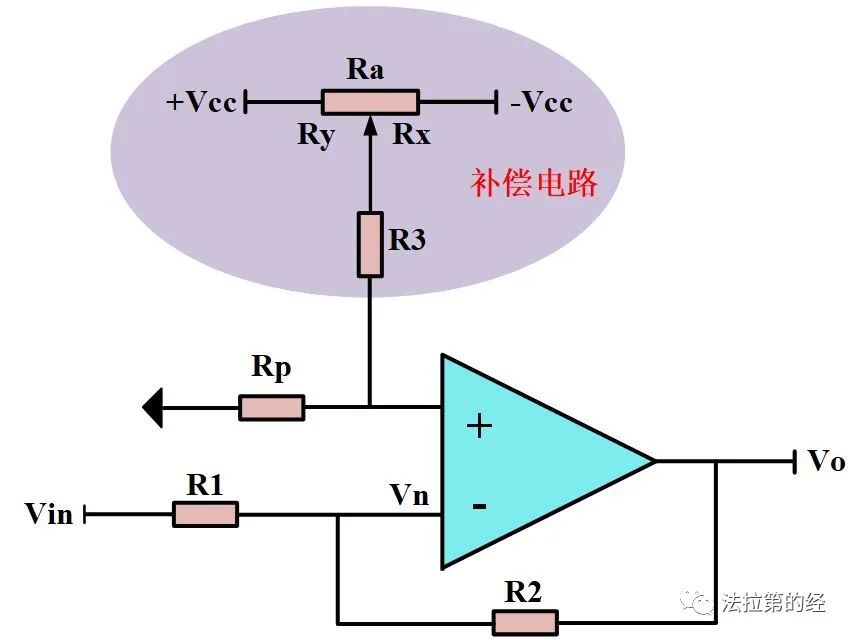

对于那些没有Vos补偿管脚的运放我们需要构建相应的Vos补偿电路。当运放输入信号从同相端输入时,可以采用图6所示补偿电路。紫色区域为引入的补偿电路。其中Ra为电位器,该电路的噪声增益为

为避免补偿电路引入不必要的噪声需要R3远大于R1以保证NG几乎不变。而Vo表达式为

图6 同向端输入时Vos补偿

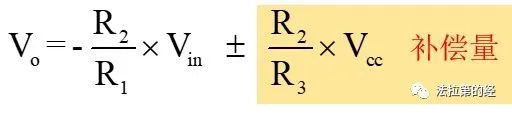

当运放输入信号从反相端输入时存在两种Vos补偿电路。第一种如图7所示。此种方法将Vos补偿电压接入到运放反向端进行补偿,此时电路的噪声增益为

而信号增益为

该种电路的缺点为噪声增益NG较未补偿电路增大,这是因为补偿电路与R1并联导致。为尽可能保持NG不变需要使R3远大于R1||R2。

图7 反向端输入时Vos补偿方法1

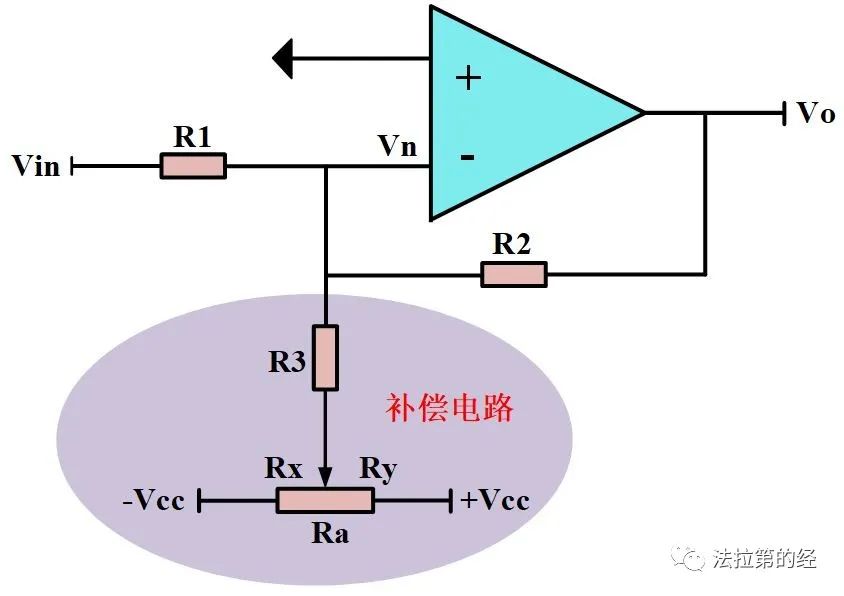

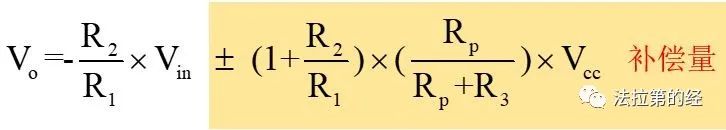

为避免补偿电路对噪声增益的影响可采用图8所示电路,此电路可保证噪声增益NG与未引入补偿电路的NG相同,为

而信号增益为

若选取的运放同向端与反向端偏置电流一致性很好(Ib+≈Ib-),则Rp= R1||R2,若运放偏置电流一致性较差(Ib+≠Ib-)则Rp取值往往小于50Ω,若Rp不得不选取较大值时可以并联一颗小电容以滤除高频噪声。

图8 反向端输入时Vos补偿方法2

OK,关于运放失调电压的几点问题今天就和大家分享到这里,喜欢笔者的读者请点击下方公众号名片关注笔者,您的关注与支持将转换为笔者前进的动力,小生将在后续的推送中不断送出更多优质内容,关注后还可加入技术交流群与各路大神共同探讨进步。

本人能力有限,若文中存在不合理之处欢迎指正。

-

jf_48021068

2024-11-25

0 回复 举报调节反馈电路时需要把输入端接地吗?是在开环状态下调节吗,需不需要去掉反馈电阻? 收起回复

jf_48021068

2024-11-25

0 回复 举报调节反馈电路时需要把输入端接地吗?是在开环状态下调节吗,需不需要去掉反馈电阻? 收起回复

-

直流参数:输入失调电压(VOS)2024-08-27 631

-

运放输入失调电压的结构和原理2024-08-23 2981

-

失调电压Vos定义 各类运放失调电压范围 失调电压产生原因2023-11-06 4785

-

什么是输入失调电压Vos?Vos对电源的影响?2023-10-29 3057

-

详解运放的失调电压Vos2023-09-28 4170

-

运放失调电压如何消除2023-09-22 7363

-

失调电压Vos的理解和仿真实验2023-08-15 3652

-

运放输入失调电压(Vos)和温漂(ΔVos/ΔT)2023-06-06 3701

-

运放的失调电压Vos的理解与仿真验证2023-02-01 7123

-

输入失调电压Vos及温漂2019-07-04 8569

-

运放失调电压自动补偿设计与实现2017-11-29 18390

-

集成运放输入失调电压VIO的测试2011-09-10 4184

-

运放的失调电压是什么?2009-04-22 9311

全部0条评论

快来发表一下你的评论吧 !